Xilinx FPGA上的快速JESD204B接口实现

"文章介绍了如何在Xilinx FPGA上快速实现JESD204B接口,探讨了JESD204B协议的四个关键层,包括传输层、加扰层、数据链路层和物理层,并提供了ADI公司的JESD204B发送器和接收器的实现示例。此外,还提到了Xilinx FPGA中的SERDES收发器在实现JESD204B链路中的作用。"

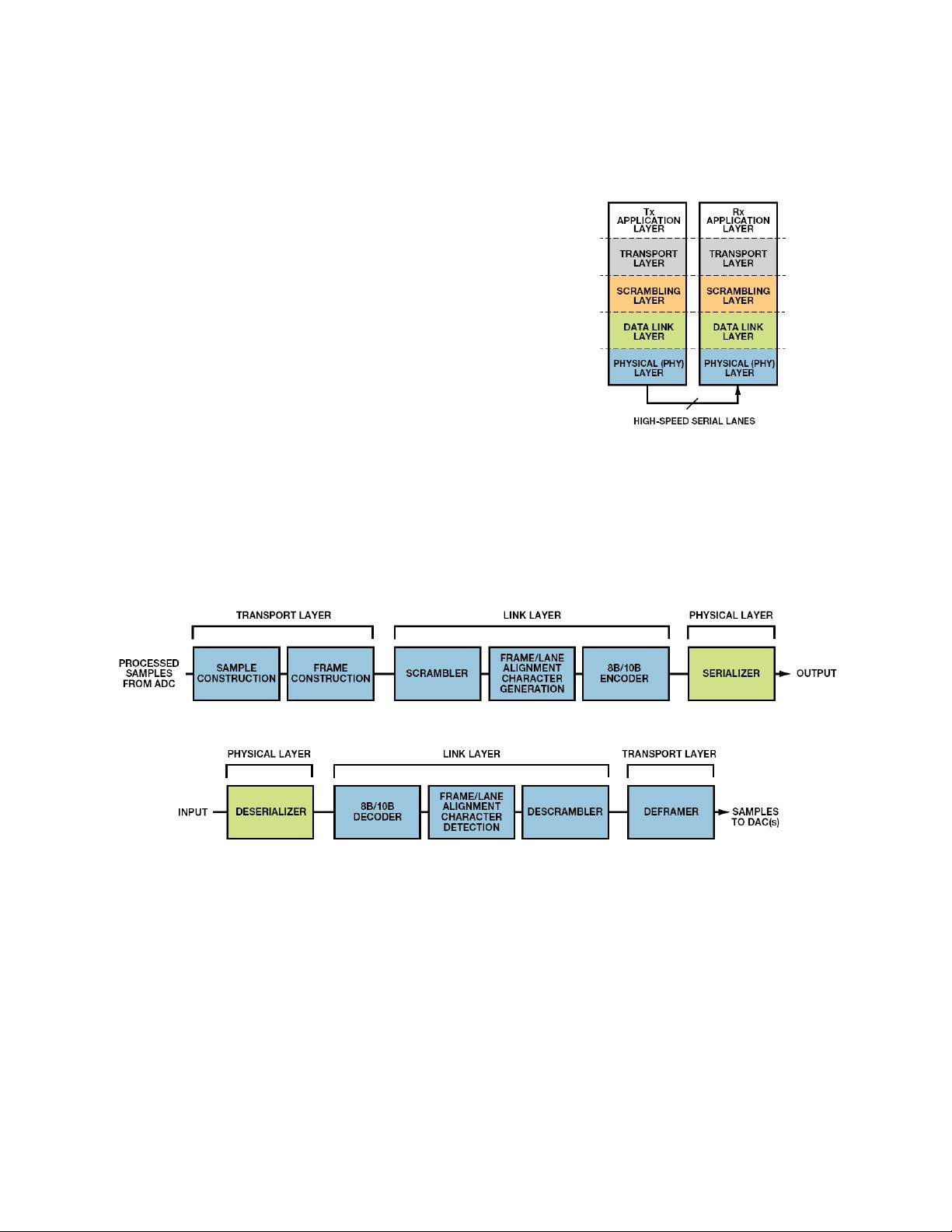

JESD204B是一种高速串行接口标准,主要用于连接高速数据转换器(如ADC和DAC)与逻辑设备,尤其在高速转换器和集成RF收发器中广泛应用。JESD204B的B修订版支持高达12.5Gbps的数据速率,并通过确保可重复的确定性延迟来优化链路性能。随着技术的发展,FPGA和ASIC中的SERDES设计逐渐取代传统的并行接口,成为实现JESD204B物理层的首选。

协议实现分为四个层次:

1. **传输层**:这一层负责样本到帧数据的映射和反向操作,但通常不包含在FPGA供应商的JESD204B IP内,因为它与特定转换器的配置密切相关。

2. **加扰层**(可选):用于加扰和解扰8位字,减少电磁干扰(EMI)。

3. **数据链路层**:管理链路的同步、建立和保持,使用8B10B编码或译码处理加扰后的数据,确保数据在传输过程中的正确性。

4. **物理层**:处理编码后的比特数据,负责高速串行数据的实际发送和接收。

ADI公司的JESD204B发送器和接收器实现分别展示了这四个层次的工作流程。发送器中,传输层和加扰层的实现与转换器配置紧密相关,而链路层逻辑和物理层(通过8B10B编码器和GTP/GTX/GTH Gbps收发器实现)则位于接收器中。

在Xilinx FPGA中,JESD204B链路的构建依赖于可配置的SERDES收发器,它们不仅可以支持JESD204B,还能兼容其他串行协议,如PCIe、SATA、SRIO和CPRI等。发送器和接收器通道实现了加扰和链路层功能,而8B/10B编码/解码器和物理层功能集成在GTP/GTX/GTH Gbps收发器中。

实现JESD204B接口时,设计人员应考虑以下几点:

1. 理解转换器的配置需求,确保与传输层的正确映射。

2. 考虑是否需要加扰层以降低EMI。

3. 正确设置数据链路层,包括同步和错误检测机制。

4. 优化物理层参数,确保信号质量和高速数据传输的稳定性。

5. 利用Xilinx提供的开发工具和IP核进行设计和验证。

快速实现JESD204B接口涉及多个步骤,包括协议理解、硬件资源配置和软件编程。设计者需具备扎实的数字通信理论基础,熟悉FPGA架构以及高速串行接口的设计实践,才能成功地在Xilinx FPGA上部署JESD204B接口。

302 浏览量

378 浏览量

378 浏览量

940 浏览量

812 浏览量

940 浏览量

812 浏览量

stayoyo

- 粉丝: 8

- 资源: 8

最新资源

- 自动抄表系统中几种传感器的应用

- Vxworks入门实验

- Spring框架的简要分析.doc

- Operating System(Chapter 1)

- RDP协议详解(remote desktop protocol)

- Resin_brochure

- eclipse中文文档

- ASP.NET 不仅仅是 Active Server Page (ASP) 的下一个版本;它还提供了一个

- C#和.Net的优点研究了一下C#和.Net,有很多体会,好的不好的都有。随便谈谈,供大家参考。

- 深入理解计算机系统(英文版)

- Practical UML Statecharts in C,C++, Second Edition.pdf

- JSP 实用教程 (第二版) 代码

- 经典c程序编程100例

- 常用DIV+CSS网页制作布局技术技巧

- scilab 软件的帮助说明

- PowerPCB教程.pdf