Xilinx FPGA上的JESD204B协议高速实现与总结

需积分: 0 55 浏览量

更新于2024-06-26

5

收藏 2.26MB PDF 举报

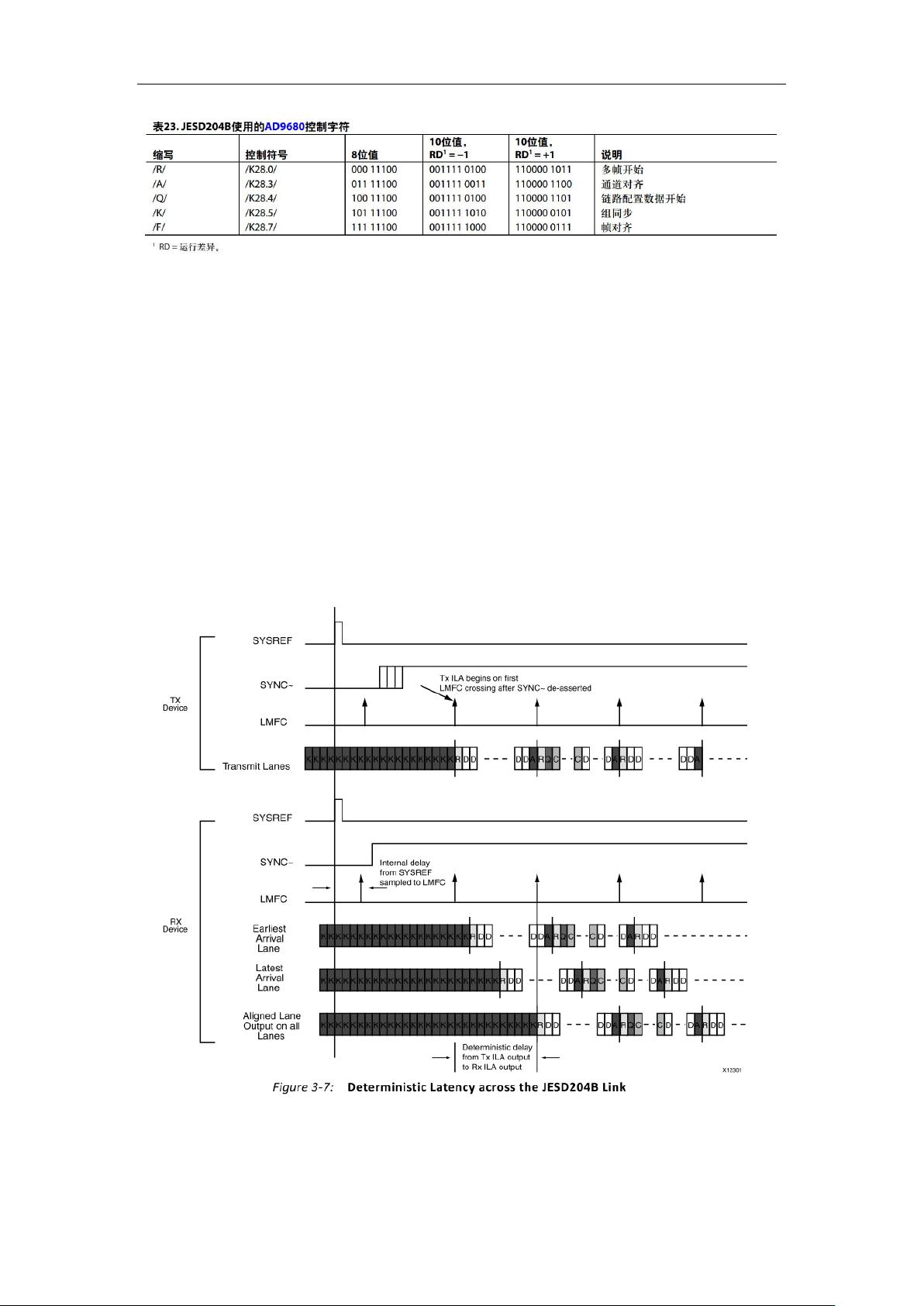

"基于Xilinx FPGA的JESD204B协议实现学习总结详细探讨了高速接口串行通信在现代电子系统中的重要性,尤其是在高数据传输速率要求下,如1Gbps乃至12.5Gbps。JESD204B协议是由JEDEC委员会制定的一种标准化接口,旨在通过减少数据转换器与FPGA之间的连接,简化系统设计,提高信号完整性并支持多通道数据传输,特别是在高性能ADC和DAC应用中。

文章首先介绍了JESD204B协议的背景,它针对高速数据传输的挑战,提供了高效的解决方案。该协议支持Class 1,这是最常见的子类,因为它能够实现超高的时钟速率和多设备间的同步。Class 1协议特别适合处理高采样率的ADC/DAC场景,比如1Gbps以上,传统的接口技术如CMOS和LVDS无法满足这样的速度需求。

此外,文章还提到JESD204B中的缩写和术语,例如M-204B中的M表示接口中转换器的数量,可能包括虚拟转换器。例如,当使用数字信号处理技术(如数字混频器DDC)时,会涉及IQ通道的复数运算,这会导致M值翻倍。理解这些缩写对于正确设计和实现基于FPGA的JESD204B接口至关重要。

作者在学习过程中,不仅研究了协议本身,还深入分析了Xilinx 7系GT口的底层结构,这部分内容涵盖了接口硬件设计的关键要素,如时钟管理、数据编码和解码、以及如何在FPGA中实现信号的同步和延迟补偿。这对于实际项目中的FPGA开发来说是极其实用的知识。

本文的学习总结提供了宝贵的实践经验和理论基础,对从事FPGA开发、高速接口设计以及ADC/DAC系统集成的工程师具有很高的参考价值。通过阅读这篇文章,读者可以了解到如何在Vivado工具中有效地利用Xilinx FPGA来实现JESD204B协议,从而构建高效、小型化的高速数据传输系统。"

1265 浏览量

165 浏览量

940 浏览量

1678 浏览量

1265 浏览量

527 浏览量

cdsn_hk

- 粉丝: 0

- 资源: 1

最新资源

- 自动抄表系统中几种传感器的应用

- Vxworks入门实验

- Spring框架的简要分析.doc

- Operating System(Chapter 1)

- RDP协议详解(remote desktop protocol)

- Resin_brochure

- eclipse中文文档

- ASP.NET 不仅仅是 Active Server Page (ASP) 的下一个版本;它还提供了一个

- C#和.Net的优点研究了一下C#和.Net,有很多体会,好的不好的都有。随便谈谈,供大家参考。

- 深入理解计算机系统(英文版)

- Practical UML Statecharts in C,C++, Second Edition.pdf

- JSP 实用教程 (第二版) 代码

- 经典c程序编程100例

- 常用DIV+CSS网页制作布局技术技巧

- scilab 软件的帮助说明

- PowerPCB教程.pdf