借助EDA工具提升SoC测试效率与质量

2 浏览量

更新于2024-08-30

收藏 169KB PDF 举报

"EDA/PLD中的利用EDA工具提高系统级芯片测试的效率"

在现代电子设计自动化(EDA)和可编程逻辑器件(PLD)领域,优化系统级芯片(SoC)测试效率至关重要。面对日益复杂的SoC设计,高可靠性、高质量、低成本以及快速上市时间的要求,可测性设计(Design for Testability, DFT)成为了解决这些问题的关键策略。可测性设计的目标是通过增强芯片的测试能力,确保在生产过程中能够有效检测和隔离潜在的故障,从而提高产品质量。

EDA工具在可测性设计中扮演了核心角色。它们提供了自动化流程,帮助设计师实现诸如边界扫描、多电压测试、压缩测试和内置自测试(BIST)等技术。这些技术不仅可以减少手动设计和验证的工作量,还能生成更有效的测试向量,提高测试覆盖率,确保更全面地检测出芯片中的缺陷。此外,使用EDA工具还可以显著降低测试成本,因为它们能高效地生成和执行测试方案,减少了测试时间,同时简化了故障诊断过程。

半导体工艺的快速发展,如摩尔定律所示,导致芯片尺寸不断缩小,集成度不断提高。然而,这也带来了新的挑战,如工艺缺陷和不稳定性导致的各种失效。传统的方法依赖于功能仿真向量来验证芯片功能,但这种方法在亚微米和深亚微米工艺下往往无法提供足够的测试覆盖率,通常只能达到50%至60%左右,无法确保产品的质量。因此,仅仅依赖功能测试向量是不够的。

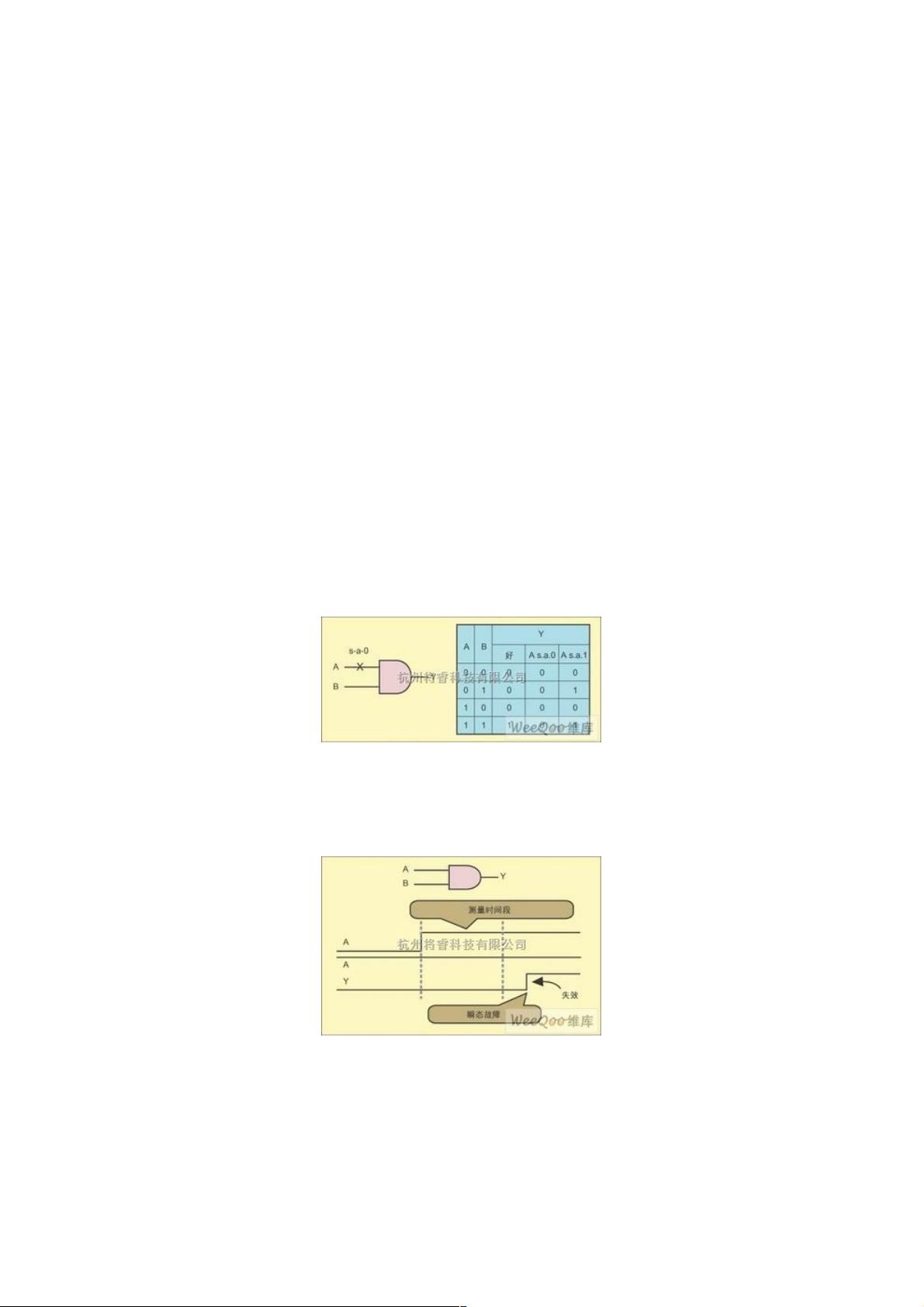

可测试性设计涵盖了广泛的活动,包括但不限于:插入测试逻辑、建立测试访问路径、故障模型分析和测试向量生成。其中,故障模型如“Stuck-at”模型,用于模拟电路中可能出现的故障状态,如信号被固定在“0”或“1”。在深亚微米工艺中,实速测试成为必需,因为它考虑了芯片在实际工作速度下的行为,能更好地暴露高速操作下的潜在问题。

此外,EDA工具还支持高级测试技术,如压缩测试( ATPG, Automatic Test Pattern Generation),它可以通过算法生成最小化的测试向量集,既能达到高测试覆盖率,又能减少测试时间和成本。BIST技术则允许芯片内部生成测试序列,减少了外部测试设备的需求,进一步降低了测试成本并提高了测试效率。

总结来说,利用EDA工具进行可测性设计可以显著提高系统级芯片的测试效率,降低测试成本,保证产品质量,应对半导体行业的快速变化和技术挑战。通过实施先进的测试策略和利用强大的EDA工具,设计师能够有效地应对复杂SoC设计的可靠性、质量和成本问题,同时缩短产品上市的时间。

165 浏览量

114 浏览量

106 浏览量

2020-11-24 上传

2020-12-02 上传

2020-11-09 上传

105 浏览量

140 浏览量

2020-12-09 上传

weixin_38634037

- 粉丝: 7

- 资源: 958

最新资源

- Google+C++编程风格指南.pdf

- red hat linux 命令

- MinGW的使用指南

- 不要害怕指针.pdf

- 安装 Integration Services

- 杜比 AC-3音频编码技术

- 蓝牙联网五子棋对战游戏分析

- Modeling Our World

- Java蓝牙无线通讯技术API

- 单片机开发40实例(汇编跟C相互对照 完整电路图)

- Java In a nutshell

- 信息系统分析与设计课程设计

- RequisitePro使用简介

- The Object Primer 2nd Edition

- SimDriveline User's Guide

- SGH-i728_QSG_CH_Rev.1.0_080321