MEHTA et al. : ON-CHIP RELAXATION OSCILLATOR IN 5-nm FinFET 2907

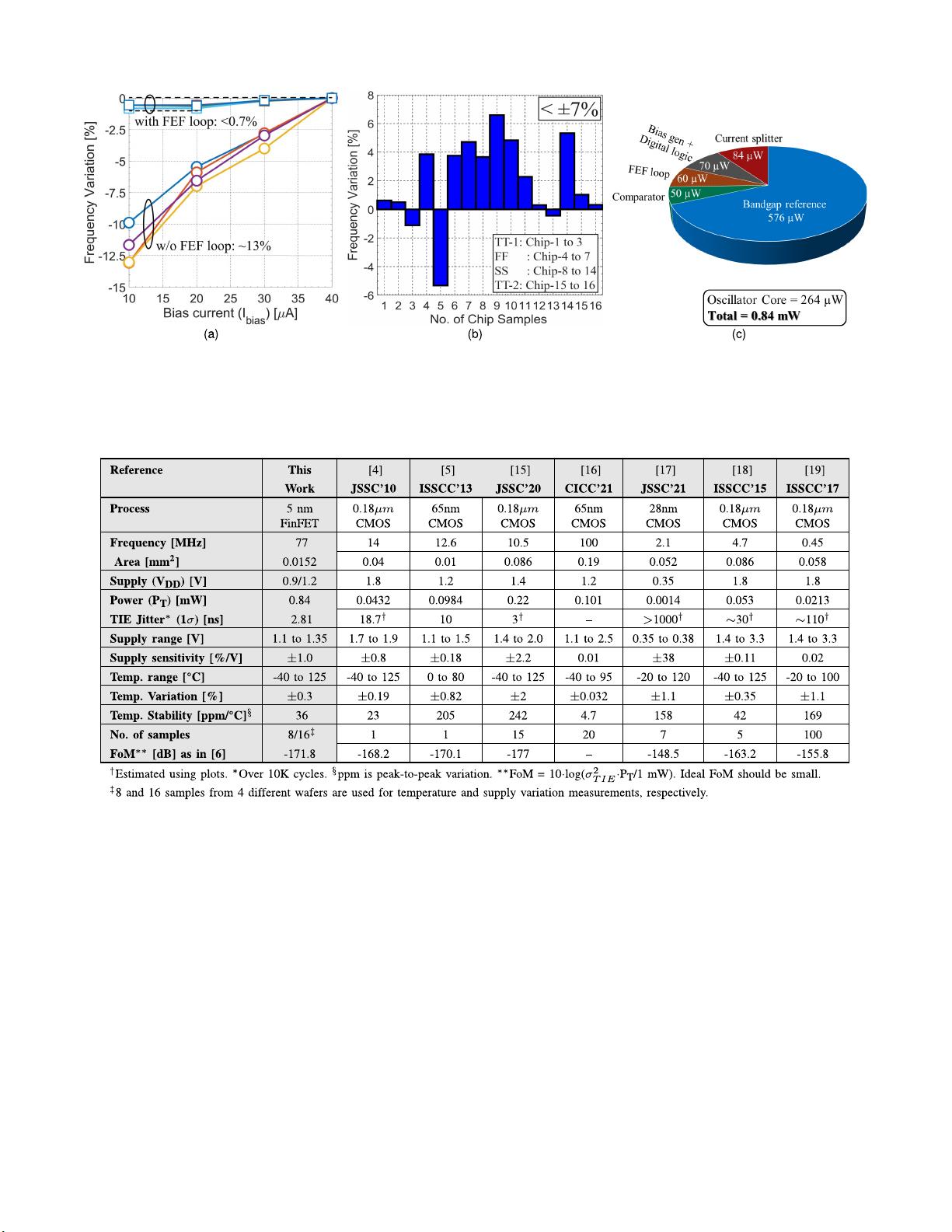

Table I summarizes the performance of the proposed oscil-

lator a nd compares it with previously publishe d state-of-the-art

works. The proposed design operates at 7 7 MHz which is one

of the h ighest among the recently published works. Thanks

to the small feature size of the 5-nm FinFET process, the

proposed oscillator achieves the lowest area even though it

uses a bandgap reference for generating the reference voltage

and reference current sources. Compared with [4], [5], the TIE

jitter is reduced by 3×. While the TIE is comparable to [15],

the thermal stability is 6× better. The frequency variations

with supply and temperature reported in Table I for this design

are the worst case values from 16 and eight chip samples,

respectively.

V. C

ONCLUSION

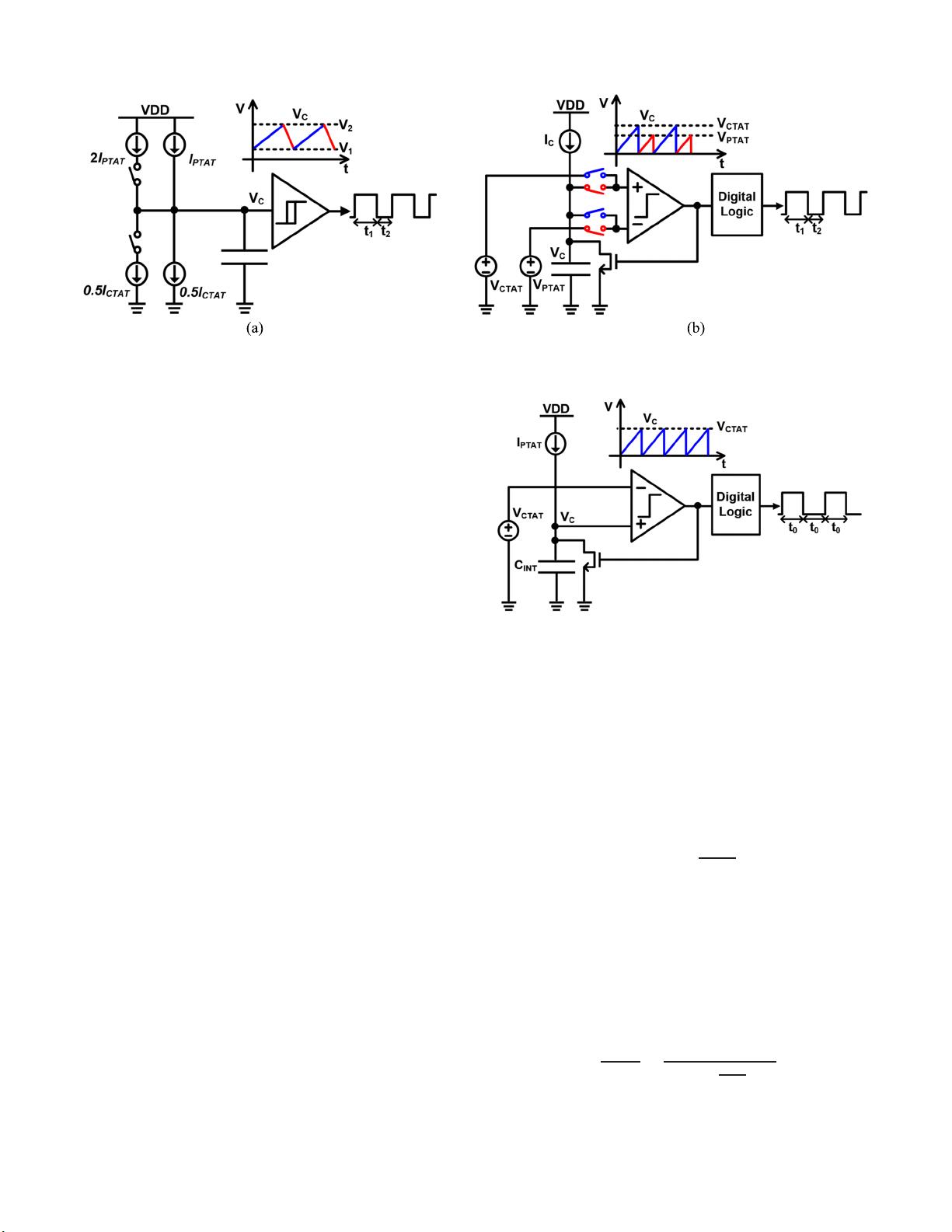

A relaxation oscillator using a FEF loop is describ ed for

securing SoCs against physical clock attacks. From a security

perspective, the

ON-chip oscillator should achieve good sta-

bility with supply and temperature as well as good TIE jitter

and period jitter. The oscillator using an FEF loop is shown to

meet these requirements using circuit techniques such as CDS-

based error-amplifier, current splitter, and reuse of loop-filter

as a hold capacitor. Realized in 5-nm FinFET, the 77-MHz

oscillator achieves 11-μW/MHz power efficiency and a TIE

of 2.81 ns over 10 K cycles with a period jitter of 60 ps. The

worst case frequency stability over 1 .1–1.35-V supply and the

temperature range of −40

◦

C to 125

◦

Cis±0.25% and ±0.3%,

respectively. This performance combined with the use of no

external components makes the proposed oscillator well-suited

for securing the boot-up process and as a reference for

ON-chip

clock monitors.

A

CKNOWL EDGMENT

The authors thank Brian Zimmer and Sudhir Kudva for

layout help and Neil Pham for equipment support.

R

EFERENCES

[1] C. H. Kim and J.-J. Quisquater, “Faults, injection methods, and fault

attacks,” IEEE Design Test Comput., vol. 24, no. 6, pp. 544–545,

Nov. 2007.

[2] T. I. Wiki. (Jul. 2009). 0x24000 Segment Overflow. Accessed:

Jan. 13, 2022. [Online]. Available: https://www.theiphonewiki.com/

wiki/0x24000_Segment_Overflo w

[3] F. Basse. (Oct. 2016). Amlogic S905 SoC: Bypassing the (not so)

Secure Boot to Dump the BootROM. Accessed: Jan. 13, 2022. [Online].

Av ailable: https://fredericb .info/2016/10/amlogic-s905-soc-bypassing-

not-so.html

[4] Y. Tokunaga, S. Sakiyama, A. Matsumoto, and S. Dosho, “An on-chip

CMOS relaxation oscillator with voltage averaging feedback,” IEEE

J . Solid-State Circuits, vol. 45, no. 6, pp. 1150–1158, Jun. 2010.

[5] Y. Cao, P. Leroux, W. De Cock, and M. Steyaert, “A 63,000 Q-factor

relaxation oscillator with switched-capacitor integrated error feedback,”

in IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers,

Feb. 2013, pp. 186–187.

[6] K. Pappu, G. P. Reitsma, and S. Bapat, “5.4 frequency-locked-loop ring

oscillator with 3 ns peak-to-peak accumulated jitter in 1 ms time window

for high-resolution frequency counting,” in IEEE Int. Solid-State Circuits

Conf. (ISSCC) Dig. Tech. Papers, Feb. 2017, pp. 92–93.

[7] T. T okairin et al., “A 280 nW, 100 kHz, 1-cycle start-up time, on-

chip CMOS relaxation oscillator employing a feedforward period control

scheme,” in Proc. Symp. VLSI Circuits (VLSIC), Jun. 2012, pp. 16–17.

[8] H. Jiang, S. Pan, C. Gurleyuk, and K. A. A. Makinwa, “A 0.14 mm

2

16 MHz CMOS RC frequency reference with a 1-point trimmed inac-

curacy of ±400 ppm from −45

◦

Cto85

◦

C,” in IEEE Int. Solid-State

Circuits Conf. (ISSCC) Dig. Tech. Papers, Feb. 2021, pp. 436–438.

[9] K. Lasanen, E. Raisanen-Ruotsalainen, and J. Kostamovaara, “A 1-V,

self adjusting, 5-MHz CMOS RC-oscillator ,” in Proc. IEEE Int. Symp.

Circuits Syst., vol. 4, May 2002, p. 4.

[10] N. Mehta, S. Tell, W. Turner, L. Tatro, G. Goh, and C. T. Gray,

“A 77 MHz relaxation oscillator in 5nm FinFET with 3 ns TIE ov e r

10 K cycles and ±0.3% thermal stability using frequency-error feed-

back loop,” in Proc. IEEE Asian Solid-State Circuits Conf. (A-SSCC),

Nov. 2021, pp. 1–3.

[11] U. Denier, “Analysis and design of an ultralow-power CMOS relaxation

oscillator ,” IEEE Trans. Circuits Syst. I, Reg . Papers, vol. 57, no. 8,

pp. 1973–1982, Aug. 2010.

[12] C. C. Enz and G. C. Temes, “Circuit techniques for reducing the effects

of op-amp imperfections: Autozeroing, correlated double sampling, and

chopper stabilization,” Proc. IEEE, vol. 84, no. 11, pp. 1584–1614,

Nov. 1996.

[13] D. Griffith, P. T. Røine, J. Murdock, and R. Smith, “A 190 nW 33 kHz

RC oscillator with ±0.21% temperature stability and 4 ppm long-term

stability,” in IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech.

Papers, Feb. 2014, pp. 300–301.

[14] J. Jung, I.-H. Kim, S.-J. Kim, Y. Lee, and J.-H. Chun, “A 1.08-nW/kHz

13.2-ppm/

◦

C self-biased timer using temperature-insensitive resistive

current,” IEEE J. Solid-State Circuits, vol. 53, no. 8, pp. 2311–2318,

Aug. 2018.

[15] J. Lee, A. K. George, and M. Je, “An ultra-low-noise swing-boosted

differential relaxation oscillator in 0.18-μmCMOS,”IEEE J. Solid-State

Circuits, vol. 55, no. 9, pp. 2489–2497, Sep. 2020.

[16] K.-S. Park et al., “A second-order temperature compensated 1μW/MHz

100 MHz RC oscillator with ±140 ppm inaccuracy from −40

◦

Cto

95

◦

C,” in Proc. IEEE Custom Integr. Circuits Conf. (CICC), Apr. 2021,

pp. 1–2.

[17] K.-M. Lei, P.-I. Mak, and R. P. Martins, “A 0.35-V 5,200-μm

2

2.1-MHz

temperature-resilient relaxation oscillator with 667 fJ/cycle energy effi-

ciency using an asymmetric swing-boosted RC network and a dual-path

comparator,” IEEE J. Solid-State Circuits, vol. 56, no. 9, pp. 2701–2710,

Sep. 2021.

[18] J. Lee, P. Park, S. Cho, and M. Je, “A 4.7 MHz 53 μW fully differential

CMOS reference clock oscillator with −22 dB worst-case PSNR for

miniaturized SoCs,” in IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig.

Tech. Papers, Feb. 2015, pp. 1–3.

[19] J. Koo, K.-S. Moon, B. Kim, H.-J. Park, and J.-Y. Sim,

“5.5 A quadrature relaxation oscillator with a process-induced

frequency-error compensation loop,” in IEEE Int. Solid-State Circuits

Conf. (ISSCC) Dig. Tech. Papers, Feb. 2017, pp. 94–95.

[20] A. L. S. Loke et al., “Analog/mixed-signal design challenges in

7-nm CMOS and beyond,” in Proc. IEEE Custom Integr. Circuits Conf.

(CICC), Apr. 2018, pp. 1–8.

Nandish Mehta (Senior Member, IEEE) received

the M.Sc. degree in microelectronics from the Delft

Uni versity of T echnology, Delft, The Netherlands,

in 2013, and the Ph.D. degree in electrical engi-

neering and computer science from the University of

California at Berkeley, Berkeley, CA, USA, in 2019.

He held internships with Apple Inc., Cupertino,

CA, USA; Ayar labs, Emeryville, CA, USA; and

Broadcom Inc., Bunnik, The Netherlands. He is

currently with Nvidia Corporation, Santa Clara, CA,

USA. His research focuses on applications of inte-

grated silicon photonics, analog-mixed signal circuits, and serial links.

Dr. Mehta was a recipient of the Foundation for Excellence Scholarship

in 2005, the Intel Scholarship in 2008, the NXP Scholarship in 2011, the

Department of EECS Fellowship in 2014, the ADI Outstanding Student

Designer Award in 2018, and the IEEE SSCS Predoctoral Award in 2019.