QuartusII中使用IP核创建双端口RAM教程

需积分: 24 20 浏览量

更新于2024-07-24

收藏 1.07MB PDF 举报

"这篇教程是关于如何在Quartus II软件中使用IP核来设计自定义的双端口RAM。适合初学者了解Quartus II的项目创建、IP核选择及RAM配置流程。"

在Quartus II这个强大的FPGA开发环境中,利用IP核进行设计可以大大提高开发效率和准确性。本教程将详细介绍如何使用Quartus II中的IP核生成器,特别是针对自定义双端口RAM的创建步骤。

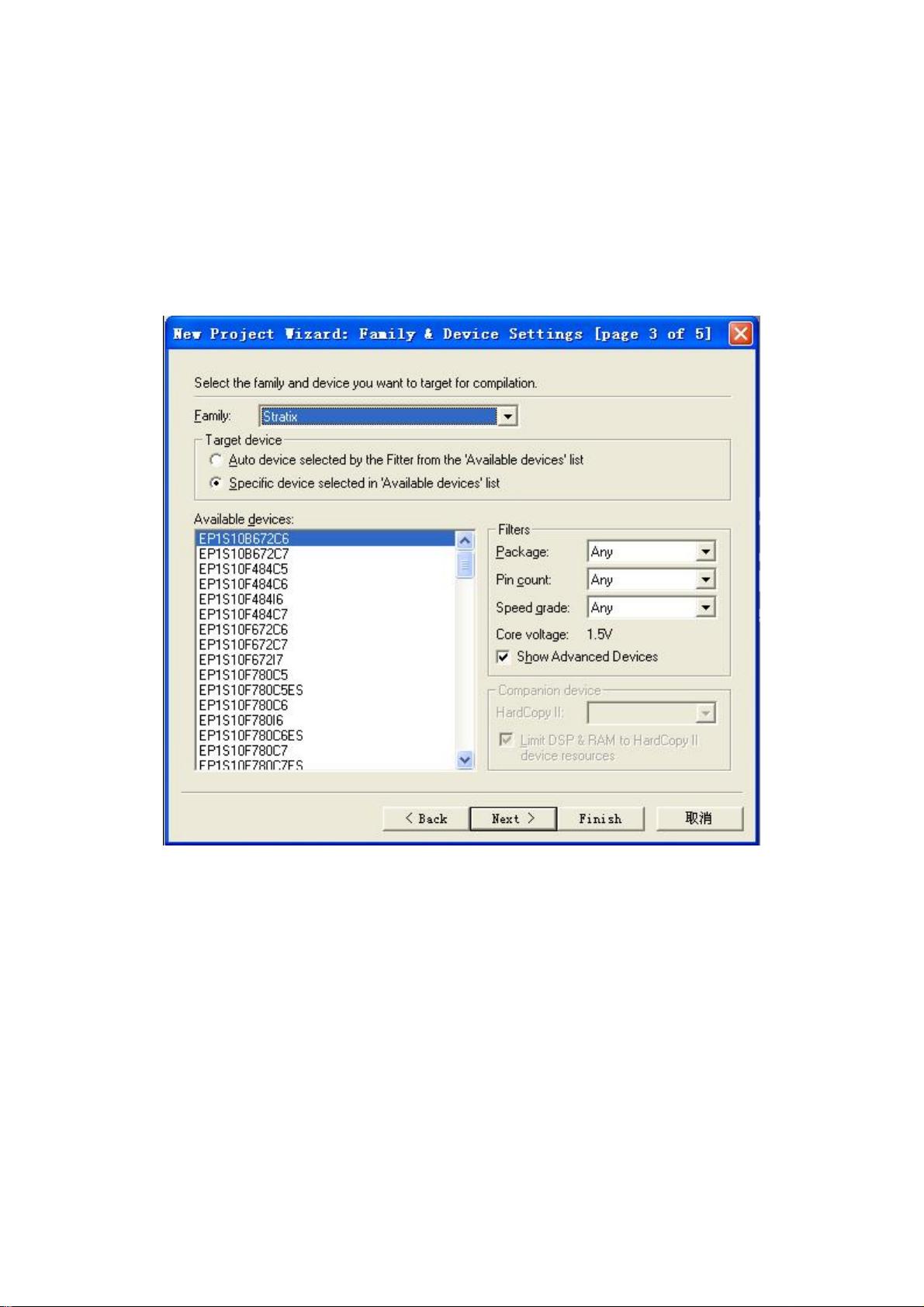

首先,打开Quartus II并启动新项目。在创建项目时,你需要指定工程存放目录、工程名和顶层文件名。接下来,选择适用的FPGA器件类型,这将决定你的设计能够运行在哪种硬件平台上。

进入关键步骤,通过Tools—MegaWizard Plug-In Manager启动IP核创建向导。这里我们选择“memory compiler—RAM:2-PORT”,即创建一个双端口RAM。设置输出文件名为myram2,以便后续引用。

接着,定义RAM的基本属性。如RAM的读写端口数量,内存大小(例如,本例中设置为16个存储单元),以及输入数据的宽度(4位)。这决定了RAM能同时处理的数据量和存储容量。

然后,设置读写时钟,这关乎到数据的存取速度。在某些应用中,你可能还需要定义输出锁存,确保数据在时钟边沿稳定。如果需要初始化RAM的内容,可以在相应步骤进行设置。

完成这些配置后,IP核生成器会自动生成对应的硬件描述语言(HDL)代码和原理图。在原理图中,可以直观地看到RAM的输入输出端口,确保正确命名总线以避免混淆。

保存原理图作为顶层文件,进行全编译。编译完成后,Quartus II会在顶层文件下显示实例化的myram2,表明RAM已经成功集成到设计中。

为了验证设计的功能,我们需要创建仿真波形文件。通过File--New—Other Files—Vector Waveform File启动波形编辑器,选择NodeFinder来定位输入输出信号,并创建对应的波形仿真文件。这样,就能进行时序仿真,通过Simulation Report查看结果,确保RAM在预期的时序条件下工作正常。

总结来说,本教程详述了在Quartus II中使用IP核生成自定义双端口RAM的整个过程,包括项目创建、IP核配置、原理图编辑、编译和仿真,为不熟悉Quartus II的开发者提供了一条清晰的学习路径。通过这个教程,你可以掌握在FPGA设计中运用IP核的基本技能,进一步提升你的设计能力。

2019-08-29 上传

2022-03-31 上传

2022-09-19 上传

2021-01-06 上传

2014-10-11 上传

2024-02-04 上传

点击了解资源详情

2023-05-25 上传

2023-06-03 上传

TIC_YX

- 粉丝: 55

- 资源: 9

最新资源

- SSM Java项目:StudentInfo 数据管理与可视化分析

- pyedgar:Python库简化EDGAR数据交互与文档下载

- Node.js环境下wfdb文件解码与实时数据处理

- phpcms v2.2企业级网站管理系统发布

- 美团饿了么优惠券推广工具-uniapp源码

- 基于红外传感器的会议室实时占用率测量系统

- DenseNet-201预训练模型:图像分类的深度学习工具箱

- Java实现和弦移调工具:Transposer-java

- phpMyFAQ 2.5.1 Beta多国语言版:技术项目源码共享平台

- Python自动化源码实现便捷自动下单功能

- Android天气预报应用:查看多城市详细天气信息

- PHPTML类:简化HTML页面创建的PHP开源工具

- Biovec在蛋白质分析中的应用:预测、结构和可视化

- EfficientNet-b0深度学习工具箱模型在MATLAB中的应用

- 2024年河北省技能大赛数字化设计开发样题解析

- 笔记本USB加湿器:便携式设计解决方案