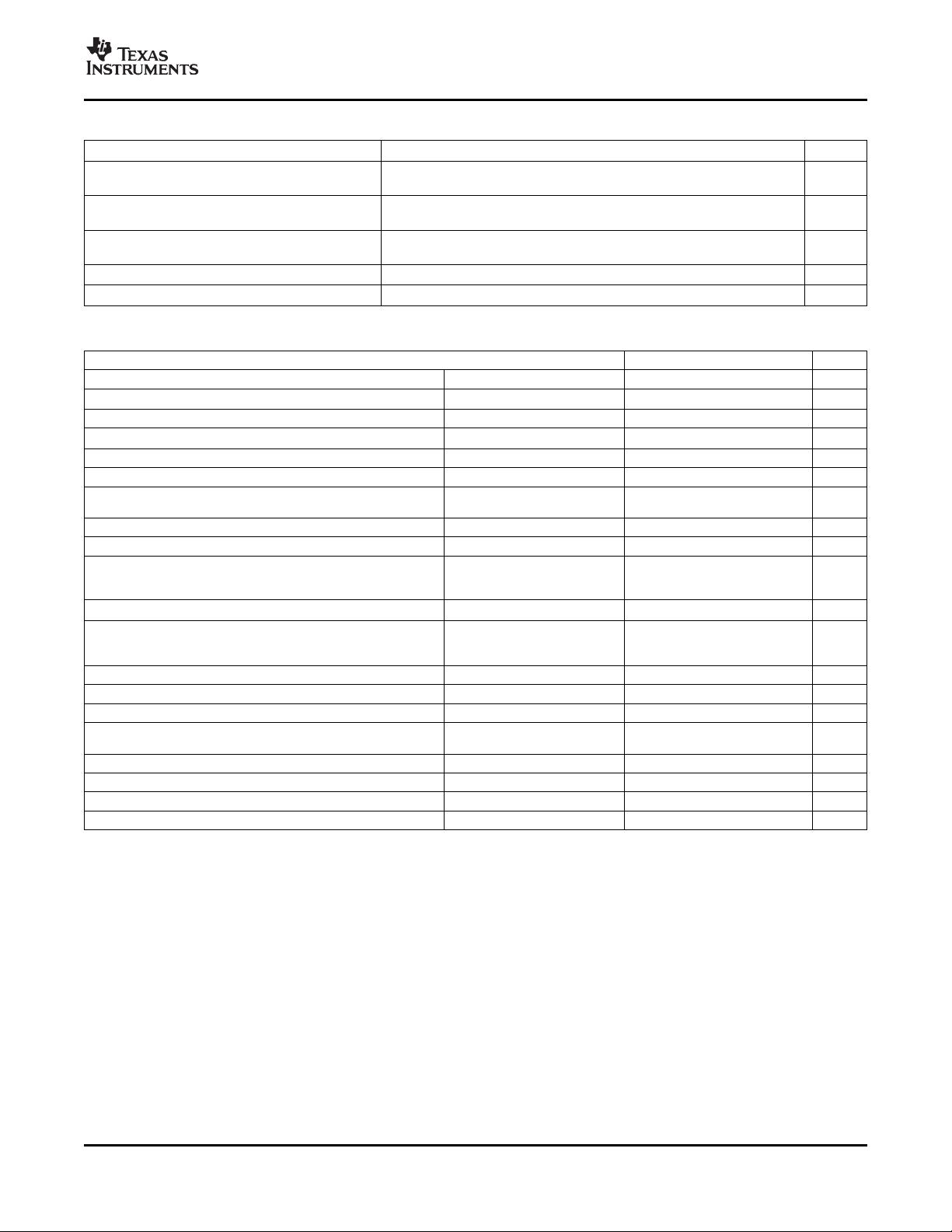

ELECTRICAL CHARACTERISTICS

TAS5414A , TAS5424A

SLOS535A – JULY 2007 – REVISED FEBRUARY 2008

Test conditions (unless otherwise noted): T

Case

= 25 ° C, PVDD = 14.4 V, R

L

= 4 Ω , f

S

= 417 kHz, Rext = 20 k Ω , master mode

operation (see application diagram)

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

OPERATING CURRENT

I

PVDD_IDLE

All four channels running in MUTE mode 240 300

PVDD idle current mA

I

PVDD_Hi-Z

All four channels in Hi-Z mode 80

I

PVDD_STBY

PVDD standby current STANDBY mode, T

J

≤ 85 ° C 2 20 µ A

OUTPUT POWER

4 Ω , PVDD = 14.4 V, THD+N ≤ 1%, 1 kHz, T

c

= 75 ° C 23

4 Ω , PVDD = 14.4 V, THD+N = 10%, 1 kHz, T

c

= 75 ° C 25 28

4 Ω , PVDD = 14.4 V, square wave, 1 kHz, T

c

= 75 ° C 43

4 Ω , PVDD = 21 V, THD+N = 1%, 1 kHz, T

c

= 75 ° C 47

4 Ω , PVDD = 21 V, THD+N = 10%, 1 kHz, T

c

= 75 ° C 50 58

2 Ω , PVDD = 14.4 V, THD+N = 1%, 1 kHz, T

c

= 75 ° C 38

P

OUT

Output power per channel W

2 Ω , PVDD = 14.4 V, THD+N = 10%, 1 kHz, T

c

= 75 ° C 40 45

2 Ω , PVDD = 14.4 V, square wave 1 kHz, T

c

= 75 ° C 70

PBTL 2- Ω operation, PVDD = 21 V, THD+N = 10%,

116

1 kHz, T

c

= 75 ° C

PBTL 1- Ω operation, PVDD = 14.4 V, THD+N = 10%,

90

1 kHz, T

c

= 75 ° C

4 channels operating, 23-W output power/ch, L = 10 µ H,

EFF

P

Power efficiency 90%

T

J

≤ 85 ° C

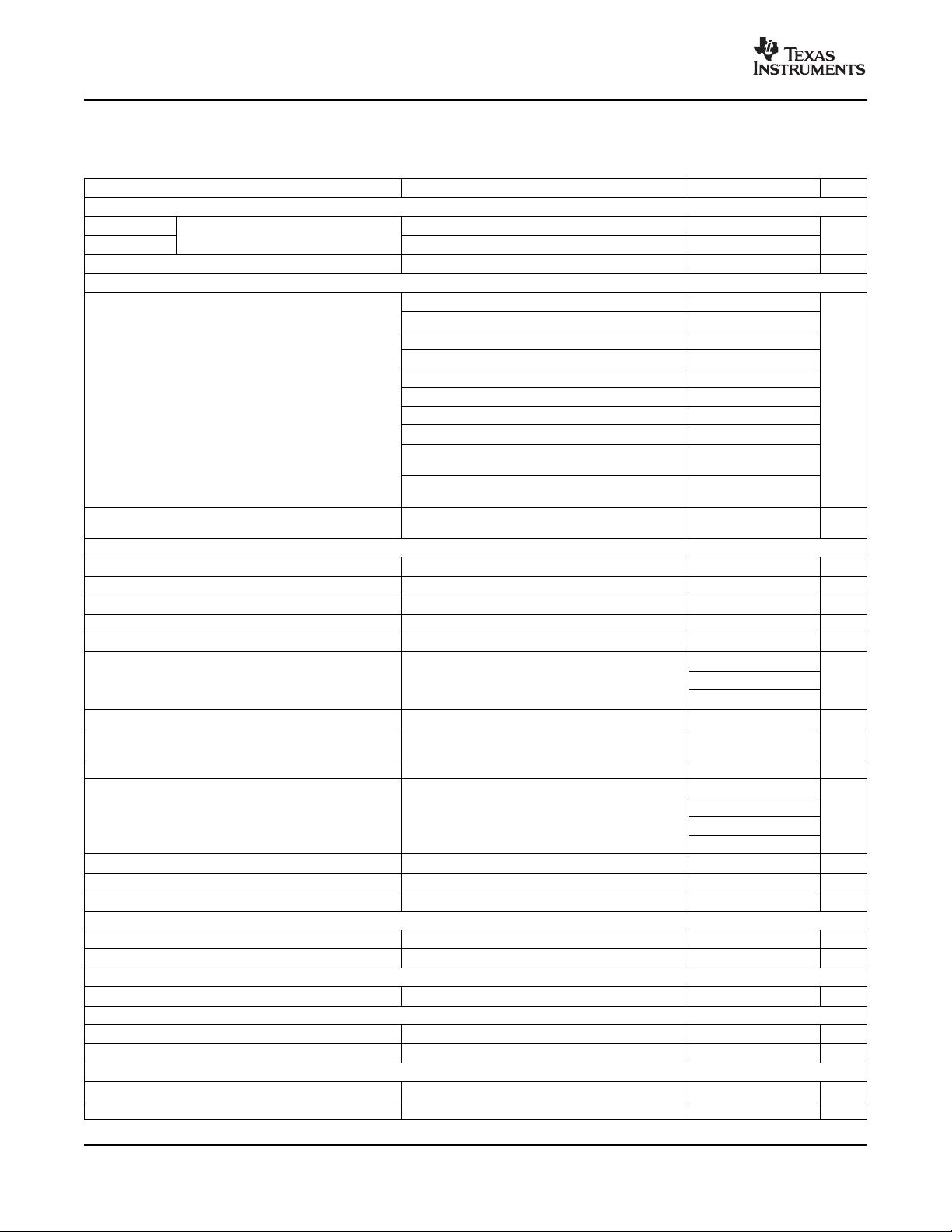

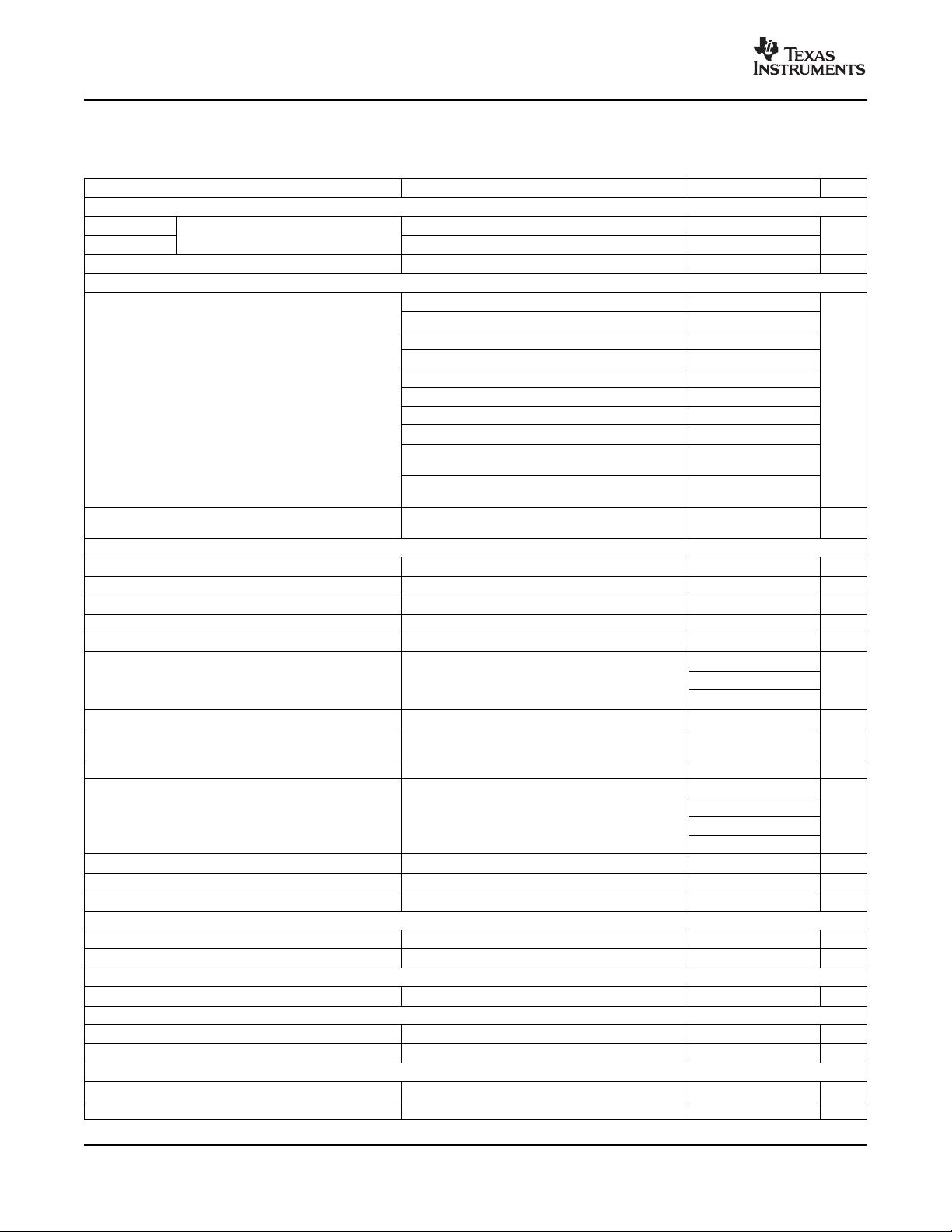

AUDIO PERFORMANCE

V

NOISE

Noise voltage at output G = 26 dB, zero input, AES17 filter, and A-weighting 60 100 µ V

Crosstalk Channel crosstalk 1 W, G = 26 dB, 1 kHz 60 75 dB

CMRR

5424

Common-mode rejection ratio (TAS5424A) 1 kHz, 1 Vrms referenced to SGND, G = 26 dB 60 75 dB

PSRR Power supply rejection ratio G = 26 dB, PVDD = 14.4 Vdc + 1 Vrms, f = 1 kHz 60 75 dB

THD+N Total harmonic distortion + noise P = 1 W, G = 26 dB, f = 1 kHz, 0 ° C ≤ T

J

≤ 75 ° C 0.02% 0.1%

336 357 378

Switching frequency selectable for AM interference

f

S

Switching frequency 392 417 442 kHz

avoidance

470 500 530

R

AIN

Analog input resistance Internal shunt resistance on each input pin 60 80 100 k Ω

AC-coupled common-mode input voltage (zero

V

IN_CM

Common-mode input voltage (non-clipping) 1.3 Vrms

differential input)

V

CM_INT

Internal common-mode input bias voltage Internal bias applied to IN_M pin 3.25 V

11 12 13

19 20 21

G Voltage gain (V

O

/V

IN

) Source impedance = 0 Ω dB

25 26 27

31 32 33

G

CH

Channel-to-channel variation Any gain commanded – 1 0 1 dB

t

CM

Output-voltage common-mode ramping time 35 ms

t

GAIN

Gain ramping time External C

MUTE

= 330 nF 30 ms

PWM OUTPUT STAGE

R

DSon

FET drain-to-source resistance Not including bond wire resistance, T

J

= 25 ° C 75 95 m Ω

V

O_OFFSET

Output offset voltage Zero input signal and G = 26 dB ± 10 ± 25 mV

PVDD OVERVOLTAGE (OV) PROTECTION

V

OV

PVDD overvoltage shutdown 22.1 23.7 26.3 V

LOAD DUMP (LD) PROTECTION

V

LD_SD_SET

Load-dump shutdown voltage 26.6 29 32 V

V

LD_SD_CLEAR

Recovery voltage for load-dump shutdown 23.5 26.4 28.4 V

PVDD UNDERVOLTAGE (UV) PROTECTION

V

UV_SET

PVDD undervoltage shutdown 6.5 7 7.5 V

V

UV_CLEAR

Recovery voltage for PVDD UV 7 7.5 8 V

10 Submit Documentation Feedback Copyright © 2007 – 2008, Texas Instruments Incorporated

Product Folder Link(s): TAS5414A TAS5424A