异步DSP核心:低功耗高性能的未来趋势

55 浏览量

更新于2024-09-04

收藏 179KB PDF 举报

"异步DSP核心设计:更低功耗,更高性能"

在当今的集成电路设计领域,处理器性能的提升往往依赖于更高的时钟频率,这通常是通过同步架构实现的。同步设计利用全局时钟信号同步整个系统,使得数据处理有条不紊地进行,这种方式在业界占据了主导地位。然而,随着摩尔定律的逐渐逼近极限,降低功耗成为了新的挑战。这时,异步设计作为一种能够有效减少功耗并提高性能的技术,开始受到越来越多的关注。

异步设计的核心优势在于其灵活性和效率。它不需要全局时钟,而是依赖于局部的信号来触发操作,这使得电路能够在需要时才工作,从而显著降低了功耗。此外,由于没有全局时钟的约束,异步设计可以更好地适应工艺变化和温度波动,提高了系统的可靠性。在90纳米以下的工艺节点中,这些优势尤其突出,使得异步设计成为解决低功耗问题的有效途径。

尽管异步设计有着诸多优点,但在过去,其发展受到了标准化工具流缺失的限制。传统的IC设计流程依赖于同步设计的高级编程语言和事件驱动的EDA工具,这使得异步设计的实施变得更加复杂。然而,随着技术的进步,现在已经有更多的工具开始支持异步设计,使得设计师可以更容易地探索这一领域。

异步设计并不意味着完全抛弃同步设计。在许多应用中,异步电路常作为同步电路的补充,特别是在那些对功耗极度敏感的场合,如嵌入式传感器。这些设备需要在保持低功耗的同时,保证稳定的电流供给和高可靠性。近年来,完全基于异步逻辑的通用DSP核心开始崭露头角,它的出现为IC设计人员和最终用户带来了全新的机遇。

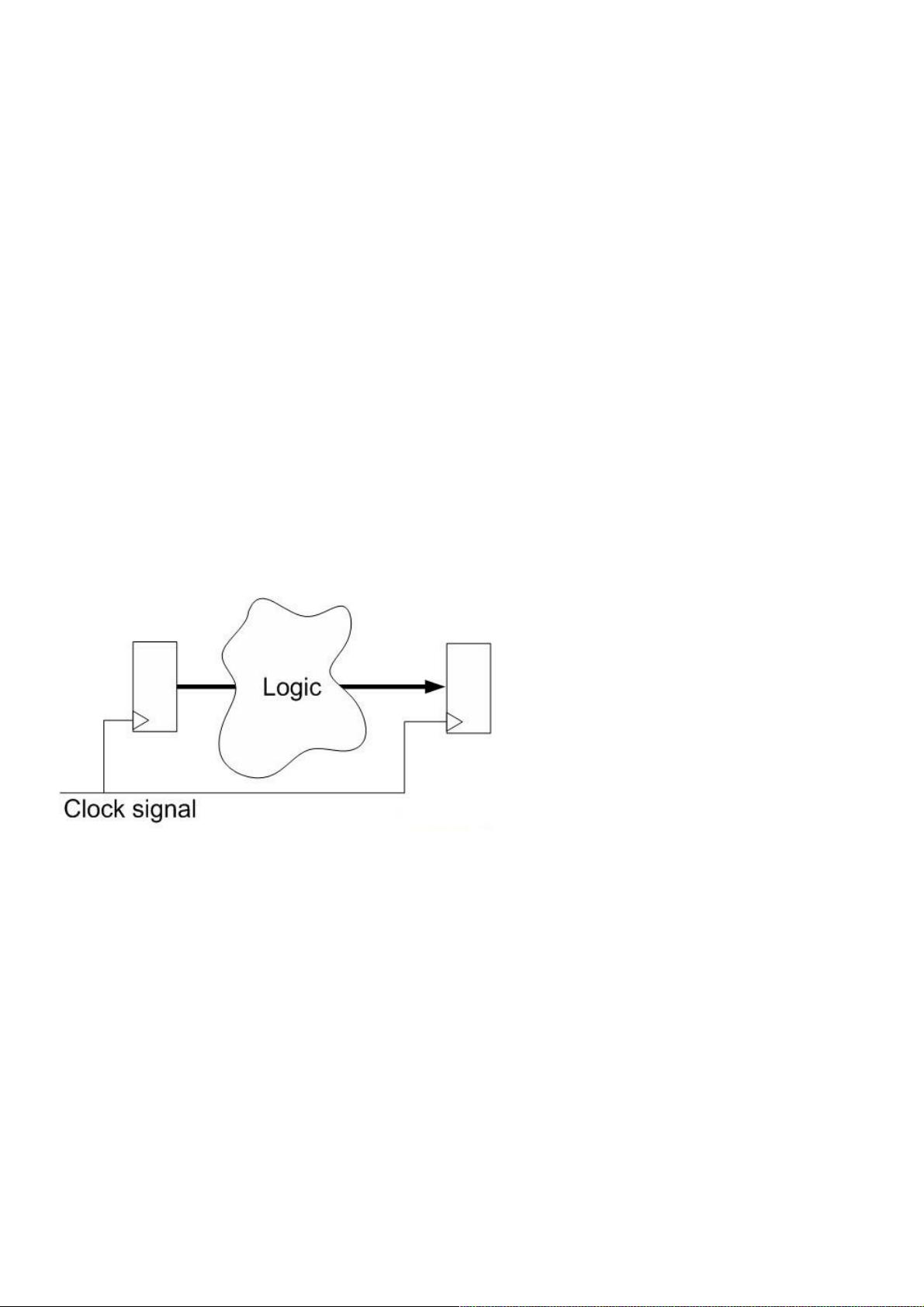

同步和异步设计之间的区别在于控制机制。同步设计中的每个功能模块由一个时钟信号控制的状态机驱动,而异步设计则取消了这种全局控制,转而采用局部的“完成”信号来触发下一阶段的逻辑操作。这种去时钟化的设计允许每个逻辑阶段独立工作,只有当前一阶段的计算完成时,才会向下一阶段发送信号,从而减少了不必要的等待时间和功耗。

在异步DSP核心中,逻辑阶段不再受全局时钟的约束,而是通过本地的控制逻辑来决定何时进行计算和何时传递结果。这样的设计可以实现更加精细的控制,允许电路根据具体任务的需求动态调整其运行速度,进一步优化了性能和能效。

异步DSP核心设计为低功耗和高性能提供了新的可能。随着工具链的完善和设计方法的成熟,异步设计有望在未来的集成电路领域发挥更大的作用,尤其是在那些对功耗和性能要求苛刻的应用中。设计师们正在积极探索这种技术,以期在未来的半导体行业中开辟新的道路。

2020-10-19 上传

2020-08-09 上传

点击了解资源详情

2020-11-02 上传

点击了解资源详情

2020-10-16 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

weixin_38739950

- 粉丝: 8

- 资源: 918

最新资源

- SSM动力电池数据管理系统源码及数据库详解

- R语言桑基图绘制与SCI图输入文件代码分析

- Linux下Sakagari Hurricane翻译工作:cpktools的使用教程

- prettybench: 让 Go 基准测试结果更易读

- Python官方文档查询库,提升开发效率与时间节约

- 基于Django的Python就业系统毕设源码

- 高并发下的SpringBoot与Nginx+Redis会话共享解决方案

- 构建问答游戏:Node.js与Express.js实战教程

- MATLAB在旅行商问题中的应用与优化方法研究

- OMAPL138 DSP平台UPP接口编程实践

- 杰克逊维尔非营利地基工程的VMS项目介绍

- 宠物猫企业网站模板PHP源码下载

- 52简易计算器源码解析与下载指南

- 探索Node.js v6.2.1 - 事件驱动的高性能Web服务器环境

- 找回WinSCP密码的神器:winscppasswd工具介绍

- xctools:解析Xcode命令行工具输出的Ruby库