TI-TLV5580:高性能8位80MSPS模数转换器

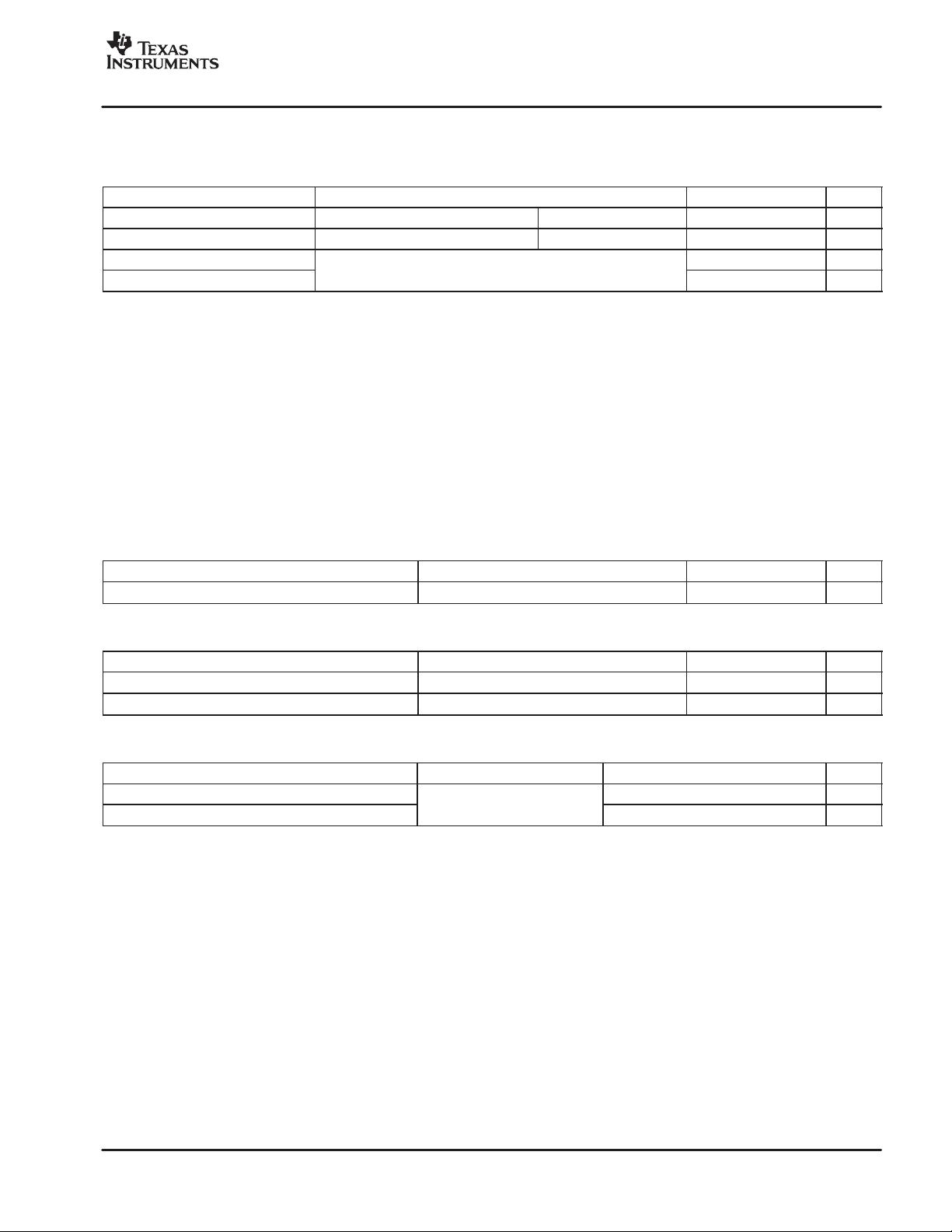

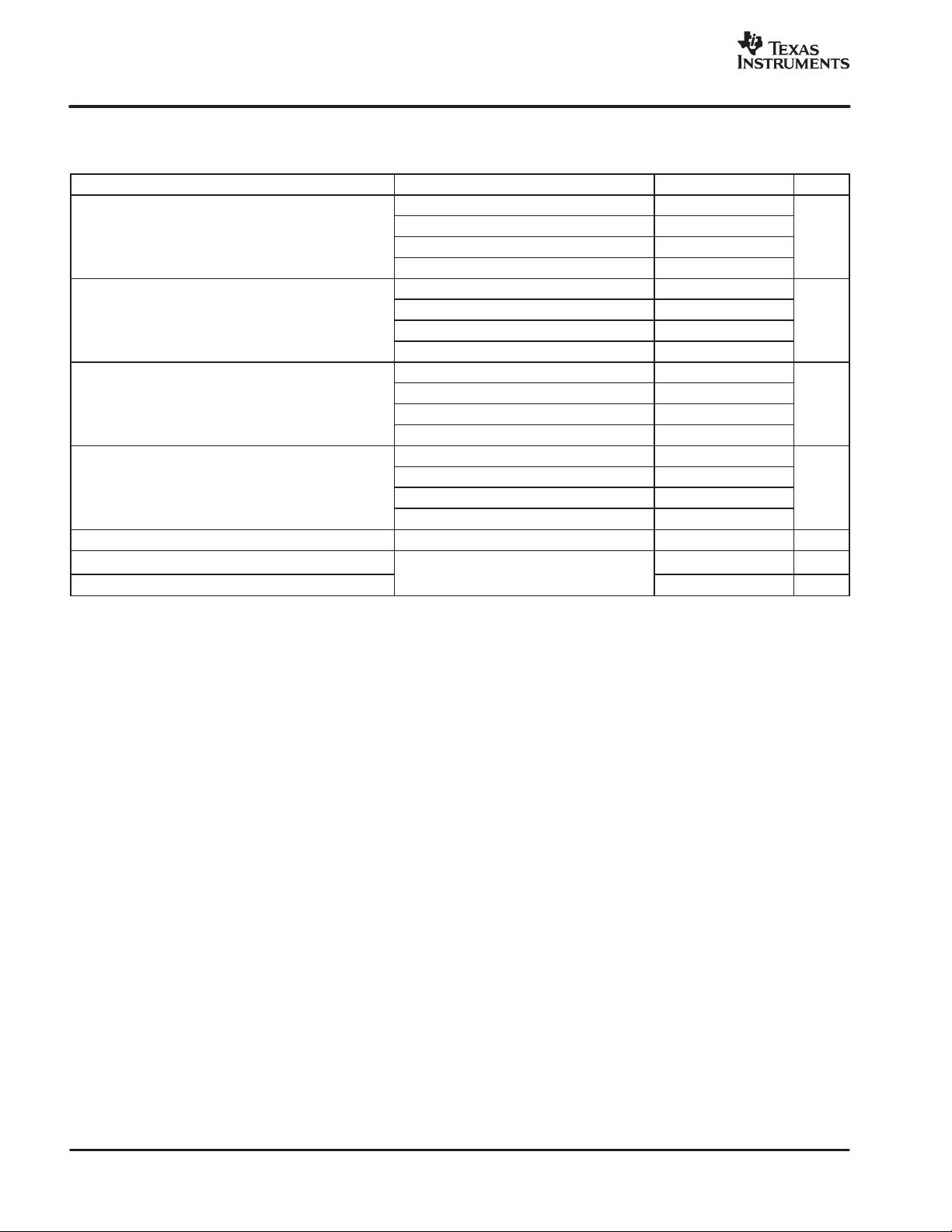

"TI-TLV5580.pdf" TI-TLV5580是一款高性能的8位模拟到数字转换器(ADC),具有80 MSPS(百万样本每秒)的采样速率,适用于各种高速数据处理和信号转换应用。这款芯片在设计上注重低功耗,典型工作状态下仅消耗165毫瓦的功率,这得益于其3.3伏的单电源操作。TI-TLV5580支持3.3V TTL/CMOS兼容的数字输入和输出,确保了与现代数字电路的无缝集成。 该ADC具备宽广的模拟输入带宽,典型值达到700 MHz,使得它能够处理高速的模拟信号。此外,它还内置了底部和顶部参考电压,允许用户进行内部电压基准调整,从而适应不同的应用场景。器件还提供了可选的外部参考电压,以增加设计的灵活性。 TI-TLV5580包含了电源管理功能,如电源下拉模式(Power Down,或Standby Mode),可以降低待机状态下的功耗。内部电压参考还可以单独进入低功耗模式,进一步优化能源效率。此ADC的输出设计为三态(Three-State Outputs),在不使用时能将输出端口置为高阻态,减少对系统总线的影响。 封装方面,TI-TLV5580采用28引脚的小外形集成电路(SOIC)和薄型小外形封装(TSSOP),这两种封装形式都适合空间有限的电路板布局。该器件适用于多种领域,包括: 1. 数字通信:在无线通信系统中,用于接收和发送信号的数字化处理。 2. 平板显示:在显示器中,用于处理图像信号的模数转换。 3. 高速数字信号处理器前端:与TMS320C6000等高速DSP配合,处理复杂的数字信号。 4. 医疗成像:在医疗设备中,用于将模拟信号转换为数字信号,进行图像分析和处理。 5. 图形处理(扫描率/格式转换):在图形和视频处理系统中,实现不同格式和速度的转换。 6. DVD读取通道数字化:在DVD播放器和其他光盘驱动器中,用于读取和处理光学信号。 TI-TLV5580是高速、低功耗模拟到数字转换应用的理想选择,特别适合需要高采样速率和宽输入带宽的系统。其特性集和封装选项使得它能够在多个行业中发挥关键作用,实现高效、准确的数据转换。

剩余37页未读,继续阅读

- 粉丝: 3513

- 资源: 5759

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

最新资源

- 前端面试必问:真实项目经验大揭秘

- 永磁同步电机二阶自抗扰神经网络控制技术与实践

- 基于HAL库的LoRa通讯与SHT30温湿度测量项目

- avaWeb-mast推荐系统开发实战指南

- 慧鱼SolidWorks零件模型库:设计与创新的强大工具

- MATLAB实现稀疏傅里叶变换(SFFT)代码及测试

- ChatGPT联网模式亮相,体验智能压缩技术.zip

- 掌握进程保护的HOOK API技术

- 基于.Net的日用品网站开发:设计、实现与分析

- MyBatis-Spring 1.3.2版本下载指南

- 开源全能媒体播放器:小戴媒体播放器2 5.1-3

- 华为eNSP参考文档:DHCP与VRP操作指南

- SpringMyBatis实现疫苗接种预约系统

- VHDL实现倒车雷达系统源码免费提供

- 掌握软件测评师考试要点:历年真题解析

- 轻松下载微信视频号内容的新工具介绍

信息提交成功

信息提交成功