Verilog HDL深度解析:时序篇——步骤、时钟与综合仿真

"Verilog_HDL_那些事儿_时序篇"

Verilog HDL是一种广泛用于数字系统设计的硬件描述语言,它允许工程师以抽象的方式描述电子系统的功能和行为。本教程“Verilog_HDL_那些事儿_时序篇”聚焦于时序设计的关键概念,这是Verilog HDL中的核心组成部分。

在时序设计中,"步骤"和"时钟"是两个至关重要的概念。步骤代表了模块执行任务的顺序和流程,就像音乐的节拍,指导着模块各个操作的展开。它定义了设计中的状态转换和操作过程,是理解模块动态行为的关键。通过引入步骤的概念,设计师可以更好地组织和控制复杂的逻辑操作,尤其是当需要处理多个并发事件时。

时钟则被视为模块的心跳,它定义了系统的时间基准,控制着数据的采样和更新。在数字系统中,大部分操作都与时钟周期同步,因此理解时钟对于避免通信错误至关重要。时钟边沿(上升沿或下降沿)通常触发数据的读取和写入,任何时钟同步问题都可能导致数据丢失、竞争条件或毛刺,这些是数字设计中的常见故障源。

传统上,状态机被广泛用于控制模块的行为,但随着设计复杂性的增加,单纯的状态机可能会导致设计过于臃肿,降低了模块的可读性和可维护性。通过使用步骤的概念,设计师可以创建更灵活的模型,例如模拟顺序操作,以应对更复杂的设计挑战。

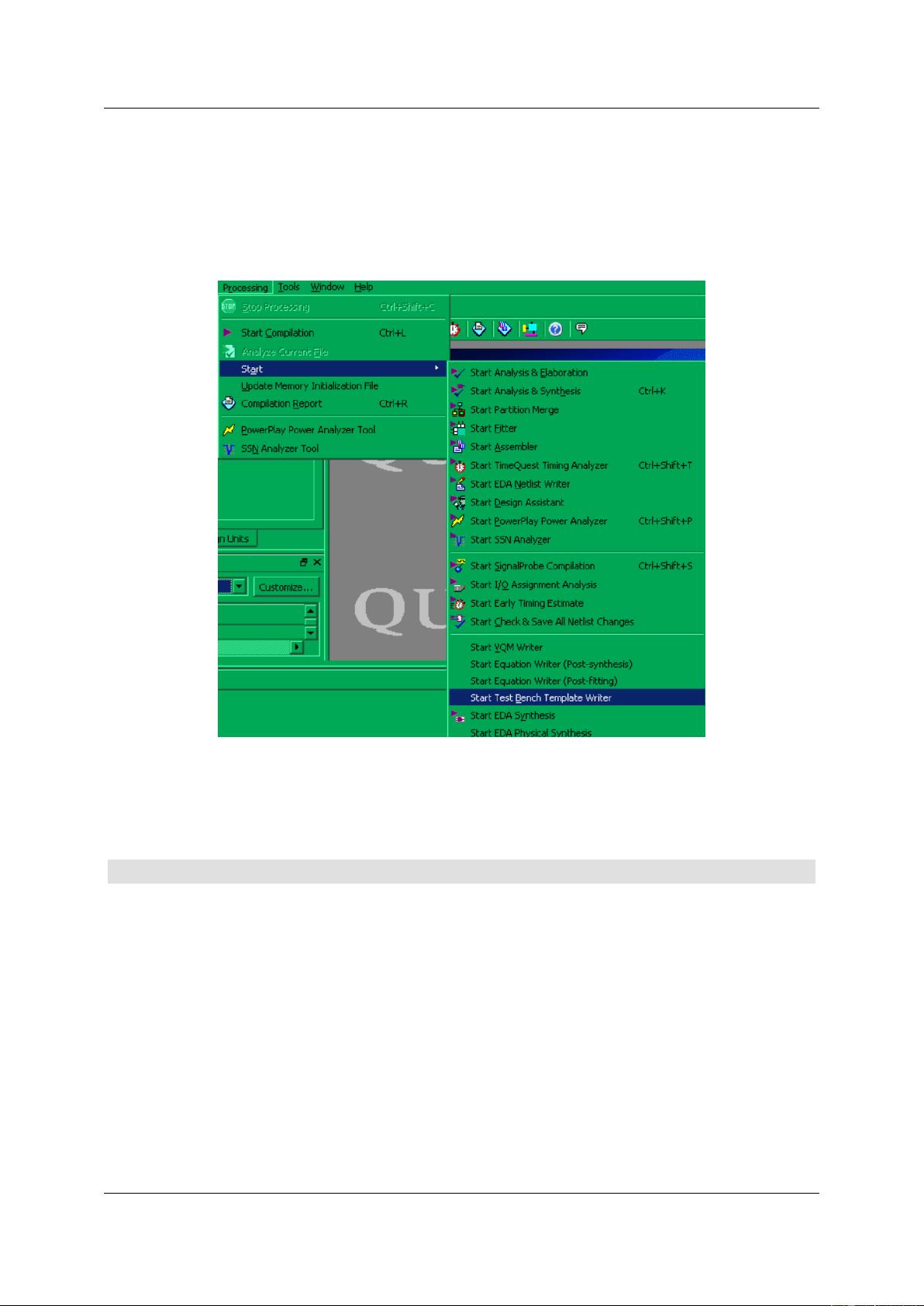

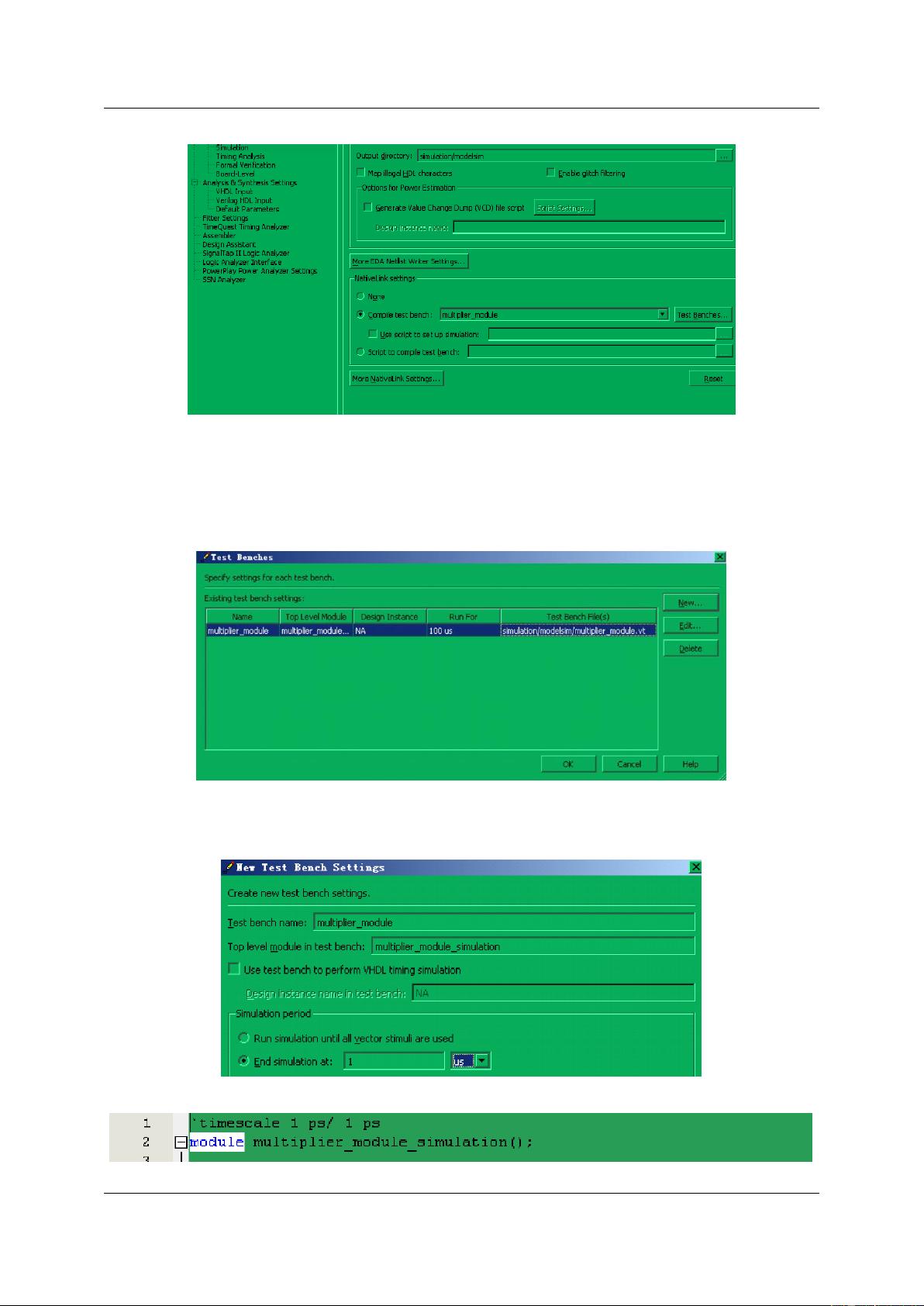

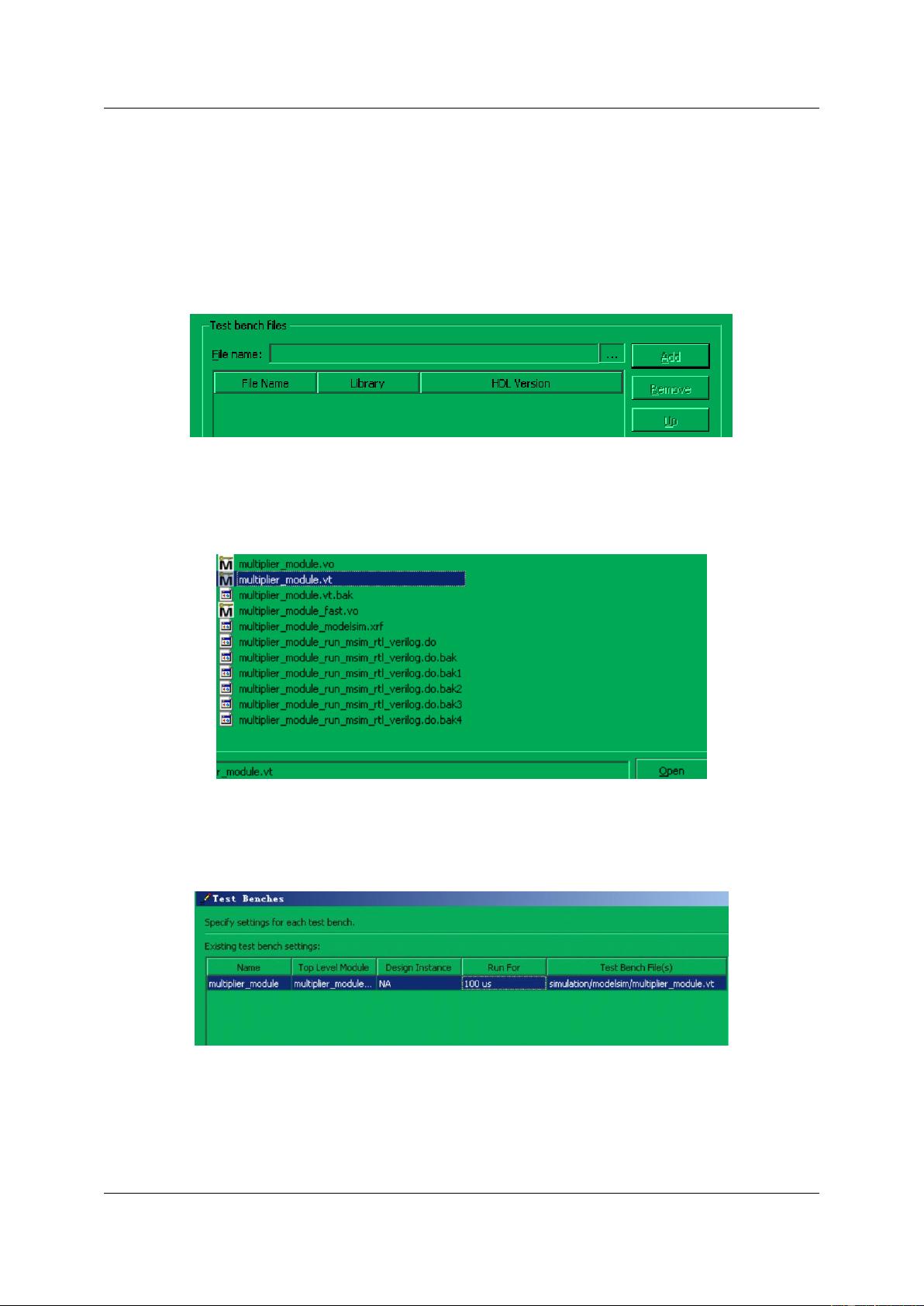

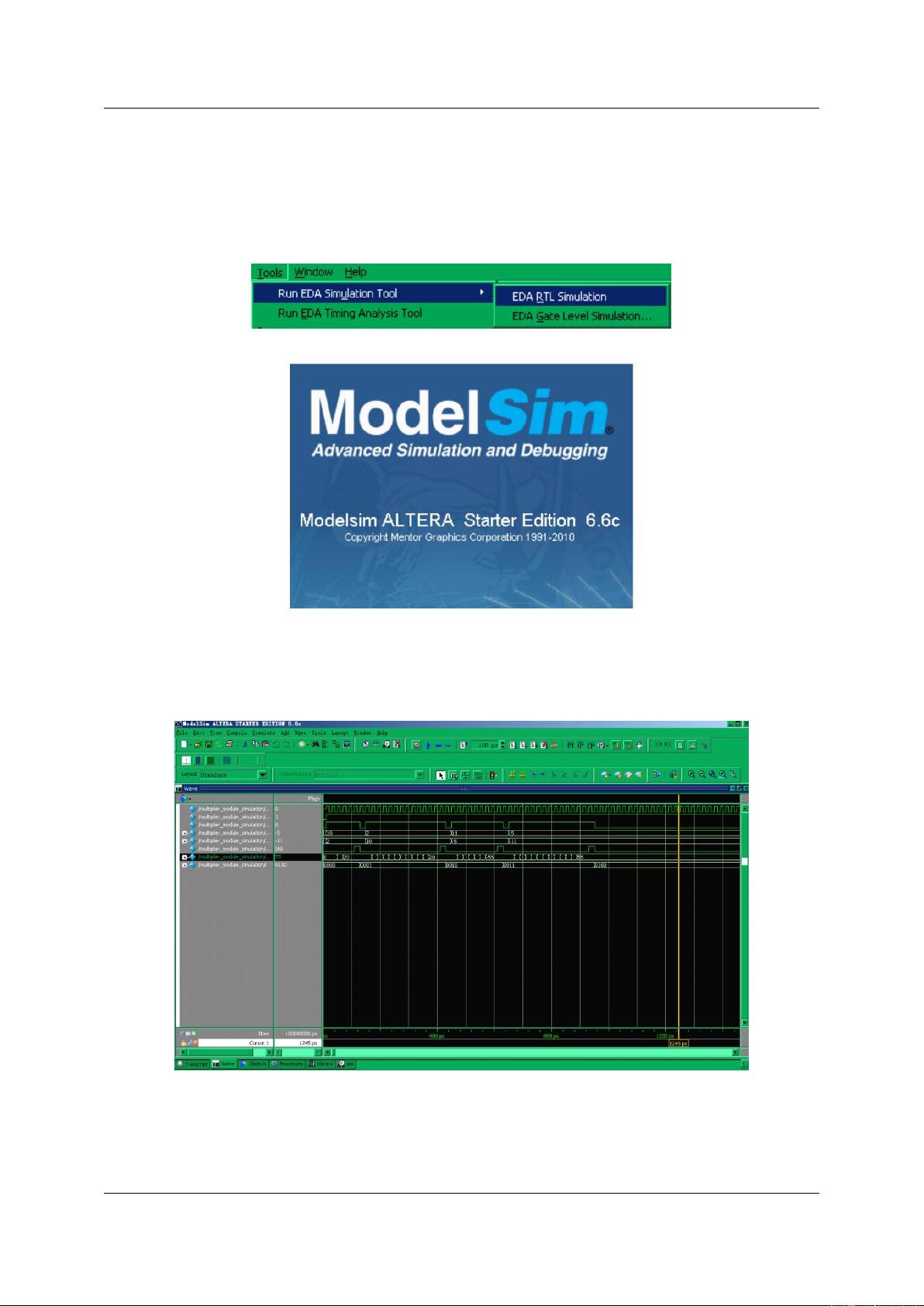

"综合"和"仿真"是Verilog设计流程中的两个重要阶段。综合是将Verilog代码转化为具体的门级网表的过程,这个过程中,编译器会根据设计约束优化逻辑,以满足目标设备的物理限制。而仿真则是验证设计功能是否符合预期的关键步骤,它在设计实现之前提供了对设计行为的模拟运行,帮助找出潜在错误。

“Verilog_HDL_那些事儿_时序篇”教程深入浅出地讲解了时序设计的关键元素,强调了步骤和时钟在模块设计中的核心地位,并介绍了如何通过综合和仿真确保设计的正确性和效率。对于初学者和经验丰富的工程师来说,这都是理解和提升Verilog HDL设计技能的重要参考资料。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2019-07-11 上传

2018-01-09 上传

2014-05-27 上传

2022-09-23 上传

2019-09-05 上传

2018-10-19 上传

szw892

- 粉丝: 0

- 资源: 10

最新资源

- 全国江河水系图层shp文件包下载

- 点云二值化测试数据集的详细解读

- JDiskCat:跨平台开源磁盘目录工具

- 加密FS模块:实现动态文件加密的Node.js包

- 宠物小精灵记忆配对游戏:强化你的命名记忆

- React入门教程:创建React应用与脚本使用指南

- Linux和Unix文件标记解决方案:贝岭的matlab代码

- Unity射击游戏UI套件:支持C#与多种屏幕布局

- MapboxGL Draw自定义模式:高效切割多边形方法

- C语言课程设计:计算机程序编辑语言的应用与优势

- 吴恩达课程手写实现Python优化器和网络模型

- PFT_2019项目:ft_printf测试器的新版测试规范

- MySQL数据库备份Shell脚本使用指南

- Ohbug扩展实现屏幕录像功能

- Ember CLI 插件:ember-cli-i18n-lazy-lookup 实现高效国际化

- Wireshark网络调试工具:中文支持的网口发包与分析