Verilog HDL时序篇探索:步骤、时钟与模块优化

需积分: 10 72 浏览量

更新于2024-07-17

收藏 6.92MB PDF 举报

"3Verilog_HDL_那些事儿_时序篇.pdf,黑金动力社区系列教程,深入探讨Verilog HDL的时序概念,包括步骤与时钟、综合与仿真"

在《Verilog HDL那些事儿-时序篇》中,作者着重讲述了Verilog HDL在时序设计方面的关键概念。这本书分为两个主要部分:步骤和时钟,以及综合和仿真。这两个部分共同构成了理解数字系统设计中时序逻辑的基础。

首先,关于"步骤"和"时钟",作者强调了它们在模块设计中的核心地位。在宏观层面上,"步骤"定义了模块执行的节奏,如同音乐的节拍,而"时钟"则像是模块的心跳,控制着模块的活动周期。在微观层面,"步骤"代表着模块执行的具体操作或状态变化,而"时钟"则作为这些操作的时间基准,是最小的时间单位。作者指出,传统的状态机设计可能导致模块复杂度增加和表达能力下降。通过引入"步骤"的概念,可以实现更灵活的建模策略,比如模拟顺序操作,这样既简化了建模,也直观地揭示了模块的操作流程和状态,对于后续的模块优化至关重要。

其次,"时钟"在模块间通信中的作用不容忽视。由于大部分数字系统是基于时钟同步的,因此,模块间的通信问题往往与时钟对齐有关。如果通信时机不当,即慢了一个时钟周期或早了一个时钟周期,就可能导致严重的错误。因此,深入理解时钟对于分析和解决这类问题至关重要,尤其是在多模块设计中。

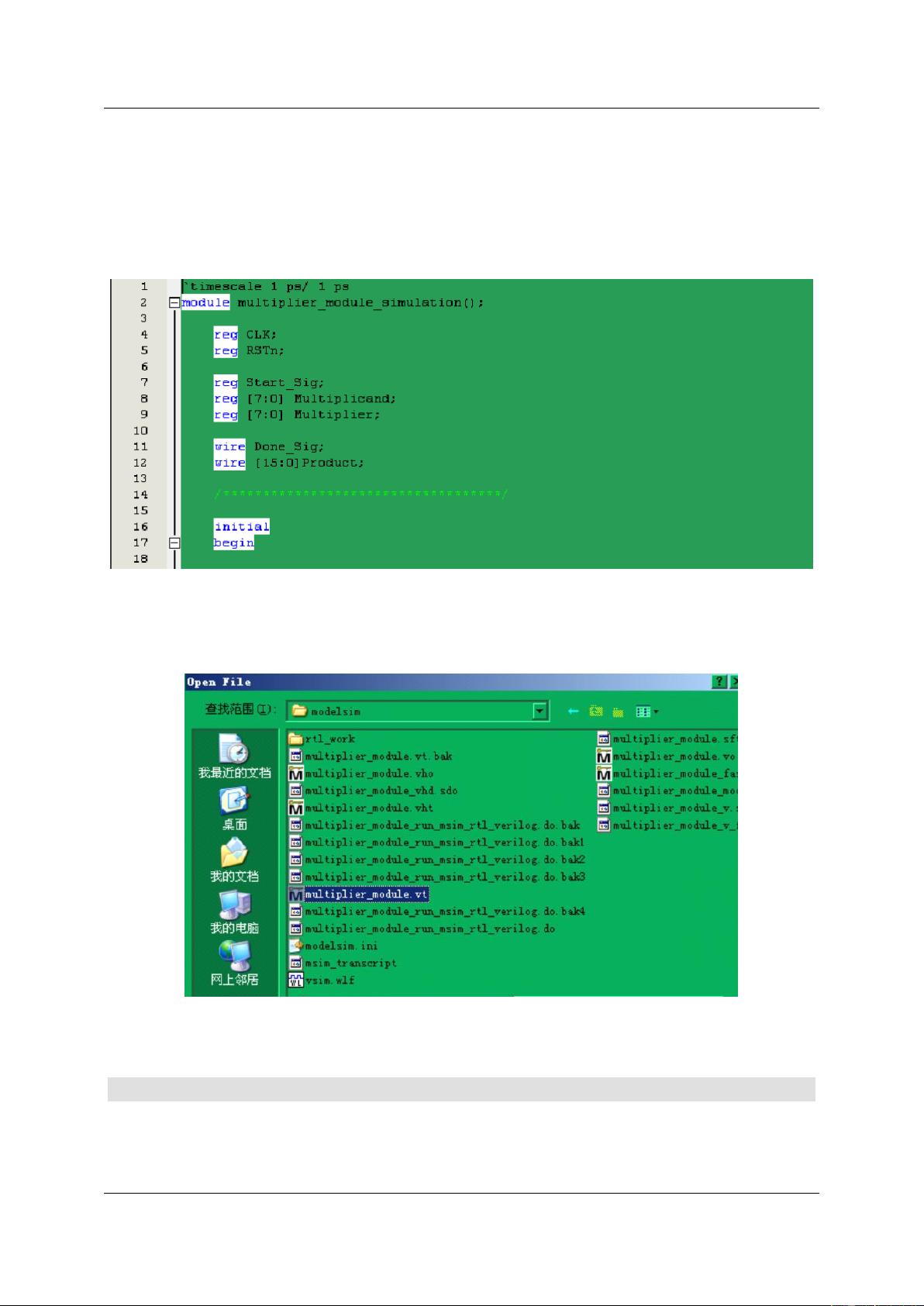

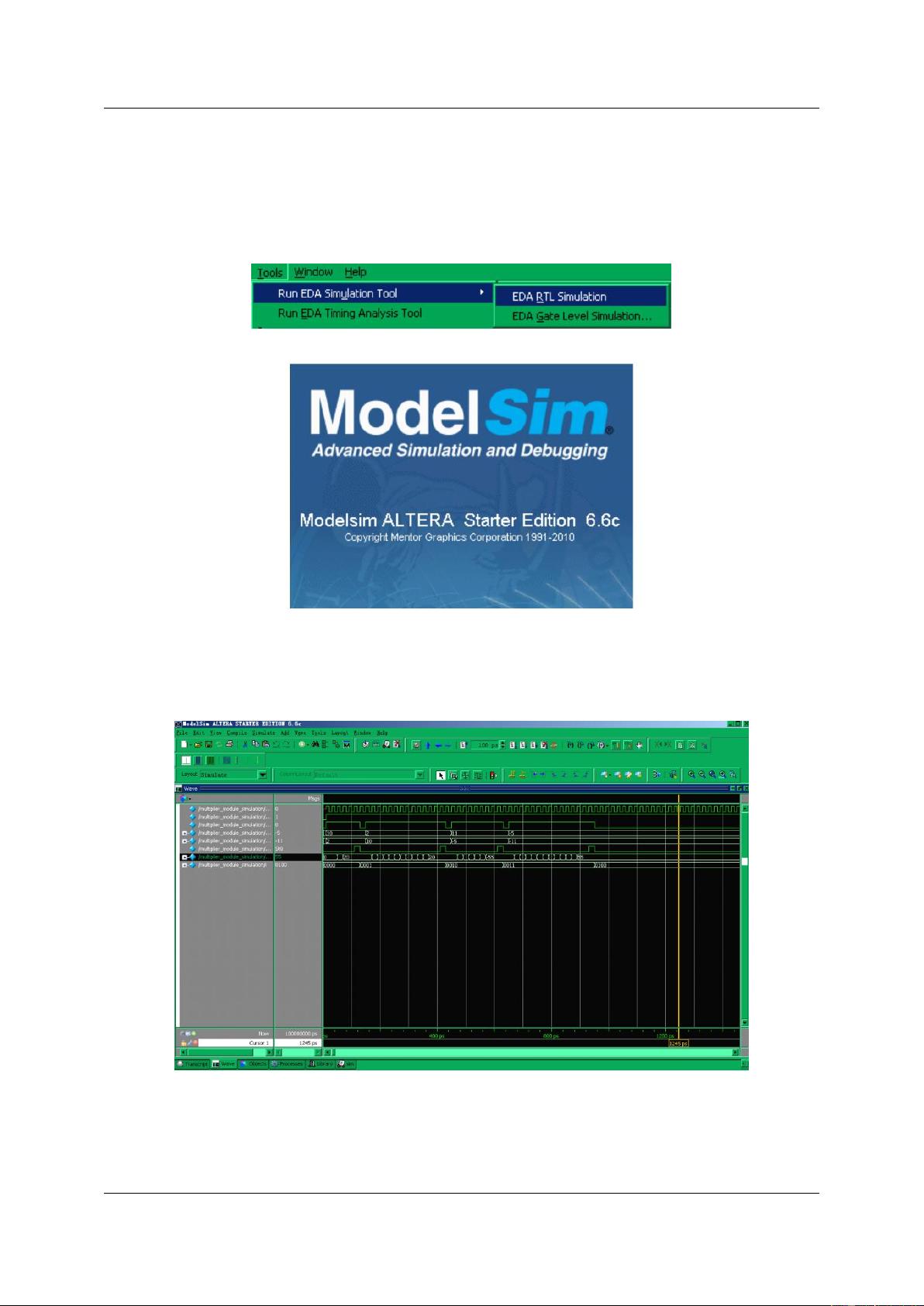

至于"综合"和"仿真",这是硬件设计流程中的两个关键步骤。"综合"是将高级语言描述的逻辑转换为门级网表的过程,它直接影响到最终的电路实现效果。而"仿真"则是验证设计功能是否符合预期的重要手段。将两者放在一起学习,可以帮助设计师更好地理解设计到硬件的实际转化过程,以及如何通过仿真来检测和修复潜在问题。

《Verilog HDL那些事儿-时序篇》深入浅出地阐述了Verilog HDL在构建时序逻辑时的关键要素,对于提升设计师的时序理解和建模能力有着极大的帮助。无论是初学者还是经验丰富的工程师,都能从中受益,提升自己的设计水平。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2022-09-23 上传

2019-09-05 上传

2020-03-31 上传

2021-10-04 上传

2022-09-19 上传

2011-11-10 上传

yalipf

- 粉丝: 3944

- 资源: 27

最新资源

- 俄罗斯RTSD数据集实现交通标志实时检测

- 易语言开发的文件批量改名工具使用Ex_Dui美化界面

- 爱心援助动态网页教程:前端开发实战指南

- 复旦微电子数字电路课件4章同步时序电路详解

- Dylan Manley的编程投资组合登录页面设计介绍

- Python实现H3K4me3与H3K27ac表观遗传标记域长度分析

- 易语言开源播放器项目:简易界面与强大的音频支持

- 介绍rxtx2.2全系统环境下的Java版本使用

- ZStack-CC2530 半开源协议栈使用与安装指南

- 易语言实现的八斗平台与淘宝评论采集软件开发

- Christiano响应式网站项目设计与技术特点

- QT图形框架中QGraphicRectItem的插入与缩放技术

- 组合逻辑电路深入解析与习题教程

- Vue+ECharts实现中国地图3D展示与交互功能

- MiSTer_MAME_SCRIPTS:自动下载MAME与HBMAME脚本指南

- 前端技术精髓:构建响应式盆栽展示网站