Spartan-6 FPGA SelectIO Resources User Guide

"Spartan-6+IO资源用户手册提供了关于如何使用Spartan-6 FPGA的输入/输出(IO)资源的详细指南,适用于设计与Xilinx硬件设备协同工作的方案。"

Spartan-6 FPGA是Xilinx公司推出的一款FPGA(Field-Programmable Gate Array)芯片系列,它在嵌入式系统、通信、计算和各种工业应用中广泛应用。该系列FPGA具有丰富的逻辑单元、分布式存储器和I/O资源,使得它能够灵活地满足各种定制化需求。

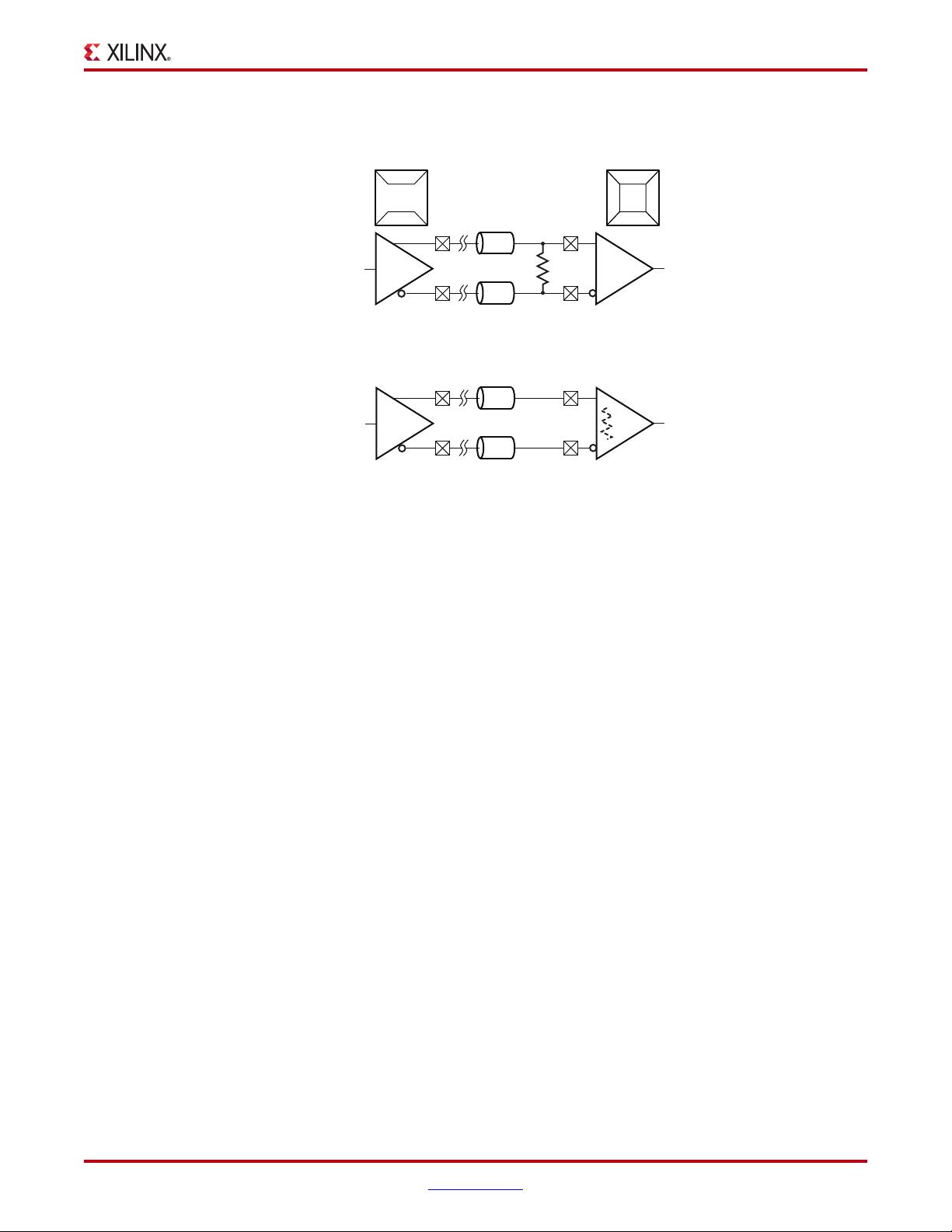

SelectIO资源是Spartan-6 FPGA的一个关键特性,它涉及到芯片外部接口的配置和管理。SelectIO技术允许设计者根据应用需求调整I/O的性能参数,如速度、电压电平和驱动电流等。用户手册《Spartan-6 FPGA SelectIO Resources User Guide UG381(v1.3)》详细介绍了如何有效地利用这些资源进行系统设计。

手册中可能涵盖的内容包括:

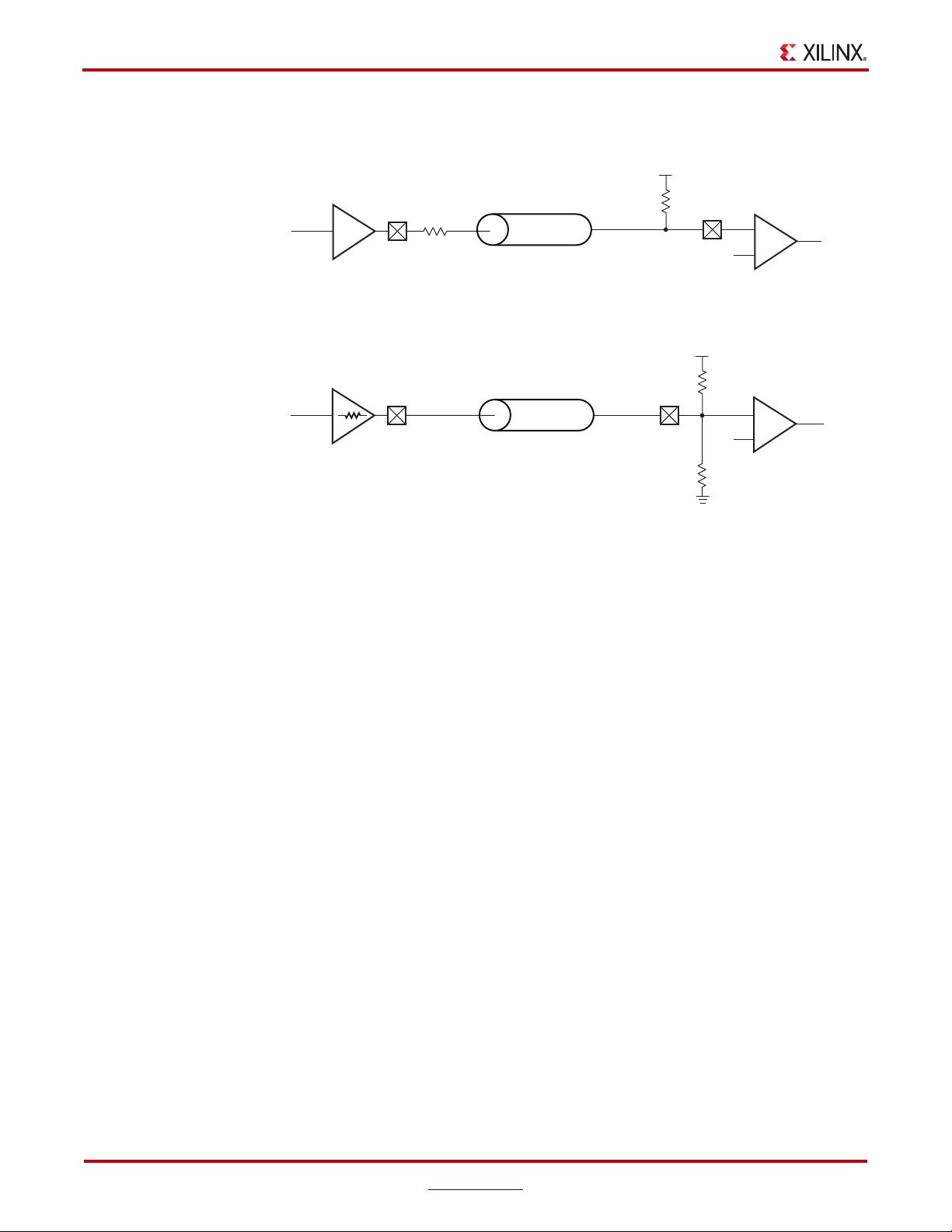

1. **I/O标准**:介绍支持的不同I/O标准,如LVCMOS、LVDS、HSTL、SSTL等,以及如何选择适合特定应用的I/O标准。

2. **I/O Bank**:解释Spartan-6 FPGA中的I/O Bank结构,每个Bank的特性,以及如何分配和配置I/O引脚。

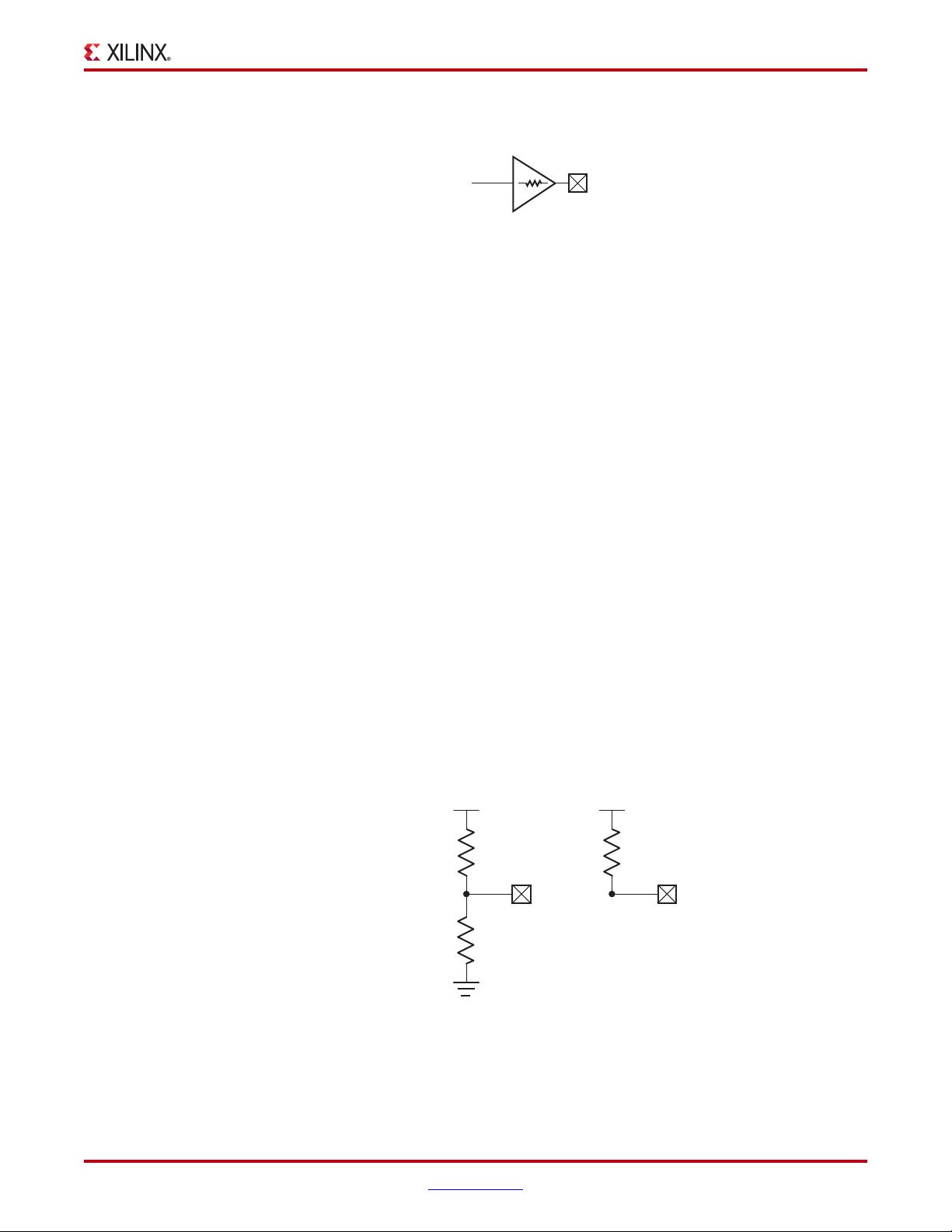

3. **I/O缓冲**:描述输入和输出缓冲器的功能,包括速度等级、电压摆幅和驱动能力的配置。

4. **I/O串行化和解串化**:讨论如何使用串行/并行转换功能,以实现高速数据传输。

5. **时序分析**:提供有关满足时序约束的指导,确保正确操作I/O接口。

6. **电源管理**:介绍I/O电源的规划和管理,以降低功耗并提高系统稳定性。

7. **热插拔和ESD保护**:解释如何实现这些功能以增强系统的可靠性。

8. **设计示例和应用笔记**:提供实际案例,帮助用户理解和应用SelectIO特性。

9. **约束文件设置**:说明如何在硬件描述语言(如VHDL或Verilog)中定义和约束I/O资源。

10. **工具使用**:指导用户如何使用Xilinx的开发工具,如ISE(Integrated Software Environment)进行SelectIO资源的配置和仿真。

请记住,Xilinx提供的文档仅供开发目的使用,并且在使用时应遵守其许可条款。由于文档内容不提供任何保修,用户在设计过程中需要自行承担风险。Xilinx保留随时更新文档而不事先通知的权利,且不对提供的技术支持或协助产生的任何问题承担责任。因此,设计者应密切关注Xilinx的最新更新和技术支持,以确保设计的准确性和兼容性。

2011-08-26 上传

2021-03-14 上传

点击了解资源详情

2021-06-10 上传

2019-05-19 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

Ljwx211314

- 粉丝: 0

- 资源: 11