Xilinx AXI Interconnect v2.1:FPGA设计指南

需积分: 11 42 浏览量

更新于2024-07-21

1

收藏 2.47MB PDF 举报

"AXI总线是Xilinx公司的一种高性能、低延迟的接口协议,用于在片上系统(SoC)或FPGA中连接不同组件。AXIInterconnect v2.1是Xilinx Vivado Design Suite的一个LogiCORE IP,提供了详细的设计指南,帮助用户理解和配置AXI接口以优化系统性能。此文档涵盖了AXI基础设施核心的功能概述、产品规格、设计流程步骤以及升级迁移指南等关键信息。"

AXI总线协议详解:

AXI(Advanced eXtensible Interface)总线协议是ARM公司提出的一种开放标准接口,广泛应用于FPGA和ASIC设计中。它分为多种类型,包括AXI4、AXI4-Lite、AXI4-Stream等,以满足不同带宽需求和应用场景。

1. AXI4:适用于高性能主存和外设访问,支持读写操作,并包含完整的地址、数据和控制信号。

2. AXI4-Lite:简化版的AXI,适合低带宽、简单控制接口的外设。

3. AXI4-Stream:针对单向连续数据流传输,常用于DMA和视频处理等应用。

AXIInterconnect v2.1特性与应用:

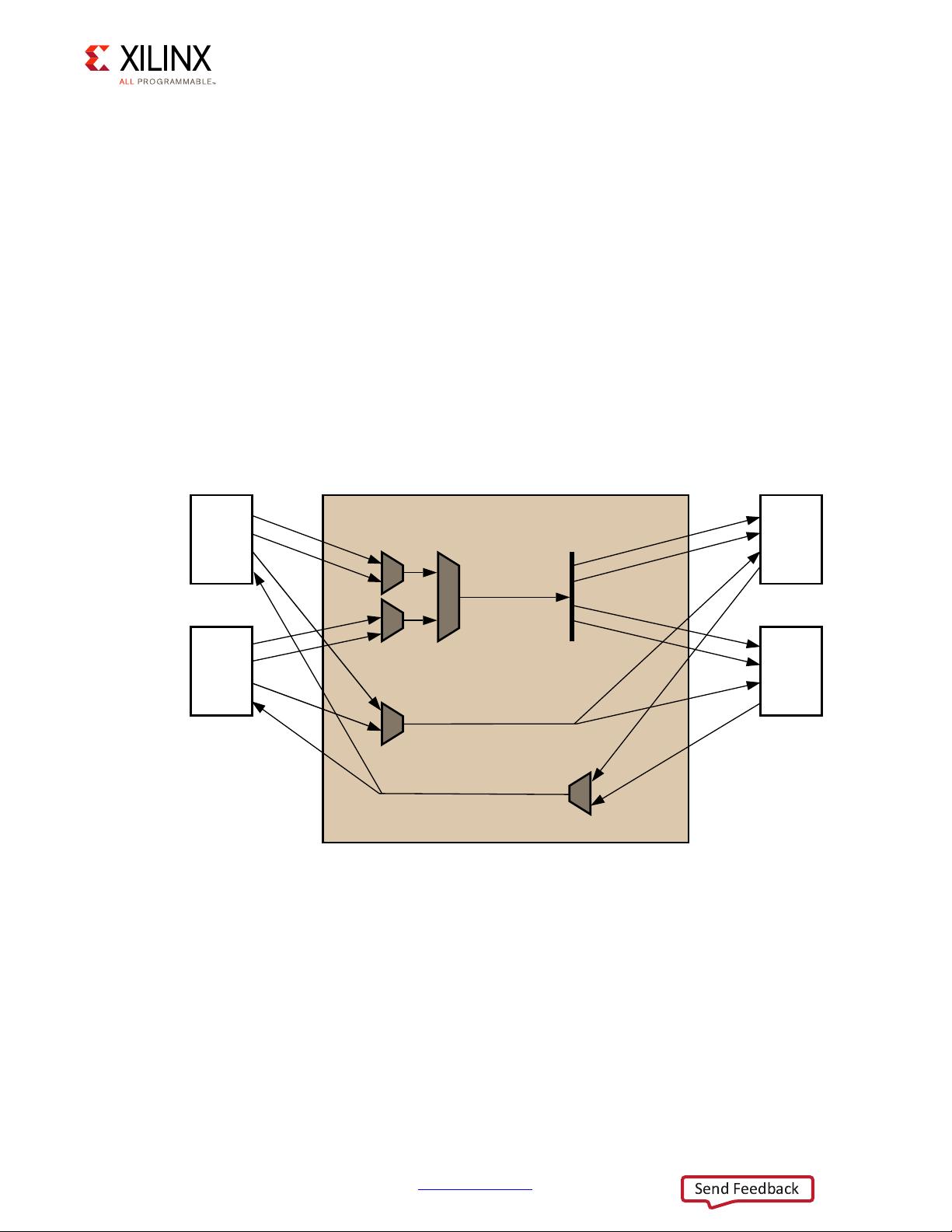

- 功能概览:该IP核提供了一个灵活的互连解决方案,可连接多个AXI主设备和从设备,支持多总线仲裁策略。

- 应用场景:适用于SoC设计,可以实现处理器、存储器、外设间的高效通信。

- 限制:文档中可能详细列出了一些设计上的限制,例如连接数量、最大带宽等。

- 许可与订购信息:可能包含了IP核的许可条件和购买指南。

设计规范与性能:

- 使用模型:描述了AXIInterconnect在设计中的各种工作模式,如单主设备或多主设备配置。

- 标准:AXI遵循的行业标准,确保与其他AXI兼容组件的互操作性。

- 延迟:分析了读写操作的传输延迟,对系统性能有直接影响。

- 最大性能:给出了IP核在不同配置下的理论峰值性能。

- 资源利用率:详述了IP核在不同设计中的逻辑资源占用情况。

设计流程:

- 核心功能:解释了AXIInterconnect如何协调和管理多个AXI接口间的通信,包括参数配置选项。

- 设计参数:列出了可供用户自定义的参数,如总线宽度、通道数量等。

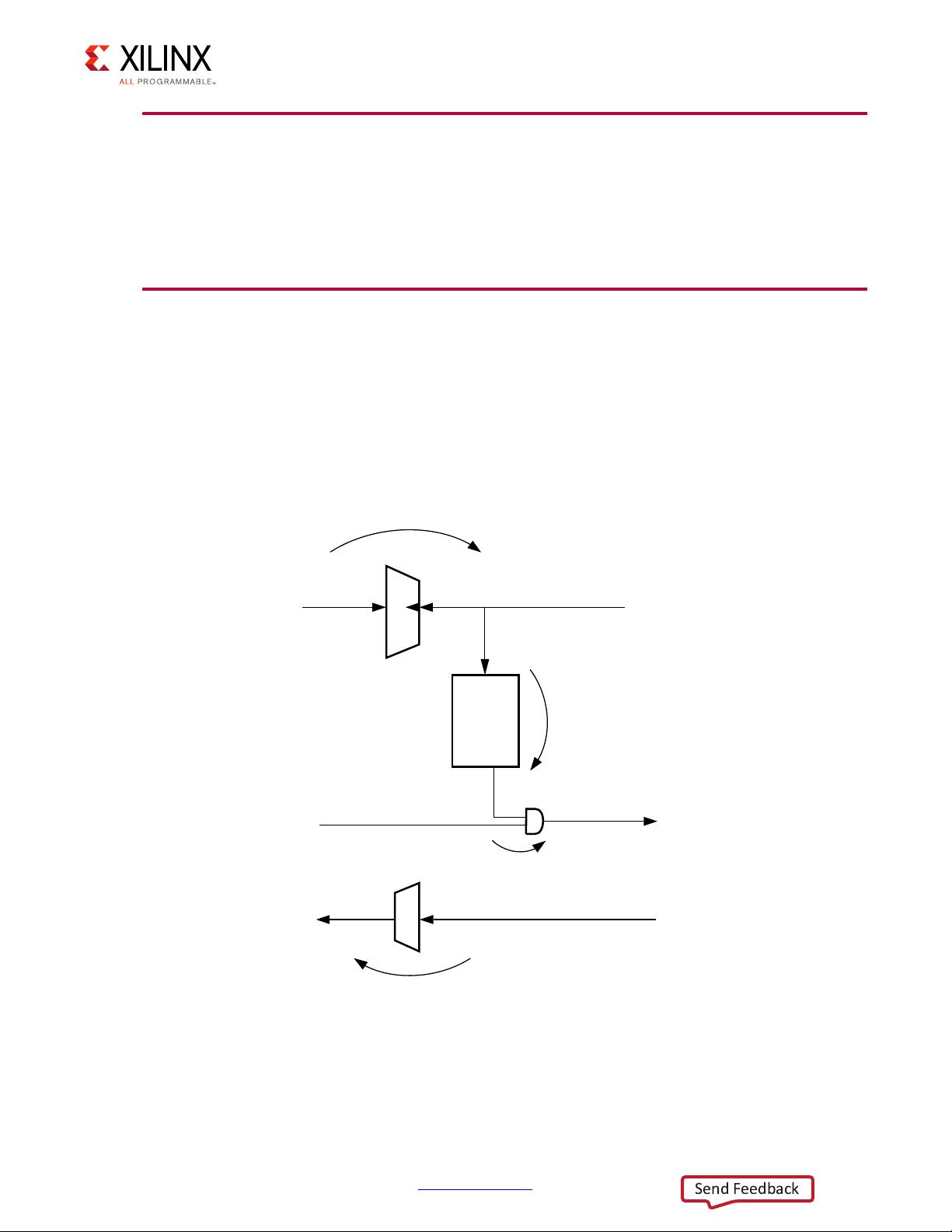

- 时钟与复位:讨论了时钟域同步和复位信号的管理,这对于避免数据错误至关重要。

- 定制与生成:指导用户如何在Vivado中配置和生成AXIInterconnect IP。

- 约束、仿真、综合与实现:提供设计流程的具体步骤,帮助用户成功集成并优化IP。

示例设计:

- 提供了实际的设计案例,帮助用户理解如何在具体项目中应用AXIInterconnect。

升级与迁移:

- 迁移指南:对于从早期版本的AXIInterconnect或其它AXI实现迁移到v2.1的用户,提供了详细步骤。

综上,AXI总线及其Interconnect IP是构建高效、可扩展的FPGA系统的关键组件,通过理解并正确使用这些资源,设计师能够实现更高效、更具灵活性的SoC设计。

2106 浏览量

417 浏览量

644 浏览量

2021-10-12 上传

376 浏览量

386 浏览量

239 浏览量

236 浏览量

victoryy222

- 粉丝: 0

- 资源: 2

最新资源

- vehiclesAPI:带有nodejs express的车辆休息API

- pngnq-s9:修改后的pngnq:将png图像转换为256色。-开源

- 模拟随机游走_随机游走模拟_随机游走_python_

- TheWarez

- AxureUX 后台管理系统框架原型模板.rar

- example-prometheus-nodejs:带有Node.js的Prometheus监视示例

- ssm框架实现的网上书店系统.zip

- can_loopback_test_CAN;verilog_

- fullstack-web-dev-studies:创建此存储库是为了存储Igor Oliveira(又名“ ProgramadorBR”)的Web开发人员课程中的内容

- HP 3PAR Management Console 4.3

- TheKeeper:JS13K游戏2015

- kerk-planning

- CSS Posicionamento:CSS Posicionamento

- AxureRP实战手册案例-免费20个.rar

- check_mk_extensions:check_mk插件

- plugin.audio.beets:用于从甜菜网络服务器流式传输音频的 Kodi 插件