UCD90910

www.ti.com

SLVSA81 –JULY 2010

Table 1. PIN FUNCTIONS (continued)

PIN NAME PIN NO. I/O TYPE DESCRIPTION

INPUT POWER AND GROUNDS

RESET 9 Active-low device reset input. Hold low for at least 2 ms to reset the device.

V33FB 58 3.3-V linear regulator feedback connection

V33A 46 Analog 3.3-V supply

V33D 45 Digital core 3.3-V supply

V33DIO1 7 Digital I/O 3.3-V supply

V33DIO2 44 Digital I/O 3.3-V supply

BPCAP 47 1.8-V bypass capacitor – tie 0.1-mF capacitor to analog ground.

AVSS1 49 Analog ground

AVSS2 48 Analog ground

AVSS3 64 Analog ground

DVSS1 8 Digital ground

DVSS2 26 Digital ground

DVSS3 43 Digital ground

QFP ground pad NA Thermal pad – tie to ground plane.

FUNCTIONAL DESCRIPTION

TI FUSION GUI

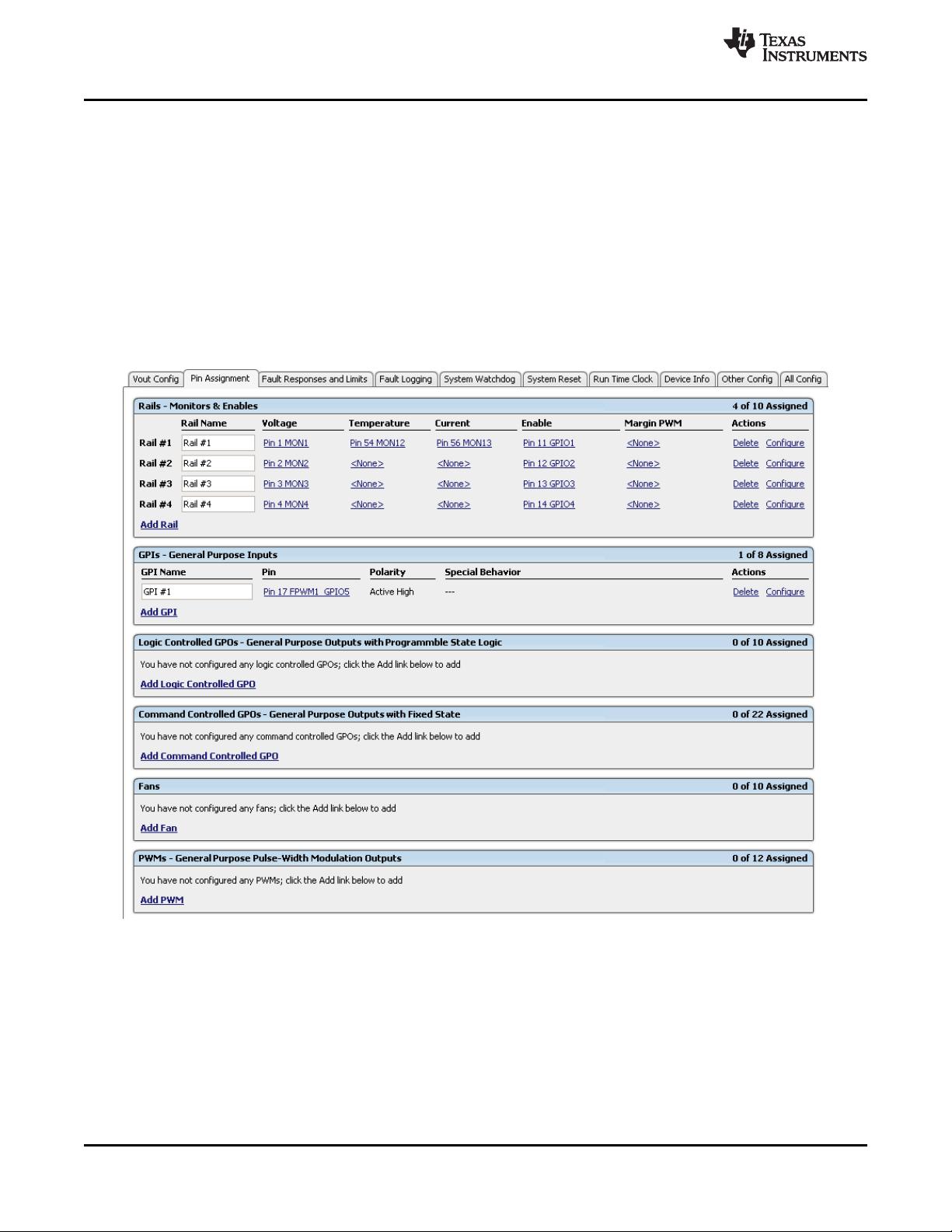

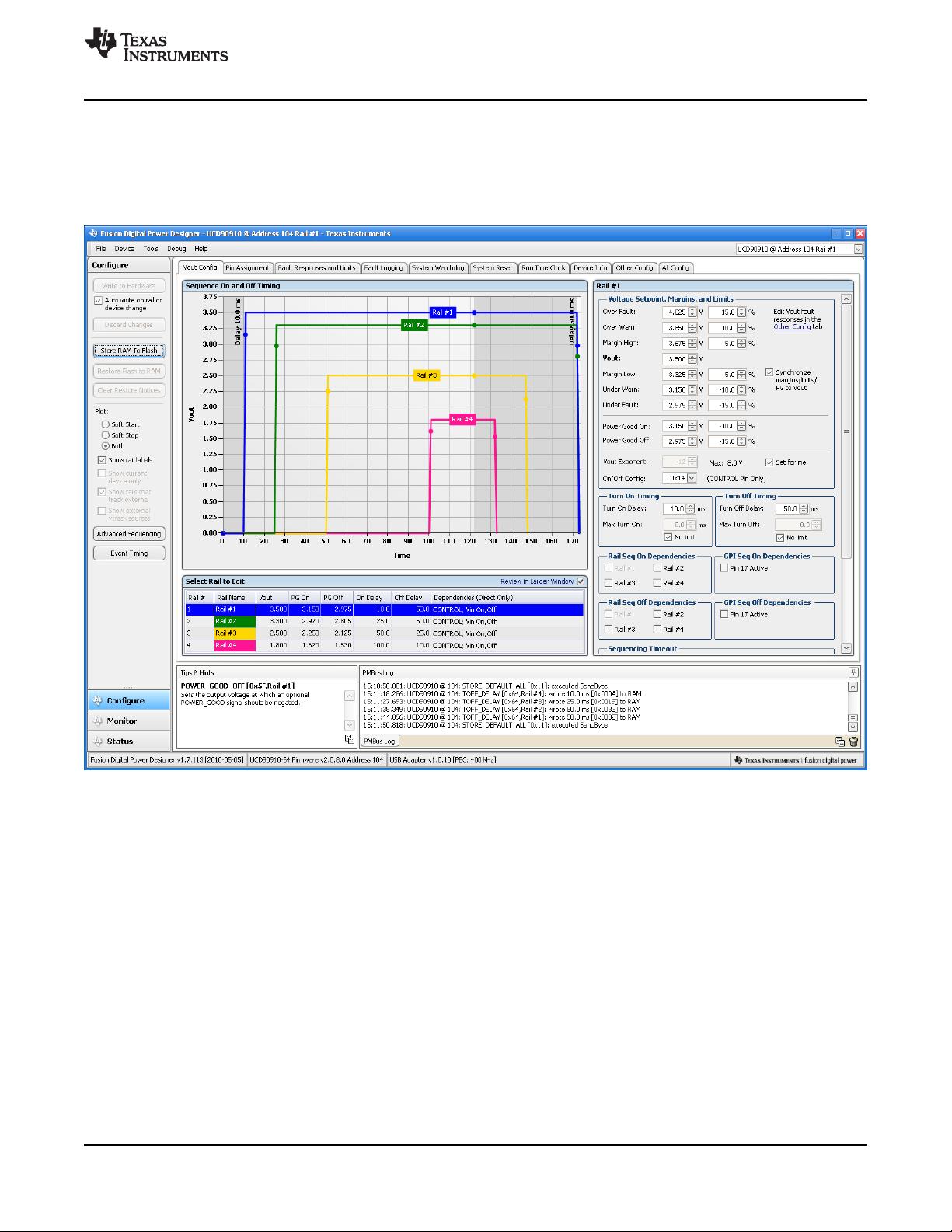

The Texas Instruments Fusion Digital Power Designer is provided for device configuration. This PC-based

graphical user interface (GUI) offers an intuitive I

2

C/PMBus interface to the device. It allows the design engineer

to configure the system operating parameters for the application without directly using PMBus commands, store

the configuration to on-chip nonvolatile memory, and observe system status (voltage, temperature, etc). Fusion

Digital Power Designer is referenced throughout the data sheet as Fusion GUI and many sections include

screenshots. The Fusion GUI can be downloaded from www.ti.com.

PMBUS INTERFACE

The PMBus is a serial interface specifically designed to support power management. It is based on the SMBus

specification that is built on the I

2

C physical interface. The UCD90910 supports revision 1.1 of the PMBus

standard. Wherever possible, standard PMBus commands are used to support the function of the device. For

unique features of the UCD90910, MFR_SPECIFIC commands are defined to configure or activate those

features. These commands are defined in the UCD90xxx Sequencer and System Health Controller PMBUS

Command Reference (SLVU352).

This document makes frequent mention of the PMBus specification. Specifically, this document is PMBus Power

System Management Protocol Specification Part II – Command Language, Revision 1.1, dated 5 February 2007.

The specification is published by the Power Management Bus Implementers Forum and is available from

www.pmbus.org.

The UCD90910 is PMBus compliant, in accordance with the Compliance section of the PMBus specification. The

firmware is also compliant with the SMBus 1.1 specification, including support for the SMBus ALERT function.

The hardware can support either 100-kHz or 400-kHz PMBus operation.

THEORY OF OPERATION

Modern electronic systems often use numerous microcontrollers, DSPs, FPGAs, and ASICs. Each device can

have multiple supply voltages to power the core processor, analog-to-digital converter, or I/O. These devices are

typically sensitive to the order and timing of how the voltages are sequenced on and off. The UCD90910 can

sequence supply voltages to prevent malfunctions, intermittent operation, or device damage caused by improper

power up or power down. Appropriate handling of under- and overvoltage faults, overcurrent faults and

overtemperature faults can extend system life and improve long-term reliability. The UCD90910 stores power

supply faults to on-chip nonvolatile flash memory for aid in system failure analysis.

Copyright © 2010, Texas Instruments Incorporated Submit Documentation Feedback 9

Product Folder Link(s) :UCD90910