门控时钟驱动的低功耗约翰逊计数器设计与应用

148 浏览量

更新于2024-08-30

收藏 281KB PDF 举报

在现代电子设计中,基于门控时钟的低功耗时序电路设计成为关键要素。传统的电路设计中,所有计算任务都依赖于全局时钟,这导致了大量时序电路的需求,特别是在移动设备等电池供电设备中,功耗管理变得至关重要。为了节省功率,设计师采用电源域划分技术,根据需要动态关闭部分电路,同时优化每个时序电路的能耗。

约翰逊计数器作为一种典型的时序电路,因其能够同步提供多种特殊数据序列而被广泛应用在诸如D/A转换器、有限状态机(FSM)和时钟分频器等核心模块中。这些应用需要支持从MHz到GHz的不同工作频率。随着片上系统的复杂性提升,设计者倾向于集成更多的IP,这就要求时钟分频器具有灵活性,以适应各种频率需求。

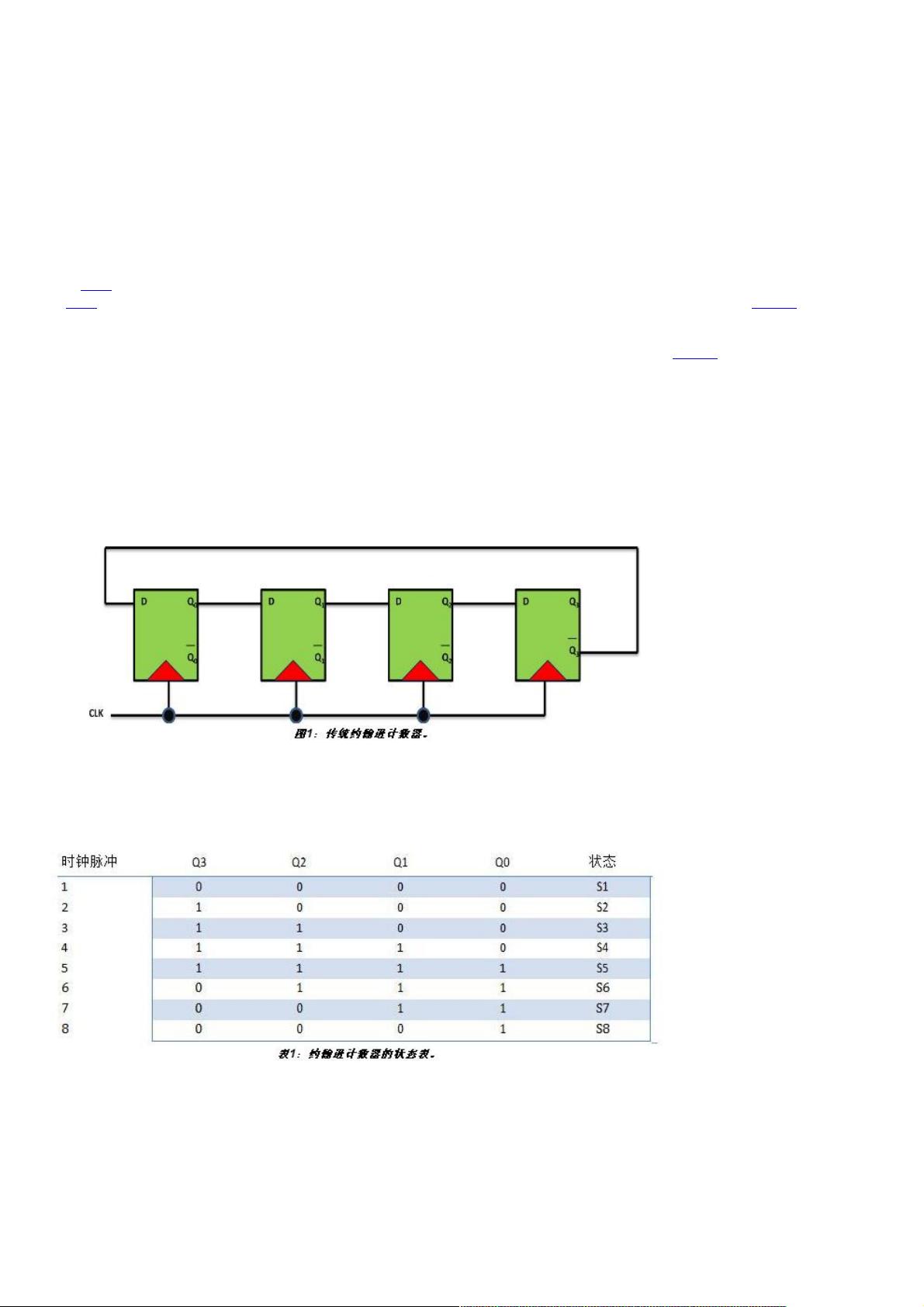

传统约翰逊计数器,如图1所示的4位上升沿设计,通过一个触发器的反相输出与下一个触发器相连,形成一个具有多个阶段的独特数据模式。这种结构使得约翰逊计数器能够在不失真的情况下调整时钟周期,实现精确的分频功能。然而,这类设计往往消耗较多的功率。

本文提出了一种创新的解决方案,即使用带有门控时钟的多级可编程约翰逊计数器系统。这种设计允许动态调整时钟频率,仅在需要时才激活,从而显著降低功耗。通过门控时钟技术,计数器可以提供从8到38(或其他偶数值)的可变分频因子,实现了更高的能效比。这种技术的优势在于灵活性和能效,但可能牺牲了一些即时响应速度或硬件复杂度,具体取决于设计目标和应用场景。

基于门控时钟的低功耗时序电路设计是现代电子设计中的一个重要课题,它通过优化时钟管理和电路控制,帮助电子设备在满足高性能需求的同时,有效地管理功耗,这对于电池续航和整体系统性能的提升具有重要意义。

2009-09-14 上传

2020-10-19 上传

2020-10-20 上传

2020-08-29 上传

点击了解资源详情

2020-08-19 上传

2021-02-03 上传

2021-05-25 上传

点击了解资源详情

weixin_38582719

- 粉丝: 11

- 资源: 952

最新资源

- JHU荣誉单变量微积分课程教案介绍

- Naruto爱好者必备CLI测试应用

- Android应用显示Ignaz-Taschner-Gymnasium取消课程概览

- ASP学生信息档案管理系统毕业设计及完整源码

- Java商城源码解析:酒店管理系统快速开发指南

- 构建可解析文本框:.NET 3.5中实现文本解析与验证

- Java语言打造任天堂红白机模拟器—nes4j解析

- 基于Hadoop和Hive的网络流量分析工具介绍

- Unity实现帝国象棋:从游戏到复刻

- WordPress文档嵌入插件:无需浏览器插件即可上传和显示文档

- Android开源项目精选:优秀项目篇

- 黑色设计商务酷站模板 - 网站构建新选择

- Rollup插件去除JS文件横幅:横扫许可证头

- AngularDart中Hammock服务的使用与REST API集成

- 开源AVR编程器:高效、低成本的微控制器编程解决方案

- Anya Keller 图片组合的开发部署记录