Xilinx System Generator for DSP: 以太网硬件协仿真接口加速FPGA仿真

13 浏览量

更新于2024-08-28

收藏 266KB PDF 举报

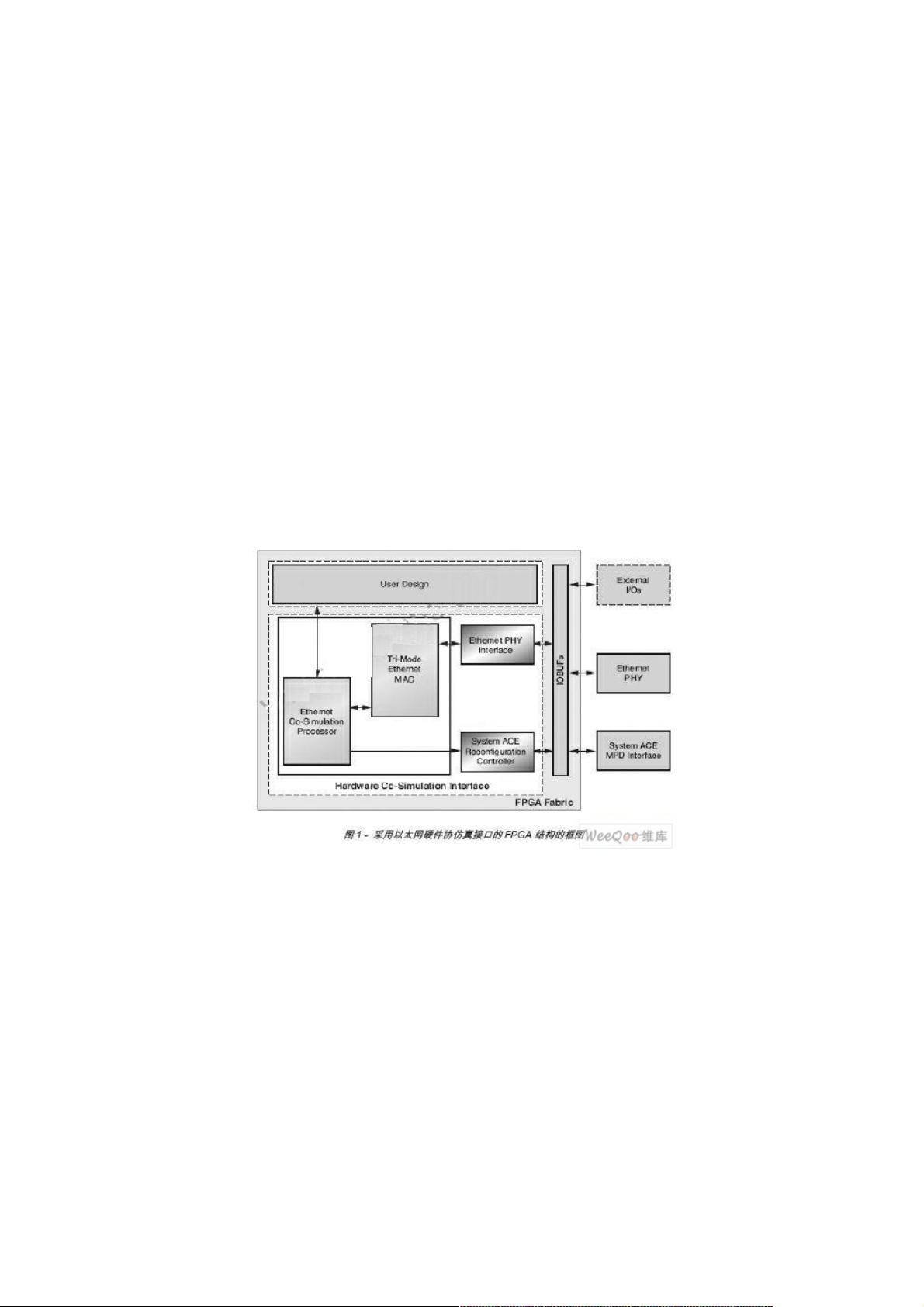

"这篇文章除了介绍Xilinx System Generator for DSP工具在FPGA设计中的应用,特别是硬件在环仿真接口的功能,还强调了以太网硬件协仿真接口的引入,为高带宽仿真提供了便利。Xilinx System Generator for DSP通过硬件在环接口加速了仿真过程,提升了效率,并允许实时的硬件调试。文中提到了不同类型的FPGA开发平台的通信方式,如JTAG和PCI总线。最新的8.1版本增加了以太网协仿真接口,使得ML402评估平台能够实现高带宽的仿真,并且可以远程通过标准以太网连接进行工作。"

文章详细介绍了在FPGA设计领域中,硬件协仿真技术的重要性。通常在开发基于FPGA的大型信号处理系统时,设计者需要进行耗时的仿真工作。Xilinx System Generator for DSP作为一款强大的FPGA设计工具,通过硬件在环接口(Hardware-in-the-Loop, HIL)解决了这一问题。HIL接口允许设计师直接将FPGA硬件集成到设计仿真流程中,极大地提高了仿真速度,甚至可以提升几个数量级,从而显著加快设计验证进程。

System Generator for DSP支持多种FPGA开发平台,它们通过各种物理接口(如JTAG、PCI总线等)与个人计算机进行通信。以JTAG为例,它是一个广泛使用的接口,适用于带有JTAG头的FPGA板卡。对于需要高存储带宽和吞吐率的系统,如视频和图像处理,过去可能需要依赖于通过PCI或PCMCIA接口的开发板进行仿真。

文章进一步指出,System Generator for DSP的8.1版本引入了一个创新的以太网协仿真接口,这是对ML402评估平台的一大增强。这个接口基于Xilinx的三态以太网MAC核,能够支持10/100/1000Mbps的半双工和全双工操作,从而提供了高带宽仿真能力。设计者现在可以通过标准以太网电缆或网络远程进行仿真,这不仅提升了仿真性能,还增强了灵活性和远程工作能力。

这篇文章揭示了FPGA设计中硬件协仿真技术的最新发展,特别是在提升仿真速度、简化调试过程以及适应高带宽需求方面。以太网协仿真接口的出现,无疑为FPGA开发者提供了一种更高效、更灵活的仿真解决方案。

2020-11-06 上传

2023-09-02 上传

2020-10-25 上传

126 浏览量

2020-12-08 上传

点击了解资源详情

2018 浏览量

点击了解资源详情

452 浏览量

weixin_38731553

- 粉丝: 4

- 资源: 899

最新资源

- nRF905射频芯片文档

- symbian入门教程(创建工程)

- 嵌入式系统C语言编程

- 某某集团员工办公应用软件操作手册.pdf

- AIX_5L_Club_TestReport.doc

- T-SQL资料(很不错)

- 高校医院管理系统需求说明书

- 利用天语A615作为调制解调器让电脑上网操作方法.doc

- CCS2000的使用说明

- Beginning JavaScript with DOM Scripting and Ajax

- 高速缓冲存储器的功能

- zxld1350的英文资料

- 2440datasheet

- ASP.net 中用C#调用Java web service 图解教程

- 计算机组成原理习题答案

- redhat as3下安装oracle 9i