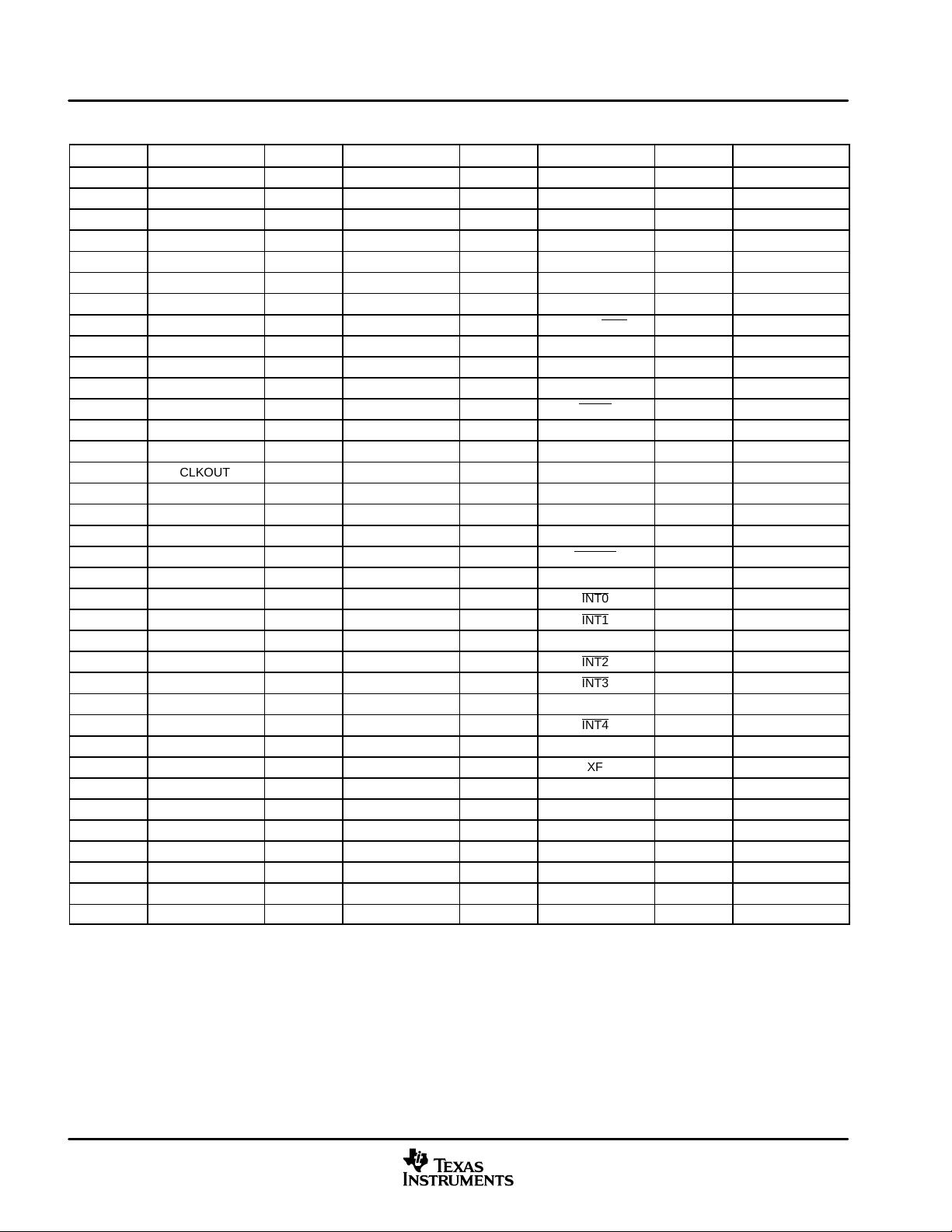

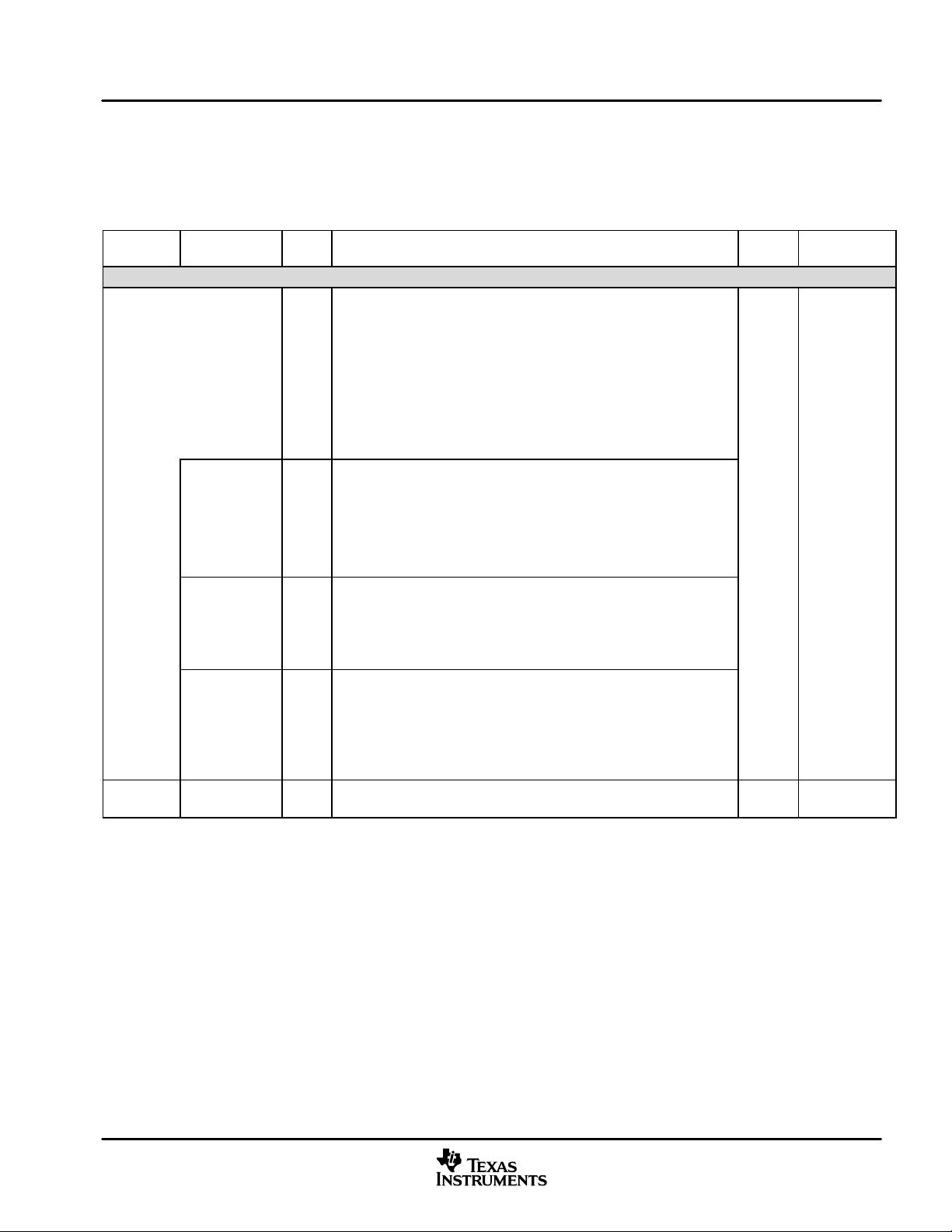

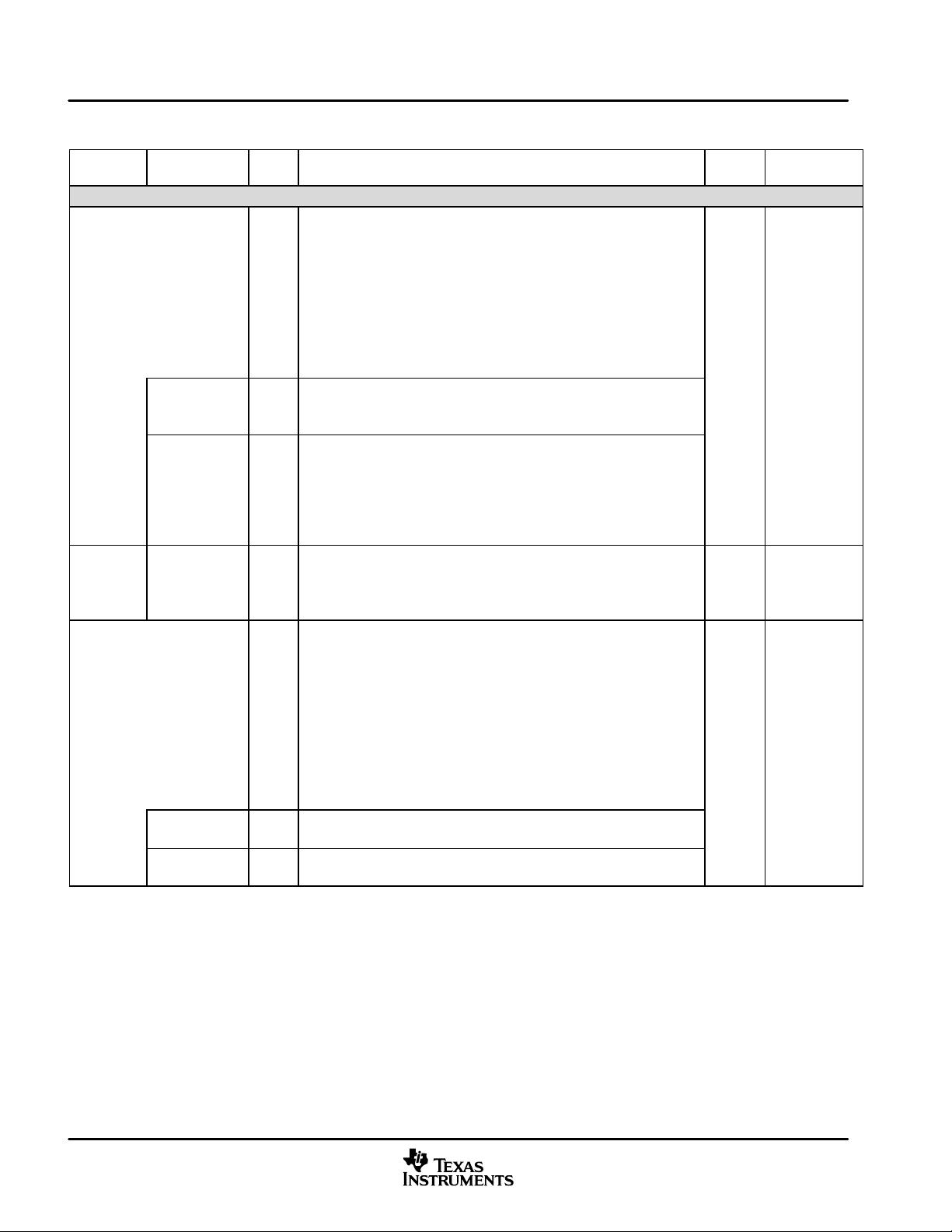

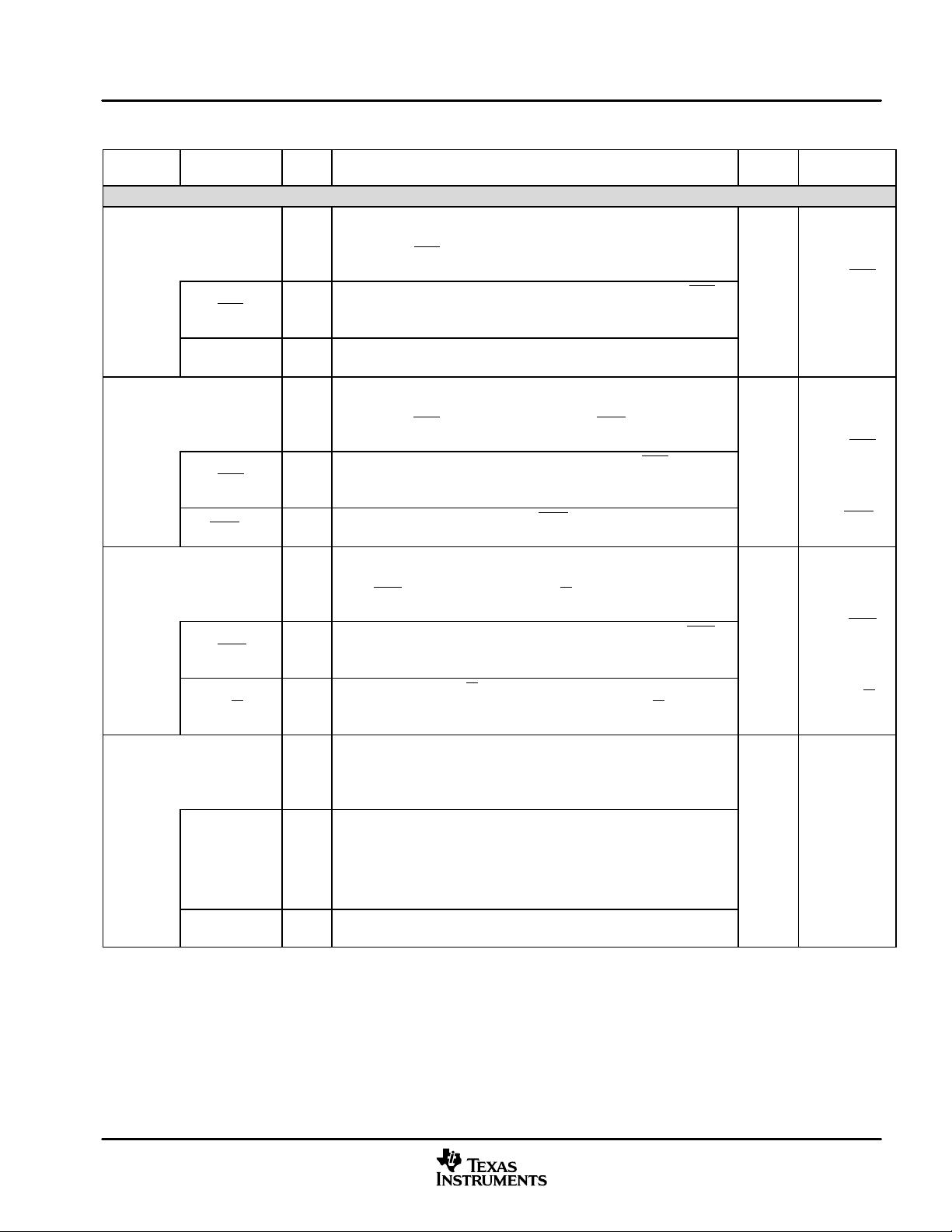

TMS320VC55x DSP 数据手册:Fixed-Point Digital Signal Processor

"TMS320VC55x系列固定点数字信号处理器数据手册,生产数据信息截至出版日期,TI保留随时对产品和服务进行修改、增强、改进或其他更改的权利,所有产品均按订单确认时的销售条款和条件出售。TI对其硬件产品的性能按照销售时适用的规格提供标准保修,使用测试和其他质量控制技术来支持此保修。" 《TMS320VC55x数据手册》是针对德州仪器(Texas Instruments, TI)开发的TMS320VC55x系列固定点数字信号处理器(DSP)的重要参考资料。该系列芯片主要用于高性能、低功耗的应用,如通信、音频处理、图像处理和工业自动化等领域。以下是手册中可能包含的关键知识点: 1. **处理器架构**:TMS320VC55x系列基于高效的VLIW(Very Long Instruction Word)架构,能够在单个时钟周期内执行多个操作,提高了处理效率。 2. **指令集**:手册会详细介绍该系列DSP的指令集,包括基本操作、浮点运算、乘法累加(MAC)、分支和循环控制等。 3. **存储器组织**:手册会描述处理器的内部存储结构,包括数据存储器(Data Memory)、程序存储器(Program Memory)以及各种寄存器的布局和功能。 4. **外围接口和外设**:TMS320VC55x可能包含多种外设接口,如串行端口、定时器、DMA控制器等,这些外设的使用方法和配置在手册中会详述。 5. **电源管理**:手册会涵盖芯片的电源管理特性,如动态电压和频率调整(DVFS),以适应不同应用的功耗需求。 6. **开发工具和软件支持**:手册可能提及TI提供的开发工具链,如编译器、调试器和实时操作系统(RTOS)支持。 7. **硬件设计和应用示例**:对于系统设计者,手册会提供电路设计指导,包括封装信息、引脚配置、电气特性以及应用电路示例。 8. **性能指标**:手册会列出处理器的性能指标,如工作频率、计算能力、功耗等,以帮助设计者评估其在特定应用中的表现。 9. **错误检测和纠正**:手册可能包括错误检测和纠正机制,如奇偶校验位、ECC等,以提高系统可靠性。 10. **标准保修和责任声明**:TI在手册中明确指出,产品性能符合销售时的标准规格,并提供保修服务。但同时提醒客户在下单前验证信息的最新性和完整性。 TMS320VC55x数据手册是开发者和工程师理解、设计和优化基于该处理器系统的核心资源,它提供了全面的技术细节和操作指南,以确保高效、稳定地利用该DSP平台进行系统开发。

剩余119页未读,继续阅读

- 粉丝: 0

- 资源: 1

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

最新资源

- C语言快速排序算法的实现与应用

- KityFormula 编辑器压缩包功能解析

- 离线搭建Kubernetes 1.17.0集群教程与资源包分享

- Java毕业设计教学平台完整教程与源码

- 综合数据集汇总:浏览记录与市场研究分析

- STM32智能家居控制系统:创新设计与无线通讯

- 深入浅出C++20标准:四大新特性解析

- Real-ESRGAN: 开源项目提升图像超分辨率技术

- 植物大战僵尸杂交版v2.0.88:新元素新挑战

- 掌握数据分析核心模型,预测未来不是梦

- Android平台蓝牙HC-06/08模块数据交互技巧

- Python源码分享:计算100至200之间的所有素数

- 免费视频修复利器:Digital Video Repair

- Chrome浏览器新版本Adblock Plus插件发布

- GifSplitter:Linux下GIF转BMP的核心工具

- Vue.js开发教程:全面学习资源指南

信息提交成功

信息提交成功