FPGA时序设计揭秘:关键概念与实战经验

需积分: 10 55 浏览量

更新于2024-08-02

收藏 1.07MB PDF 举报

"FPGA经验总结,重点探讨了FPGA/CPLD数字电路设计中的时序设计、建立时间、保持时间以及竞争和冒险现象,旨在提供有效的设计策略和实践经验。"

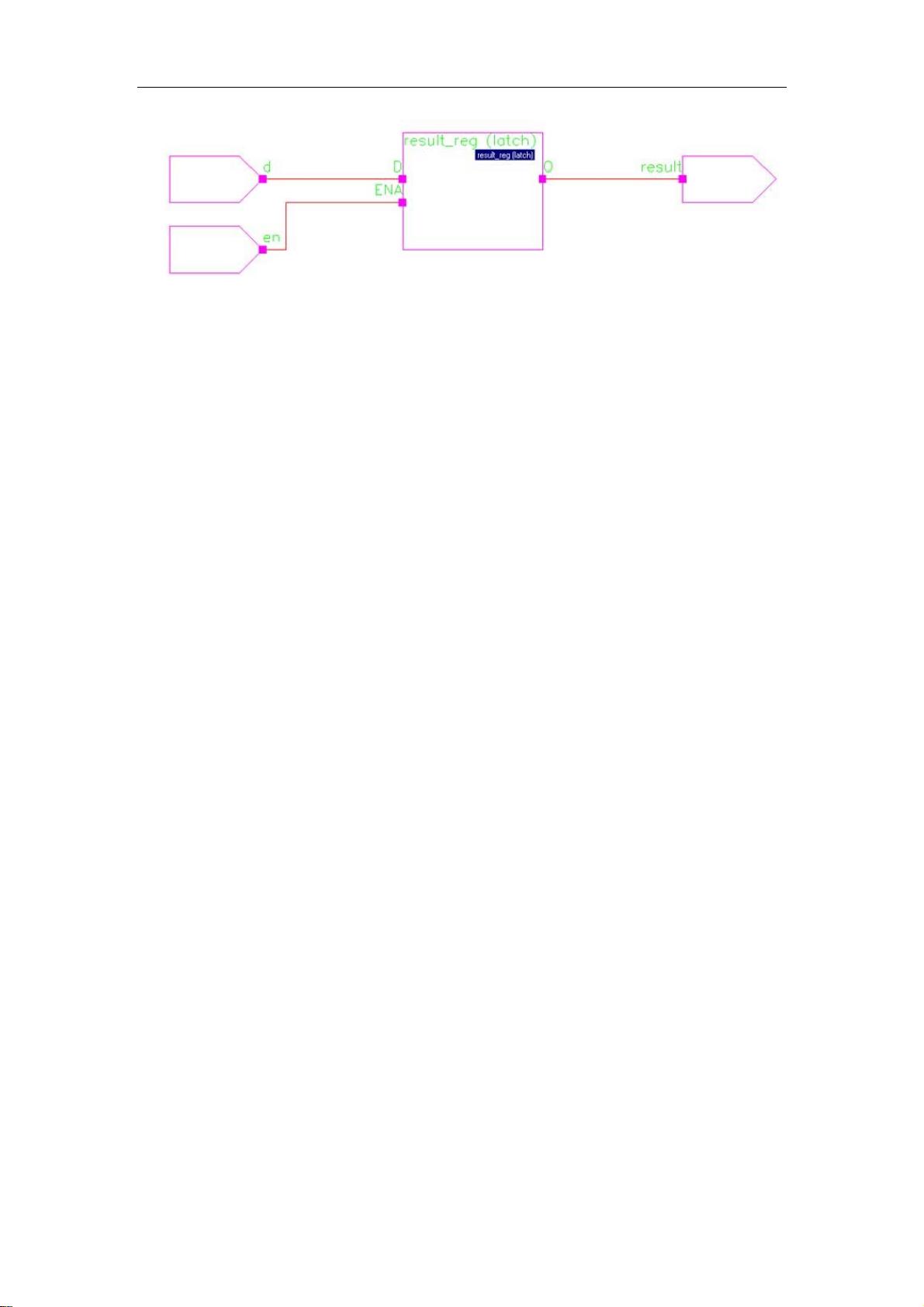

在数字电路设计中,FPGA(Field-Programmable Gate Array)和CPLD(Complex Programmable Logic Device)是实现高速、高性能系统的关键技术。本文的核心在于时序设计,这是衡量系统性能的关键指标。时序设计涉及到建立时间和保持时间,这两个参数直接影响着数据能否正确地被触发器捕获。

1. 建立时间和保持时间是数字设计中的关键概念。建立时间是指数据在时钟边沿到来前需要保持稳定的时间,而保持时间则是在时钟边沿之后数据必须保持不变的时间。如果这两个时间不足,可能会导致数据丢失或错误。在FPGA设计中,软件工具通常能自动计算输入间的建立和保持时间。设计时,应确保在不同时钟频率下,系统都能满足这些时间限制。

2. 在高频时钟系统中,如果建立时间过紧,降低时钟频率可以改善问题。然而,保持时间并不依赖于时钟周期,如果设计不当,可能导致即使调整时钟频率也无法解决问题,可能需要对设计进行大幅度修改。因此,合理规划时序对于提升设计质量至关重要。

3. FPGA中的竞争和冒险现象是另一个需要注意的问题。由于信号传播的延迟和转换时间,当多个路径同时改变状态时,可能出现短暂的不确定状态,这可能导致输出错误。避免竞争和冒险的方法包括优化逻辑设计、使用同步电路和添加适当的同步元素。

4. 在FPGA设计实践中,除了理解和掌握理论知识外,还需要结合具体的设计工具,例如使用VHDL进行硬件描述语言编程,以及使用Synthesis工具进行逻辑综合和Place & Route工具进行布局布线。理解这些工具如何处理时序约束,以及如何优化逻辑以减少延迟,是提高设计效率和成功率的关键。

5. 设计实例和经验分享对于深入理解和应用这些知识至关重要。通过实际案例,设计师可以更好地学习如何在设计过程中平衡速度、面积和功耗,以及如何解决出现的时序问题,从而提升FPGA/CPLD设计的成熟度和成功率。

FPGA/CPLD数字电路设计是一门涉及多方面知识和技巧的复杂艺术。深入理解时序设计原则,熟练掌握建立和保持时间的管理,以及有效地应对竞争和冒险现象,是成为一个成功的FPGA设计师的必备技能。通过不断的学习和实践,设计师可以逐步积累经验,优化设计方案,以达到更高的设计质量和性能。

2010-03-17 上传

153 浏览量

129 浏览量

112 浏览量

409 浏览量

点击了解资源详情

1216 浏览量

184 浏览量

132 浏览量

麦兜兜_qishiyi

- 粉丝: 3

- 资源: 11

最新资源

- node-shopping-cart

- platzi-store-backend

- 小企业考勤表excel模版下载

- 宽敞阳光3D客厅模型设计

- upptime:Christ Christopher Demicoli的正常运行时间监控器和状态页面,由@upptime提供支持

- Colormix:将基本颜色与字符串语法相结合以创建任何 RGB 颜色。-matlab开发

- 在16x2 LCD显示屏上创建自定义动画-项目开发

- 舒适室内家装模型

- 值班表excel模版下载

- shortuuid:PHP 7.3+库可生成简洁,明确,URL安全的UUID

- laravel-webp

- uri-online-judge:ResoluçãodasQuestões做URI在线法官

- Unity ads demo

- dogify:帮助狗化网络!

- btech_cse_sem_4-material_-2021-MRU

- 超市进出货管理流程excel模版下载