VHDL实现八人抢答器:编码解码与时间控制

本篇文档详细介绍了用VHDL编程技术设计的一款八人抢答器系统。设计的主要目标是创建一个可以容纳8名选手的抢答器,每个选手都有自己的抢答按钮,以及一个主持人控制的开关。系统的关键组成部分包括编码器、译码器、计时器和报警器。

1. 设计任务要求:

- 抢答器需支持8个独立选手编号,从1到8,各自拥有一个按钮,按下的选手将通过编码器转换为8421BCD码,显示在数码管上并触发报警。

- 主持人控制开关负责清零抢答状态和启动抢答过程。

- 抢答过程中,一旦有人按下按钮,抢答者的编号将被锁存并持续显示,直至主持人清零。

- 提高要求部分,设计了一个倒计时计时器,如果规定时间内无人抢答,系统会发出报警,数码管显示0号。

2. 设计流程:

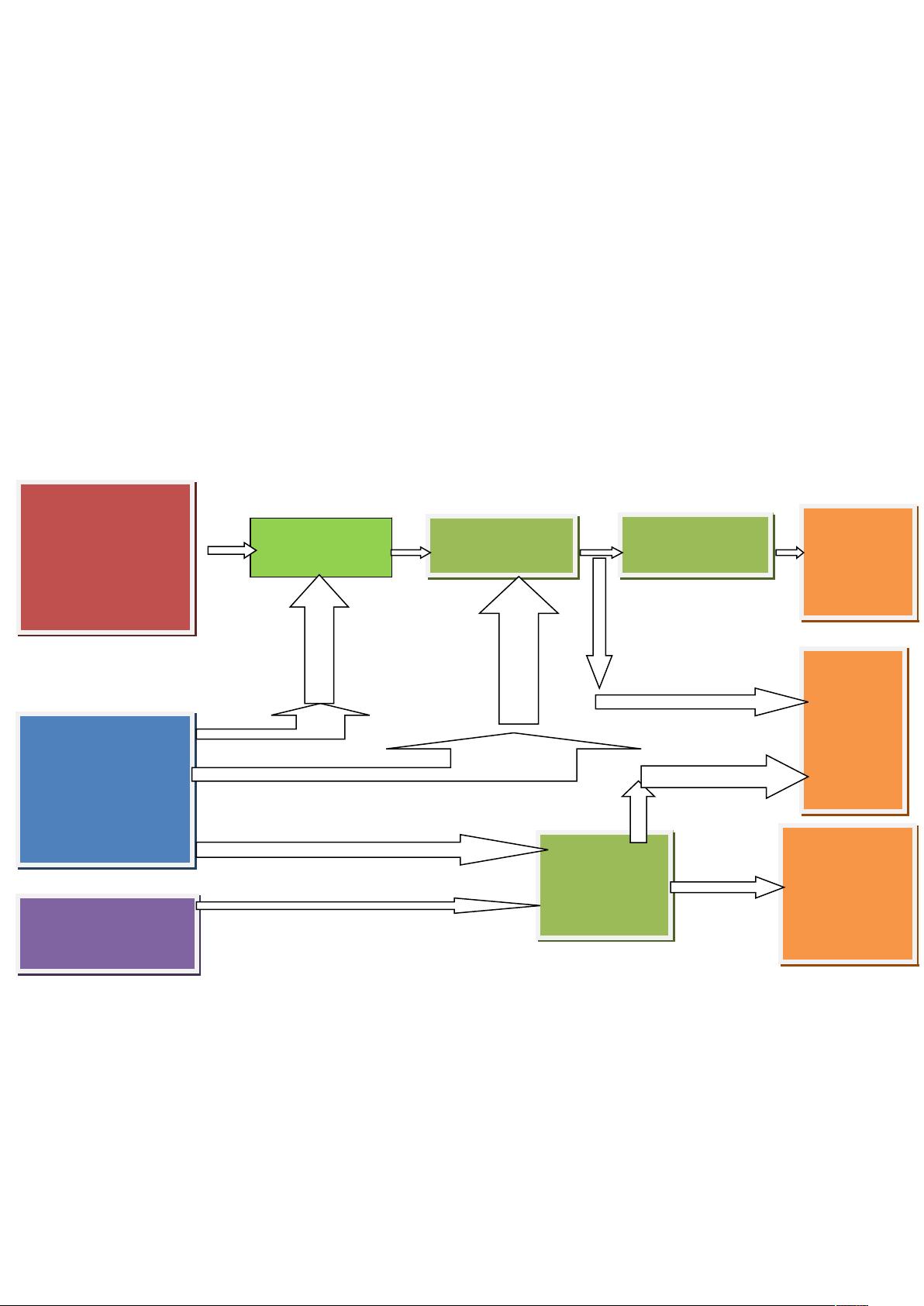

- 设计模块方框图:展示了整个系统的模块化结构,包括选手按钮电路、编码器、锁存器等关键组件的连接和交互。

- 模块功能分析:

- 参赛选手按钮电路:每个选手按钮连接到常开开关,抢答时开关断开,输入低电平信号。

- 编码器:负责将选手的开关状态转换成可识别的数字代码,以便于数码管显示。

- 锁存器:接收抢答信号后,锁存并保持该选手的编号,防止其他选手干扰。

3. 电路设计:

- 系统封装图:展示了硬件电路的整体布局和连接方式。

- VHDL文本输入语言:详细描述了各个模块的VHDL代码实现,包括逻辑门电路、触发器等元件的编程。

- 封装图和仿真波形:提供了实际电路的图形表示和各模块在不同工作状态下的信号行为。

4. 设计总结:

- 反馈了整个设计过程中的挑战、解决方案以及最终产品的性能评估。

5. 参考文献:列出了完成本项目所参考的相关技术资料和理论基础。

本文档通过深入剖析各个模块的功能和实现细节,为读者提供了一个完整的VHDL编程设计案例,适用于学习和理解如何用VHDL构建一个实际的抢答器系统。

2018-08-06 上传

2009-09-02 上传

2022-09-19 上传

2018-07-04 上传

点击了解资源详情

2023-05-25 上传

2022-09-21 上传

2022-09-20 上传