Cyclone FPGA PLL详解:功能、应用与设计指南

需积分: 10 100 浏览量

更新于2024-08-02

收藏 924KB DOC 举报

Cyclone FPGA是Altera公司的一款高性能可编程逻辑器件,其内部集成了一种先进的锁相环(PLL,Phase-Locked Loop)模块。PLL在数字电路设计中扮演着关键角色,它能够将输入的参考时钟同步到内部电路,实现时钟倍频、分频、相位偏移和可编程占空比等功能,从而优化系统性能并确保时钟信号的稳定性和准确性。

PLL硬件结构包含多个组件,如相位频率检测器(PFD,Phase Frequency Detector)和电压控制振荡器(VCO,Voltage-Controlled Oscillator)。PFD负责检测参考时钟与反馈时钟之间的相位差,并通过比较产生误差信号,驱动VCO调节自身的频率,以达到锁相的目的。VCO则根据PFD的输出调整,以产生所需频率的时钟输出。

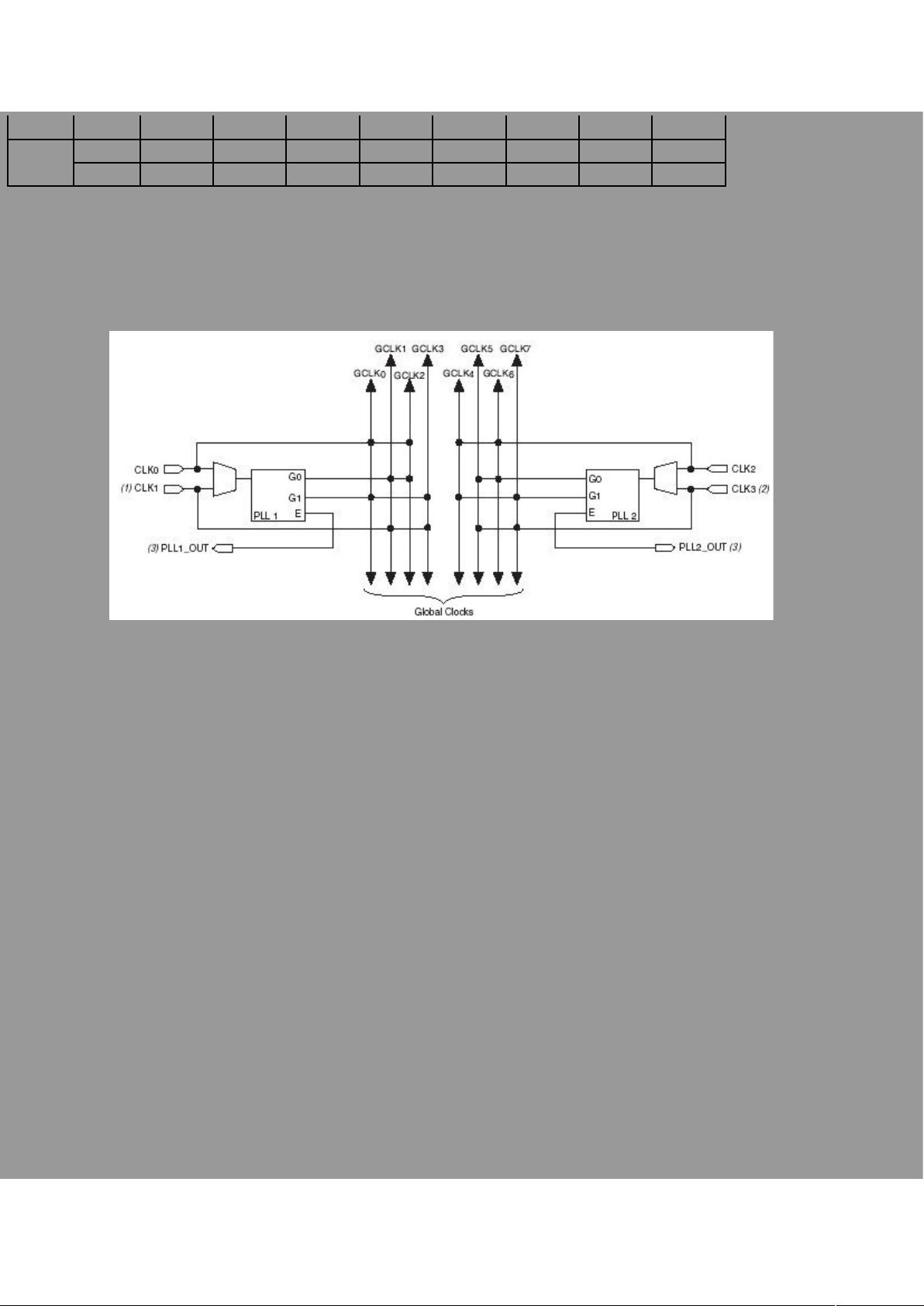

Cyclone PLL的设计灵活,支持多路时钟输出,每个PLL最多有两个内部时钟输出和一个外部时钟输出,这使得设计师可以根据应用需求选择合适的配置。例如,M/(N×后scale计数器)机制允许对时钟频率进行精确的调整,最小相位偏移可达156皮秒,这对于减少时钟延迟和保持系统时序一致性至关重要。

在使用Cyclone PLL时,可以通过Altera Quartus II软件进行便捷的配置和实现。软件提供了MegaWizard定制功能,帮助用户快速设置PLL参数,而无需额外的外部元件。同时,时序分析工具能够评估PLL对整个设计时序的影响,确保系统的可靠运行。

在实际的板级设计中,Cyclone PLL的锁定端口可以与逻辑阵列相连,以便于将PLL产生的时钟信号分配到各个模块。此外,不同的Cyclone FPGA型号可能有不同的PLL配置,比如100脚TQFP封装的EP1C3不支持某些特定的PLL输出类型,用户需注意选择适合的设备。

总结来说,Cyclone FPGA中的PLL功能强大且易于使用,对于需要精细时钟管理的系统来说,它是提高性能、减少噪声和提高整体系统稳定性的重要手段。通过理解其工作原理和配置方法,设计者能够充分利用这一特性来优化他们的FPGA设计。

2012-03-19 上传

2022-08-04 上传

294 浏览量

点击了解资源详情

点击了解资源详情

284 浏览量

2022-08-04 上传

yixiaman

- 粉丝: 0

- 资源: 1

最新资源

- ttysgym

- Design_Patterns

- 蓝桥杯嵌入式练习题——“电子定时器”的程序设计与调试*代码.zip

- Deeper.dmg.zip

- PlotFilter / 滤波器系数文件:PlotFilter 绘制滤波器响应。 过滤器文件包括 ITU-T 过滤器和 QMF 过滤器。-matlab开发

- rs-popover:佳能弹出式视窗的Angular指令

- 电子功用-家庭能量动态分配路由器、方法及家庭能量发电计划方法

- pitches:这是一个网络平台,允许用户查看,提交和评论一分钟音高的各种类别。此站点允许用户查看各种音高并明智地使用它们,因为仅需一分钟即可打动他人

- 玩hangmangame

- UserPrefs2020.rar

- binary_trees:关于二叉树结构的项目

- Resume-Builder-Web-Application

- 第八届 蓝桥杯嵌入式设计与开发项目决赛——频率控制器的功能设计与实现·代码.zip

- GFH:使bepo-xxerty定制键盘在GitHub上工作

- google-drive-cleaner:用于删除Google云端硬盘中文件的工具

- k8s:Hello world k8s