An Ultra Low Power Non-volatile Memory

in Standard CMOS Process for Passive RFID Tags

Peng Feng, Yunlong Li, and Nanjian Wu*

Institute of Semiconductors, Chinese Academy of Sciences, Beijing 100083, China;

*nanjian@red.semi.ac.cn

Abstract-An ultra low power non-volatile memory is designed

in a standard CMOS process for passive RFID tags. The memory

can operate in a new low power operating scheme under a wide

supply voltage and clock frequency range. In the charge pump

circuit the threshold voltage effect of the switch transistor is

almost eliminated and the pumping efficiency of the circuit is

improved. An ultra low power 192-bit memory with a register

array is implemented in a 0.18μM standard CMOS process. The

measured results indicate that, for the supply voltage of 1.2 volts

and the clock frequency of 780KHz, the current consumption of

the memory is 1.8μA (3.6 μA) at the read (write) rate of

1.3Mb/s (0.8Kb/s).

I. INTRODUCTION

The rapid growth of electronic circuits such as hardware

encryption circuits, radio frequency identification (RFID) tags,

and analog trimming circuits is driving the need for small size

of embedded non-volatile (NV) memory. However, the typical

EEPROM or FLASH memory requires additional masks and

process steps so that a small size of embedded NV memory

results in the whole system chip must bear the additional cost.

So the ultra low power NV memory in standard CMOS

process receives much attention in recent years. A single poly

EEPROM cell was proposed, in which FN tunneling

phenomenon is employed to program/erase (P/E) the state of

the memory cell [1]. An embedded flash memory was

reported in [2]. Each bit cell includes a high voltage switch

and a SRAM data-latch. However, it suffers from large power

consumption. When a passive UHF RFID tag operates, its

supply voltage and clock frequency varies widely with the

configuration of the reader and tag, so the regulation circuit

and charge pump circuit are necessary to keep the supply

voltage stable and to generate the high voltage for the bit cell

programming. The area and power of these circuits usually

take up a large proportion of the chip [3]. Some attempts have

been made to improve the performance of the charge pump

circuit [4, 5]. However, the stage gain is still lower than the

supply voltage.

This paper presents an ultra low power NV memory with a

high efficiency charge pump circuit and a register array in a

0.18μm standard CMOS process for passive RFID tags. The

memory can be operated in a new operating scheme under a

wide supply voltage and clock frequency range. In the charge

pump circuit the influence of the threshold voltage of the

switch transistor is almost eliminated and the pumping

efficiency of the circuit is improved. In section II, the memory

circuits and operation principles are introduced. In section III,

the implementation and test results of the memory are given.

Finally, a conclusion is given in section IV.

II. M

EMORY CIRCUITS AND OPERATION PRINCIPLES

A. The Architecture of the Memory

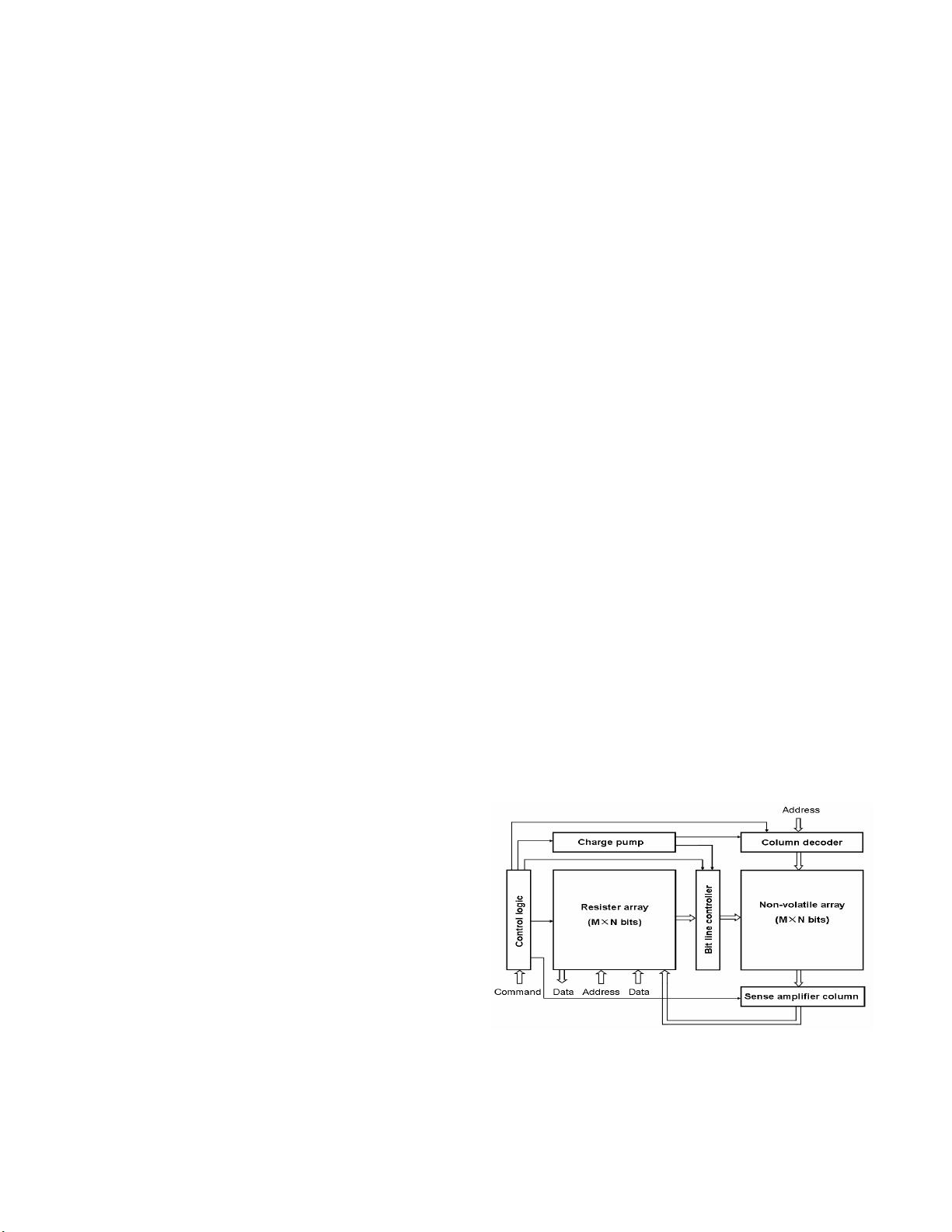

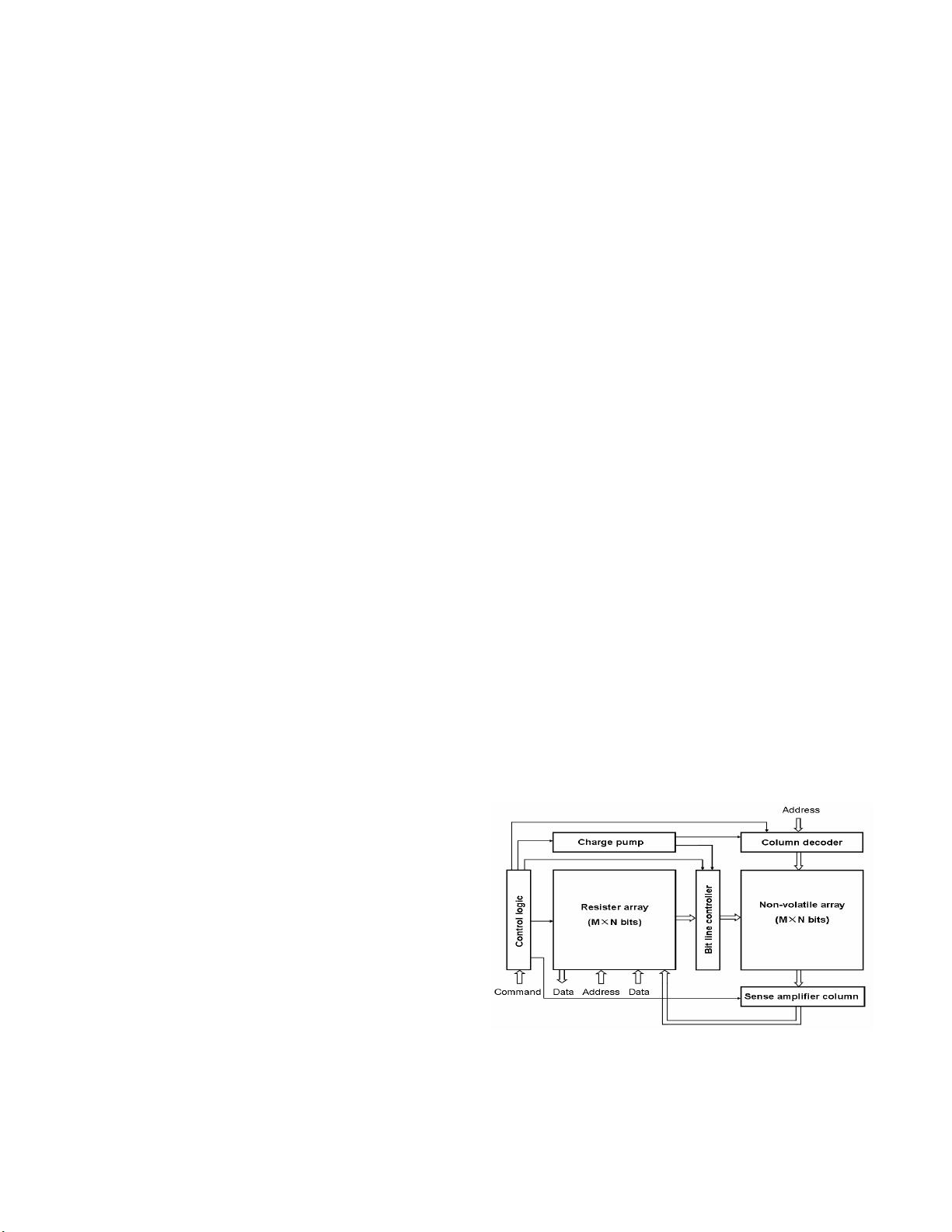

The architecture of the memory is shown in Fig.1. It

consists of a NV cell array, a bit line controller, a column

decoder, a sense amplifier column, a charge pump, a register

array and the control logic module. The control logic module

manages the operation of the blocks. The bit line controller

controls the write operation of the NV memory. The column

decoder selects the active column. The sense amplifiers detect

the outputs of the active-column cells in read operation. The

charge pump generates a high voltage and a medium voltage

in write operation. The size of the NV memory is equal to that

of the register array. Each N-bit word in the NV cell array

corresponds to N-bit word in the register array. The data in the

NV array are first loaded into the register array for the

subsequently read operation which is both faster and

consumes much less power.

B. The Bit Cell and Operation Principles

Fig. 2 shows the schematics of the bit differential cell and

the sense amplifier. The bit cell consists of coupling

capacitors C

c1

and C

c2

and FN tunneling junctions M

1

, M

2

, M

3

,

M

4

. C

c1

, M

1

and M

3

(C

c2

, M

2

and M

4

) are interconnected

through common floating poly F (F_n). FN tunneling

phenomenon with small current density is used to perform

ultra low power P/E operations. The electrons can tunnel

through M

1

and M

2

to inject into the floating gates F and F_n

and through M

3

and M

4

to depart from the floating gates. In

Read mode, M

1

and M

2

also act as read transistors. The

capacitances of C

c1

and C

c2

are much larger than that of

tunneling junctions, so the bias voltages on C

c1

and C

c2

can

control the voltages of the floating gates. A large electric field

across the junctions can be established by biasing the nodes

Fig.1. The architecture of the memory

713

IEEE 2009 Custom Intergrated Circuits Conference (CICC)

978-1-4244-4072-6/09/$25.00 ©2009 IEEE 24-4-1

Authorized licensed use limited to: INSTITUTE OF SEMICONDUCTORS CAS. Downloaded on April 13,2010 at 03:35:33 UTC from IEEE Xplore. Restrictions apply.