H.264在ADSP-BF561上的DSP实现与优化

7 浏览量

更新于2024-08-31

收藏 251KB PDF 举报

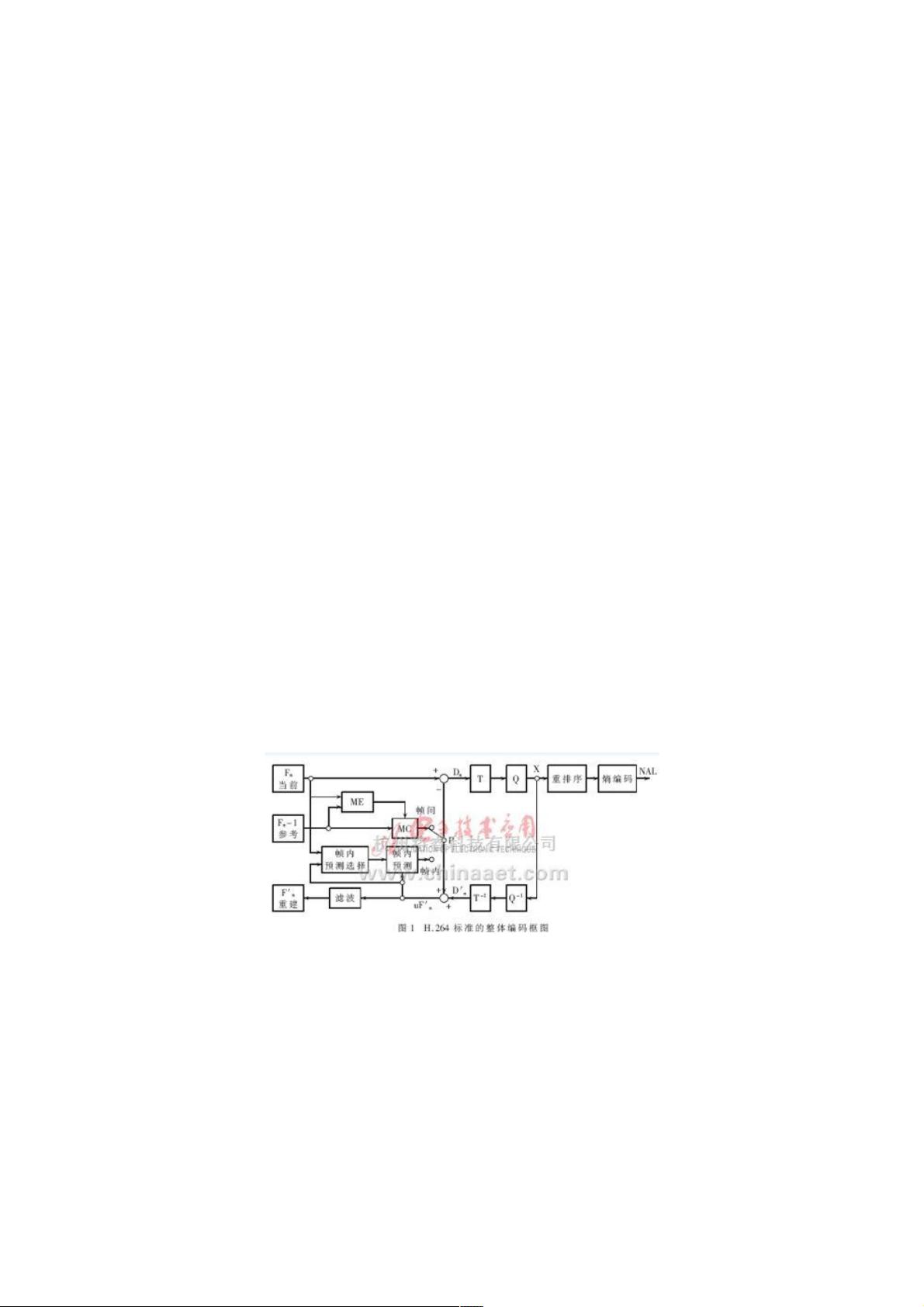

"本文详细探讨了H.264视频编码标准在ADSP-BF561数字信号处理器上的实现和优化。随着互联网和移动通信的快速发展,对视频编解码技术的需求日益增长,H.264/AVC作为新一代视频编码标准,因其高效的编码效率和网络适应性而备受关注。相较于MPEG-4,H.264能提供更高的压缩率,同时具备在移动环境下对抗数据丢失和错误的能力。

H.264的编码模型框架包括基于块的混合编码,它整合了帧内预测、运动补偿、熵编码等多种技术,以提高压缩性能。然而,这种复杂性也带来了计算量的增加,对实时编解码器提出了挑战。ADSP-BF561由ADI公司设计,拥有双核处理单元和高速时钟频率,能够满足高性能实时编码的需求。

文章提出了一种利用ADSP-BF561实现H.264压缩算法的策略,并针对该DSP平台对算法进行了优化。通过充分利用其硬件特性,如哈佛总线结构和层次化存储模型,可以有效地加速编码过程,确保在限制的资源下实现高效运行。

1.2 ADSP-BF561优化策略

为了在ADSP-BF561上高效执行H.264编码,可能的优化策略包括:

- 并行处理:利用双核结构,将编码过程的不同阶段分配给两个核心,以平行执行。

- 内存访问优化:通过预加载和缓存数据,减少不必要的内存访问,提高速度。

- 算法重构:重新设计某些计算密集型部分,如运动估计和量化过程,以减少计算复杂度。

- 位操作优化:利用DSP硬件对位操作的优化特性,提高编码效率。

- 流水线设计:通过流水线技术,使得每个处理步骤在前一个步骤完成后立即开始,减少空闲时间。

通过这些优化,可以在满足实时性的前提下,最大限度地发挥ADSP-BF561的潜能,实现高质量的H.264视频编码。

此外,文章还可能涵盖了错误恢复机制、网络适应性以及在实际应用中的性能评估等方面,全面阐述了H.264在ADSP-BF561上的实现细节和优化方法,对于理解高性能DSP在视频编码领域的应用具有重要的参考价值。"

点击了解资源详情

点击了解资源详情

105 浏览量

2022-09-21 上传

2022-09-24 上传

2022-09-24 上传

2020-10-19 上传

150 浏览量

2022-09-19 上传

weixin_38598613

- 粉丝: 7

- 资源: 914

最新资源

- 微信小程序-点餐

- ionicStudyWithTabs:带有 ngCordova 的离子模板项目

- note-taker

- XIANDUAN.rar

- 一种基于高通量测序的拷贝数变异检测自动化分析解读及报告系统.rar

- rasaxproject1

- GitHub Open All Notifications-crx插件

- gatsby-remark-component-images:一个Gatsby注释插件,将gatsby-plugin-sharp处理应用于html样式的markdown标签

- 易语言开关音频服务实现开关声音-易语言

- ComposeKmmMoviesApp

- HistogramComponentDemo.7z

- UA GPU-able Search-crx插件

- MYSQL数据库管理器(易语言2005年大赛三等奖)2010-10-27.rar

- native-api-notification-[removed]JavaScript中的本机通知API

- 将超像素作为输入MATLAB代码-laplacianseg:种子图像分割的拉普拉斯坐标

- MyDroid