优化设计:三阶一位量化Σ-Δ调制器的CIFB结构

需积分: 10 69 浏览量

更新于2024-08-26

2

收藏 1.73MB PDF 举报

"该文提出了一种基于MATLAB SIMULINK的三阶一位量化连续时间积分器反馈滤波器(Continuous-Time Integrator Feedback Filter, CIFB)结构的Σ-Δ调制器设计方法,采用256倍过采样率,优化了噪声传输函数的零极点和系统反馈系数,以提升系统稳定性和降低模拟电路设计复杂度。在考虑实际电路中的非理想因素如积分器的直流增益限制、饱和电压、压摆率和增益带宽后,实现了SNDR (Signal-to-Noise and Distortion Ratio)为123 dB和ENOB (Effective Number of Bits)为20.14 bits的高性能指标。此设计展示了在低量化位数下也能达到高精度和稳定性的可能性,对高层次的晶体管级电路设计有指导意义。"

Σ-Δ调制器是一种常用的模拟数字转换器(ADC),尤其适用于音频处理、ISDN、电子测量和数字录像等中低频应用。其主要优点在于能提供高分辨率、高性价比和低功耗。调制器的核心机制是过采样技术和噪声整形,通过提高采样率将噪声推向高频区域,从而提高信噪比。

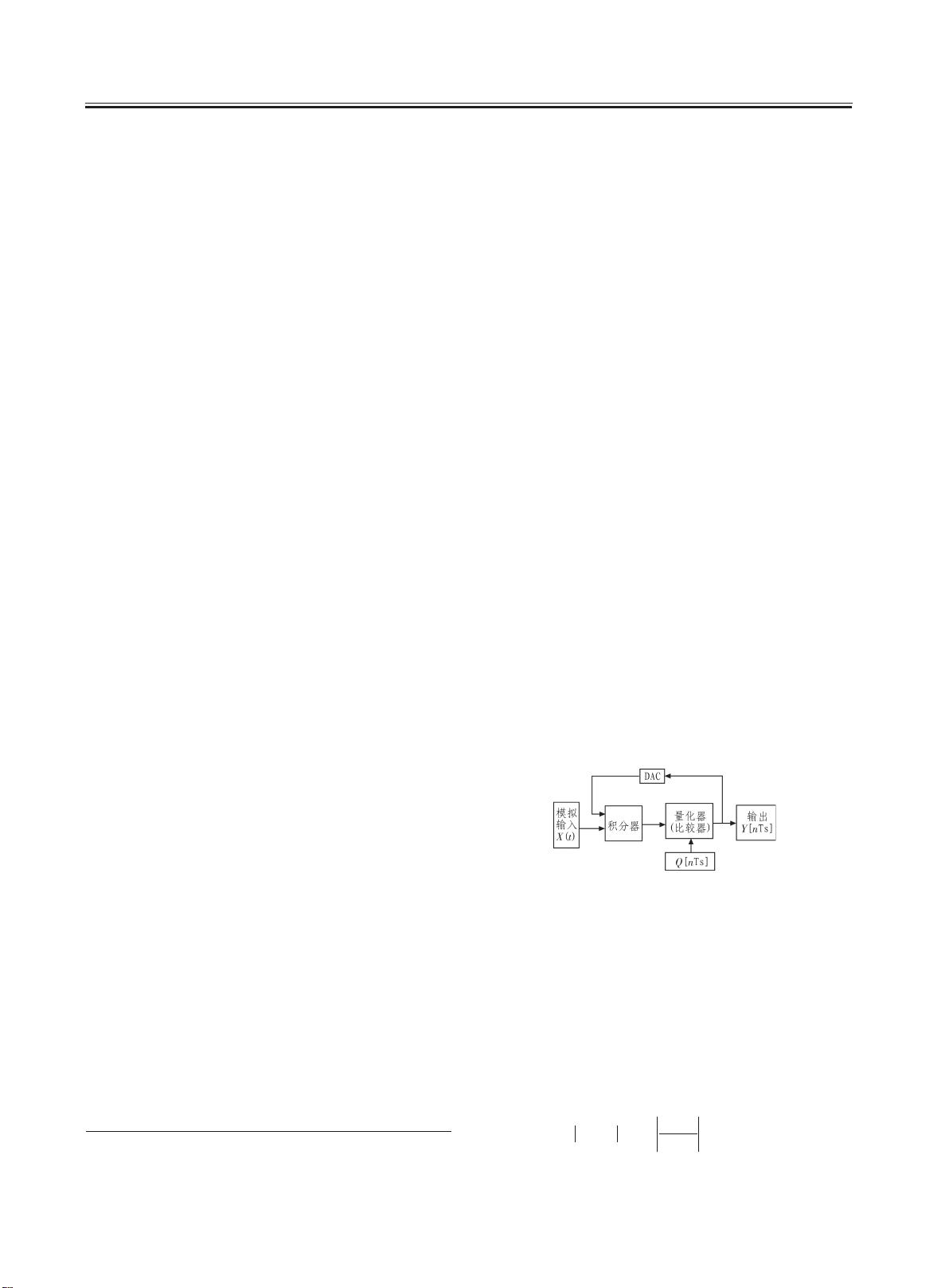

文中提出的单环三阶CIFB结构调制器,相较于二阶多位量化和三阶级联结构,具有更简单的电路设计和较少受到非理想因素的影响。一阶调制器通常包含模拟输入采样、积分器、一位量化噪声比较器和反馈数模转换器(DAC)四个部分。在三阶结构中,通过增加反馈级数,可以进一步提升系统的噪声性能。

设计过程中,优化噪声传输函数的零极点布局和反馈系数是为了改善系统的动态性能,这有助于减少噪声对信号的影响。同时,考虑到积分器的实际特性,如有限直流增益可能导致的信号失真,饱和电压可能限制信号范围,压摆率影响转换速度,以及增益带宽决定系统的频率响应,这些因素都需要在建模时予以考虑。

在MATLAB/SIMULINK环境下进行系统建模,能够方便地模拟和分析调制器的性能,为实际电路设计提供理论依据。通过仿真,该设计达到了SNDR 123 dB和ENOB 20.14 bits,这表明即使在一位量化的情况下,也能实现高精度的转换效果,且系统的稳定性良好。

这种设计方法对于简化模拟电路设计流程,提高Σ-Δ调制器的性能,特别是在晶体管级电路设计阶段提供了有价值的指导,有助于实现高性能、低成本的ADC解决方案。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2021-01-27 上传

119 浏览量

2023-02-25 上传

2021-03-14 上传

2024-12-26 上传

weixin_38632247

- 粉丝: 8

- 资源: 1000