"CADENCE ALLEGRO是一款广泛应用于半导体封装设计的软件工具,其基于Wirebond (WB)方式的操作流程涉及到从封装创建、规则设定、原理图导入、布局布线到设计优化、自检及最终输出等多个步骤。本操作流程详细介绍了如何在CADENCE ALLEGRO中进行WB封装设计。"

在CADENCE ALLEGRO中,基于WB方式的软件操作流程主要包括以下几个关键环节:

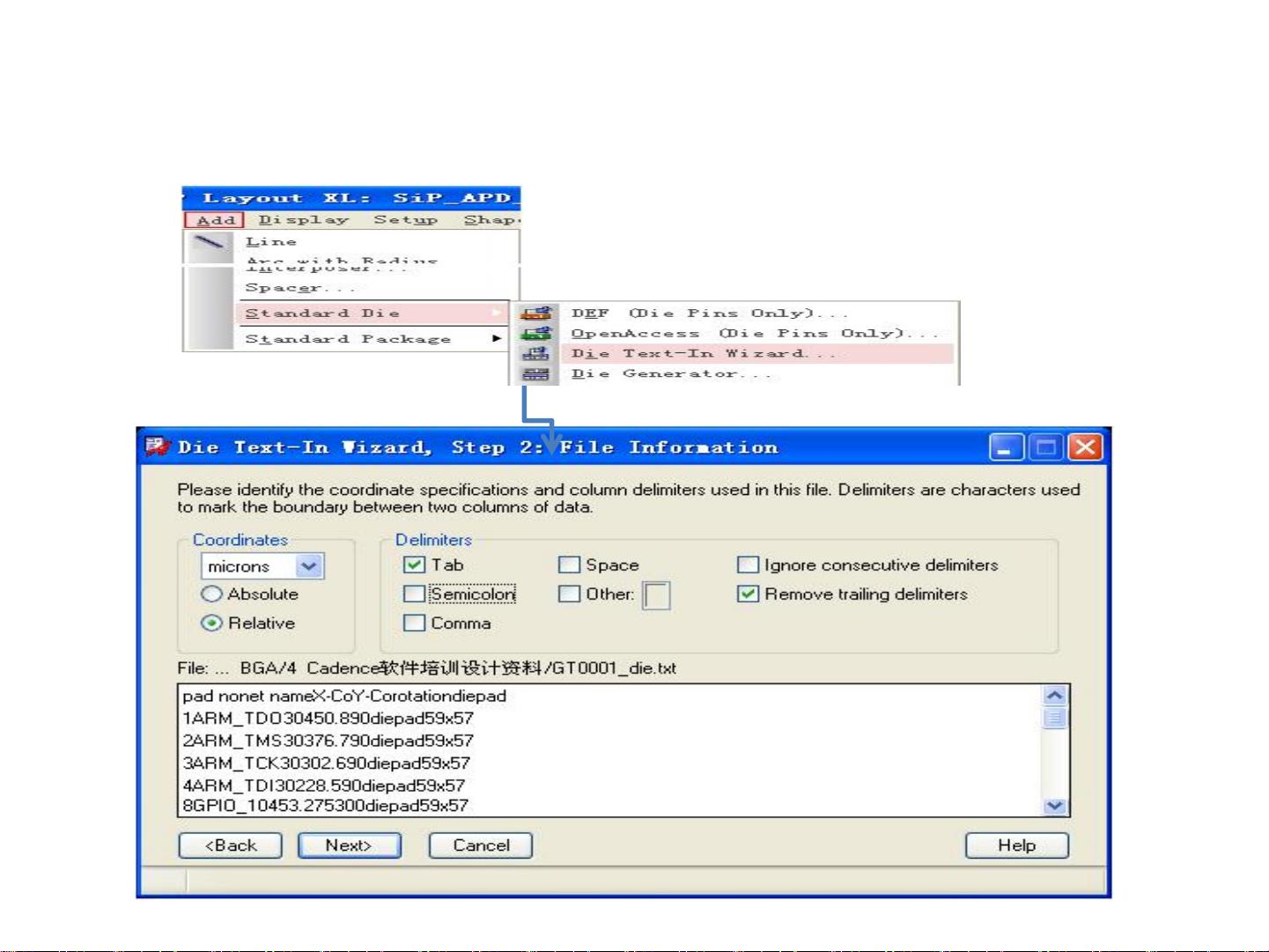

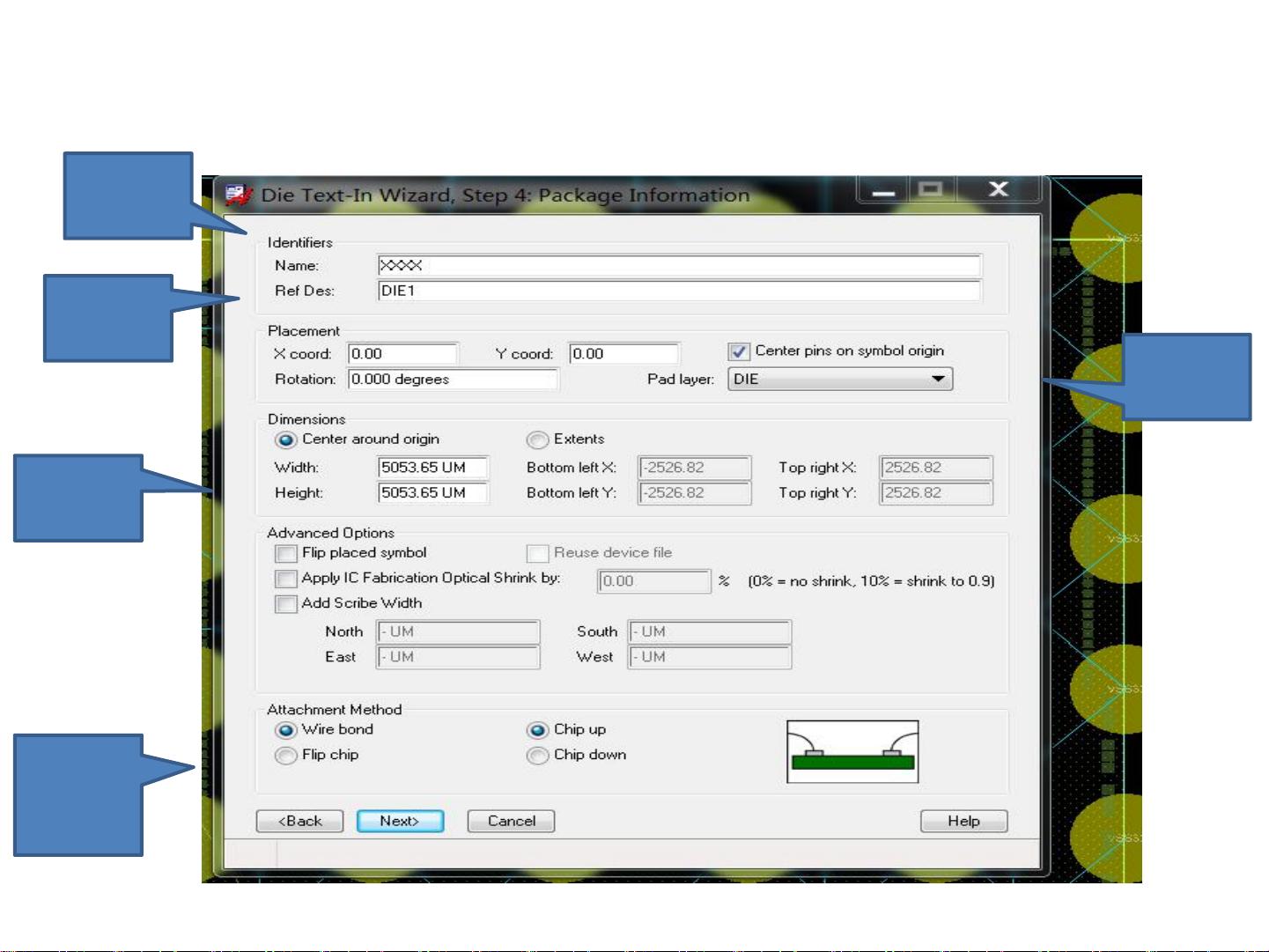

1. **制作DIE或BGA封装**:

- 根据客户提供的信息,如芯片尺寸、连接关系等,制作DIE或BGA封装。在创建封装时,需要确保NETNAME的对应正确,并处理好小数点问题,通常用"P"代替。

2. **导入原理图**:

- 如果客户提供了原理图,将其转换为ALLEGRO可识别的网表格式并导入。这一步是设计的基础,确保了电气连接的准确性。

3. **设置Wirebond规则**:

- 对bondpad的尺寸、bondwire线径以及打线方式进行规则设定,这些参数直接影响到封装的可制造性和成本。

4. **设置constrains**:

- 定义设计约束,如电气间距、最小线宽、过孔大小等,以确保设计符合工艺规范。

5. **布局**:

- 在die放置阶段,根据叠构建过孔并导入相应的过孔。布局优化至关重要,要考虑信号完整性和电源分布。

6. **布线**:

- bondwire拉线时,需要根据基板走线情况和BALLMAP进行调整,以优化出线路径。同时,优化Bondpad pitch,使得间距尽可能大,利于生产且降低成本。线弧长度和finger的设计应满足工艺能力,关键信号线应尽量短以减少干扰。

7. **优化设计**:

- 持续调整布局布线,以提高设计效率和性能。

8. **自检发初稿**:

- 对设计进行全面检查,确保符合基板设计检查内容,无误后提交初步设计稿。

9. **导出GERBER等后续工作**:

- 根据不同供应商的要求,选择合适的设计资料用于基板生产,或进行存档。

在建立BGAPackage的过程中,需要按照客户的资料建立BGABallPad的网络连接关系,并保存为TXT格式。TXT文档应包含PinNumber、PinNetName、封装名称和焊盘坐标等信息。通过CADENCE ALLEGRO的特定功能(如ADD-Standardpackage-BGAText-inwizard)导入编辑好的封装信息,放置于BASE层,完成封装设计后,删除无用的net。

总结来说,CADENCE ALLEGRO的基于WB方式的软件操作流程是一个综合性的设计过程,涉及多步骤的协同工作,包括封装设计、电气连接、工艺规则设定、布局布线优化和设计验证,确保了半导体封装设计的高效和准确。