FPGA实现32阶FIR滤波器:硬件优化与凯泽窗设计

146 浏览量

更新于2024-09-03

收藏 960KB PDF 举报

"FPGA实现32阶FIR数字滤波器的硬件电路方案"

本文探讨了如何使用FPGA(Field-Programmable Gate Array)来实现一个32阶的FIR(Finite Impulse Response)数字滤波器。FIR滤波器在数字信号处理领域具有重要地位,因其线性相位特性、稳定性以及灵活性而被广泛采用。在设计过程中,作者并未利用线性相位滤波器的对称性来简化硬件实现,但指出结合特定算法可以减少硬件资源和提高运算速度。

FPGA的可编程性使得设计能够适应不同的滤波需求,比如调整参数来实现高通或带通滤波器。这在实际应用中具有显著的价值,因为可以根据具体场景的需求进行定制化设计。在软件无线电等技术中,高性能的数字滤波器是不可或缺的组成部分,用于信号的预处理和解析。

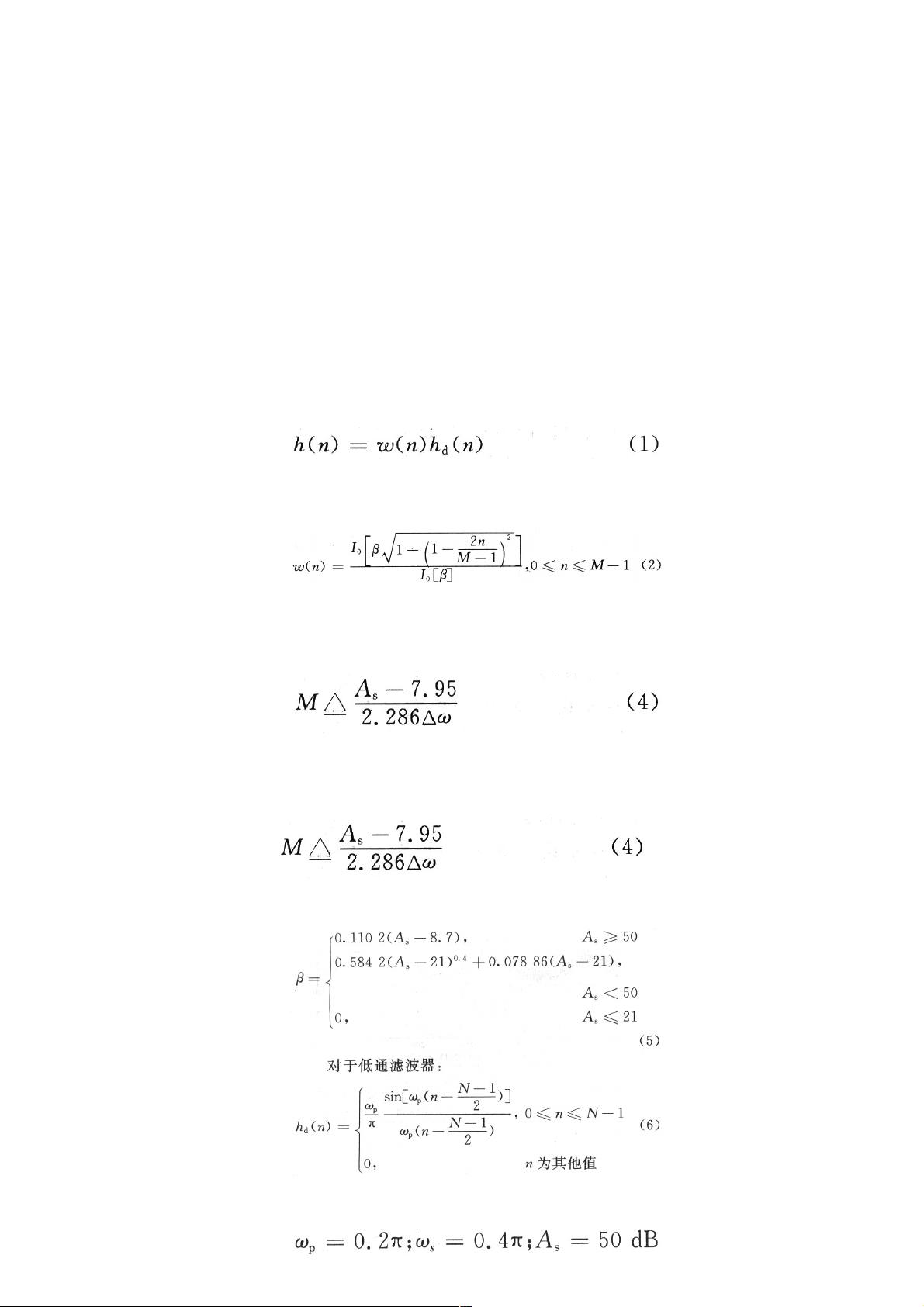

FIR滤波器的设计通常涉及窗函数的选择,本文采用的是凯泽窗(Kaiser Window)。凯泽窗提供了一种灵活的方式来调整过渡带宽和阻带衰减,通过形状参数β的调整,可以优化滤波器性能。在给定特定的通带截止频率ωp、阻带起始频率ωs和阻带衰减As后,可以计算出滤波器的阶数M和形状参数β,进而设计出满足要求的滤波器。例如,文章中提到的一个32阶FIR低通滤波器,其幅频特性可以通过Matlab进行计算和可视化。

在FPGA实现中,滤波器的系数需要从浮点型转换为定点型,以便硬件能处理。量化过程是这个转换的关键步骤,它影响滤波器的精度和所需的硬件资源。本文选择12位二进制来量化系数,这样可以平衡精度和资源消耗。

滤波器的硬件实现基于并行分布式算法,该算法将滤波器的差分方程重新组织,将加权和操作并行化。在FPGA中,乘法操作通常由查找表(Look-up Table, LUT)来代替,以提高计算效率。通过这种方法,FPGA可以实现高效的FIR滤波器,快速处理输入信号并产生相应的输出。

本文提供的方案展示了如何利用FPGA的优势来设计和实现一个高效、可配置的32阶FIR数字滤波器,同时提到了设计过程中的关键步骤,包括滤波器参数的计算、系数的量化以及并行分布式算法的硬件实现,这对于理解FPGA在数字信号处理中的应用有着重要的指导意义。

2014-06-21 上传

2021-07-13 上传

2021-07-13 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

2021-07-13 上传

weixin_38620741

- 粉丝: 1

- 资源: 909

最新资源

- Wrox.Professional.Ajax.2nd.Edition.Mar.2007

- java连接数据库驱动的代码.txt

- The C++ Standard Library

- java 如何打包成jar和exe.txt

- Arcgis Desktop 9.2 使用手册

- 互换性与测量技术基础复习与练习

- Effective STL

- 多变量时间序列异常样本的识别

- 英语学习的相关资料哦

- C语言面试题之华为篇.doc

- struts2 讲义

- PCB高级设计系列讲座

- c++编程思想(卷2)

- c++编程思想(卷1)

- AVR_单片机与GCC_编程

- 达内面试125题全,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,