Intel Agilex FPGA DDR4 DIMM设计指南

需积分: 15 122 浏览量

更新于2024-07-09

收藏 5.43MB PDF 举报

"该文档是Intel Agilex FPGA IP User Guide,专注于外部存储器接口,特别是DDR4 DIMM的布局指南,适用于那些寻求DDR4 DIMM规范参考设计的工程师。"

在Intel Agilex FPGA系列中,外部内存接口(EMIF)是连接FPGA与外部存储设备的关键部分,如DDR4 DIMM。这份用户指南详细介绍了如何有效地利用这些接口来实现高效、可靠的存储系统设计。以下是关键知识点的详细说明:

1. **Release Information**:

提供了该IP的最新版本信息,如Intel Quartus Prime Design Suite的19.4版,以及IP版本为2.0.0,确保用户了解当前使用的软件和IP的状态。

2. **Intel Agilex FPGA EMIF IP – Introduction**:

这一部分介绍了EMIF IP协议和特性支持,包括它能够处理的各种内存标准,比如DDR4。此外,还概述了设计流程,帮助用户理解从开始到完成设计的一系列步骤。

3. **Intel Agilex EMIF IP Design Checklist**:

设计检查列表是确保成功设计的关键工具,它列出了设计过程中需要考虑的重要事项,有助于防止常见错误并提高设计质量。

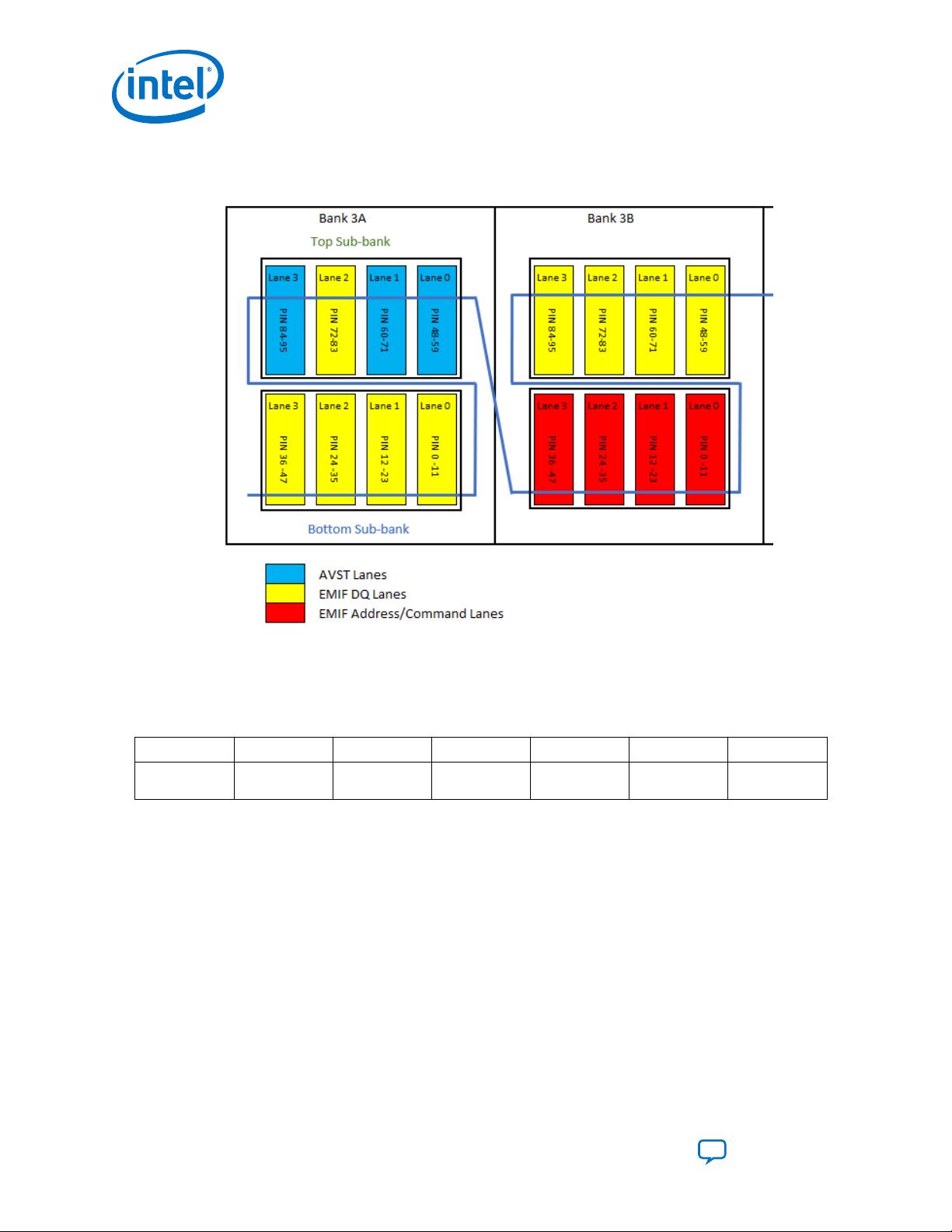

4. **Intel Agilex FPGA EMIF IP – Product Architecture**:

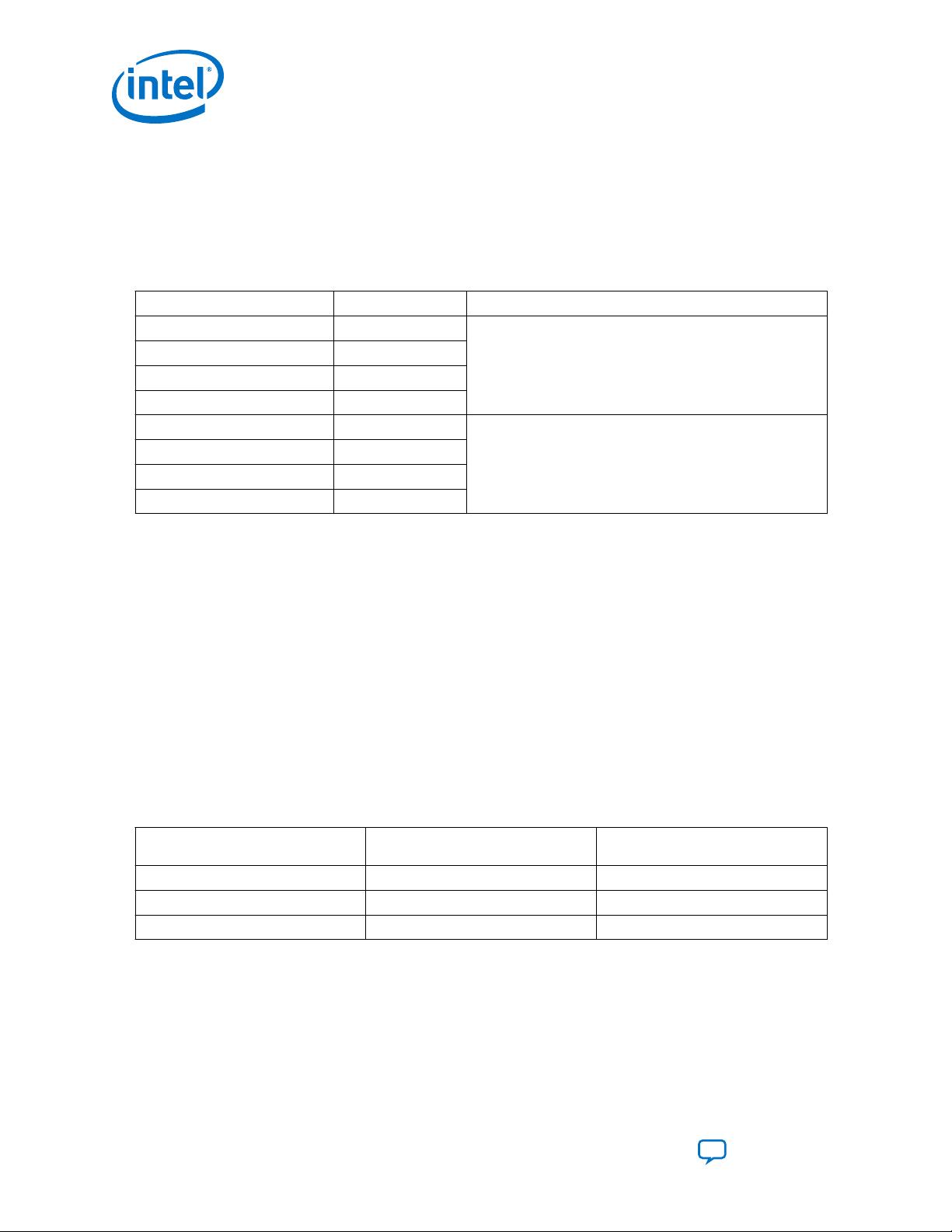

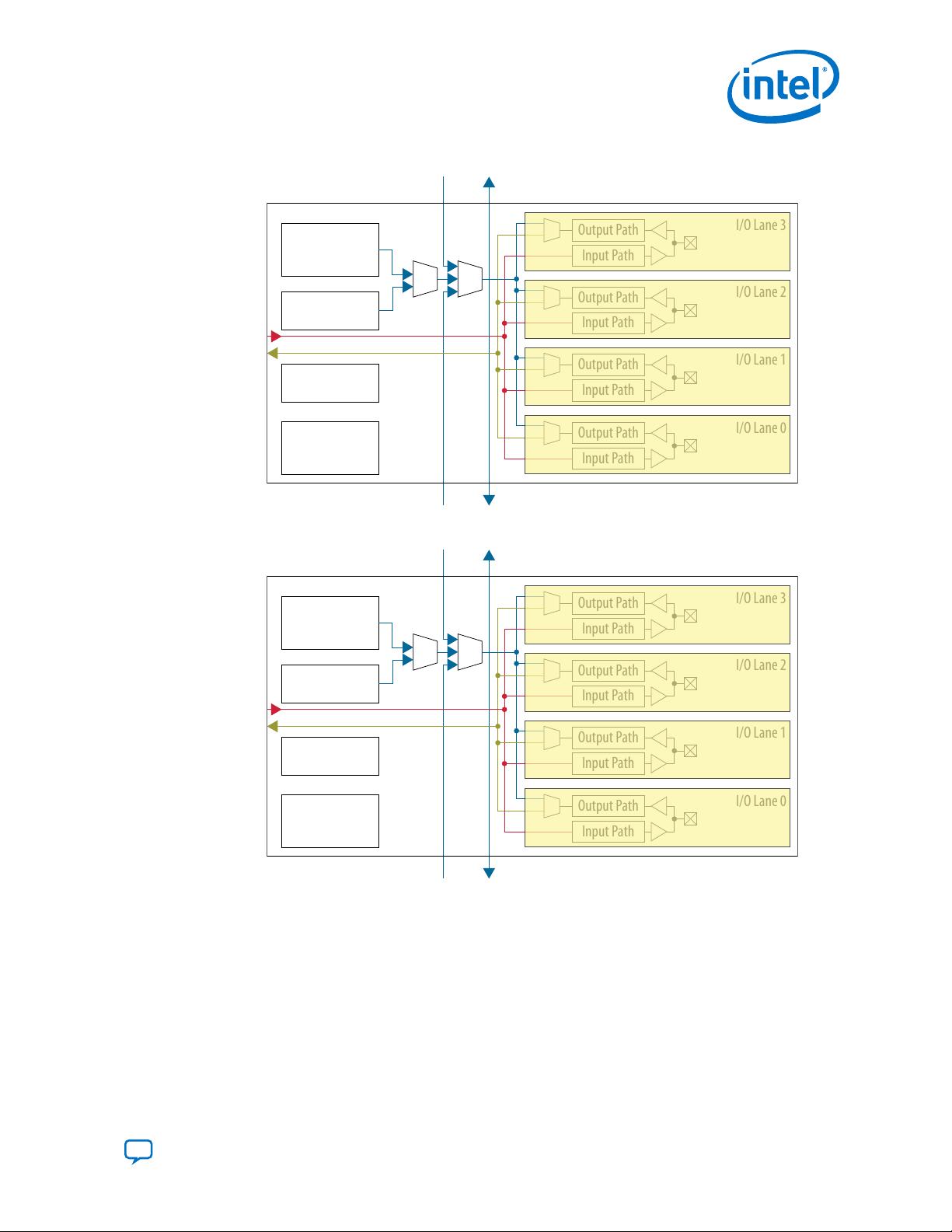

- **I/O Subsystem**: FPGA EMIF的I/O子系统是接口的基础,它处理输入/输出信号的转换。

- **I/O State Machine (I/O SS)**: I/O状态机管理I/O操作的时序,确保数据传输的正确性。

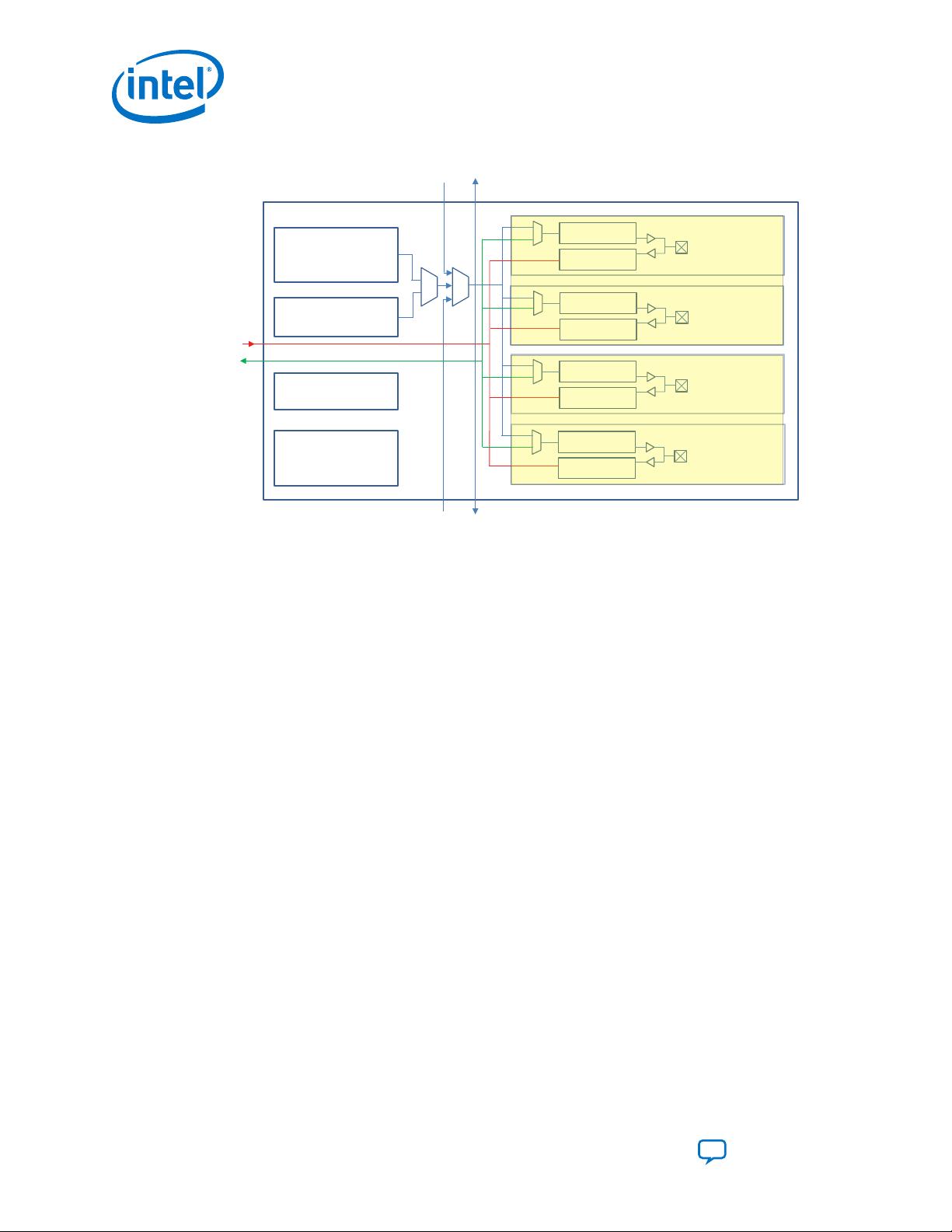

- **I/O Bank and Lane**: I/O银行和 lane 分配决定了物理连接的组织方式,优化信号路由和性能。

- **Input DQS Clock Tree**: 输入DQS时钟树用于同步从内存设备接收的数据,确保数据的正确捕获。

- **PHY Clock Tree**: PHY时钟树是物理接口的时钟基础设施,为接口操作提供时钟信号。

- **PLL Reference Clock Networks**: PLL参考时钟网络生成所需的高速时钟,以驱动整个EMIF系统。

- **Clock Phase Alignment**: 时钟相位对齐确保数据传输的精确时序,减少抖动和提高系统稳定性。

5. **Intel Agilex EMIF Sequencer**:

EMIF sequencer是一个重要的组件,它控制内存访问序列,包括初始化、读写操作等,确保内存操作的正确执行。

6. **Intel Agilex EMIF Calibration**:

自动校准功能允许IP自动调整参数以适应不同的内存设备,优化性能并保证兼容性。

7. **DDR4 DIMM Layout Guide**:

文档特别提到了DDR4 DIMM的布局指南,这是针对DDR4内存模块的详细设计规范,对于构建符合行业标准的内存接口至关重要。

这份Intel Agilex FPGA IP User Guide提供了全面的指导,涵盖了从基本概念到高级特性的所有方面,是设计基于Intel Agilex FPGA的DDR4 DIMM存储系统的宝贵资源。它不仅解释了硬件层面的接口设计,还强调了设计流程和注意事项,确保用户能够成功地集成和优化DDR4内存系统。

195 浏览量

点击了解资源详情

点击了解资源详情

149 浏览量

463 浏览量

123 浏览量

207 浏览量

138 浏览量

2019-06-27 上传

tutaipo

- 粉丝: 3

- 资源: 13

最新资源

- 带日历的VB圆形的模拟时钟代码

- apache-maven-3.6.0-bin.rar

- delphi人才信息管理系统.zip

- 涂料、裱煳、刷浆木材表面施涂溶剂型混色涂料施工工艺标准

- react-advance

- personal-rank-implemented-by-CPP

- Onliner.by конвертер цен-crx插件

- 新疆某钢厂钢结构厂房工程施工组织设计

- 粤语报时示例.rar

- linux-sk:-基于ZEN的内核,具有其他功能

- Определение CMS - iTrack-crx插件

- 密码学:国王密码学课程的python游乐场

- github-slideshow:机器人提供动力的培训资料库

- 价格区间滑块

- fsm

- 51单片机驱动12864液晶显示(有字库)程序(汇编)keil工程文件C源文件