DDR3布线实战:FPGA_ARM与DDR3的等长与电源管理

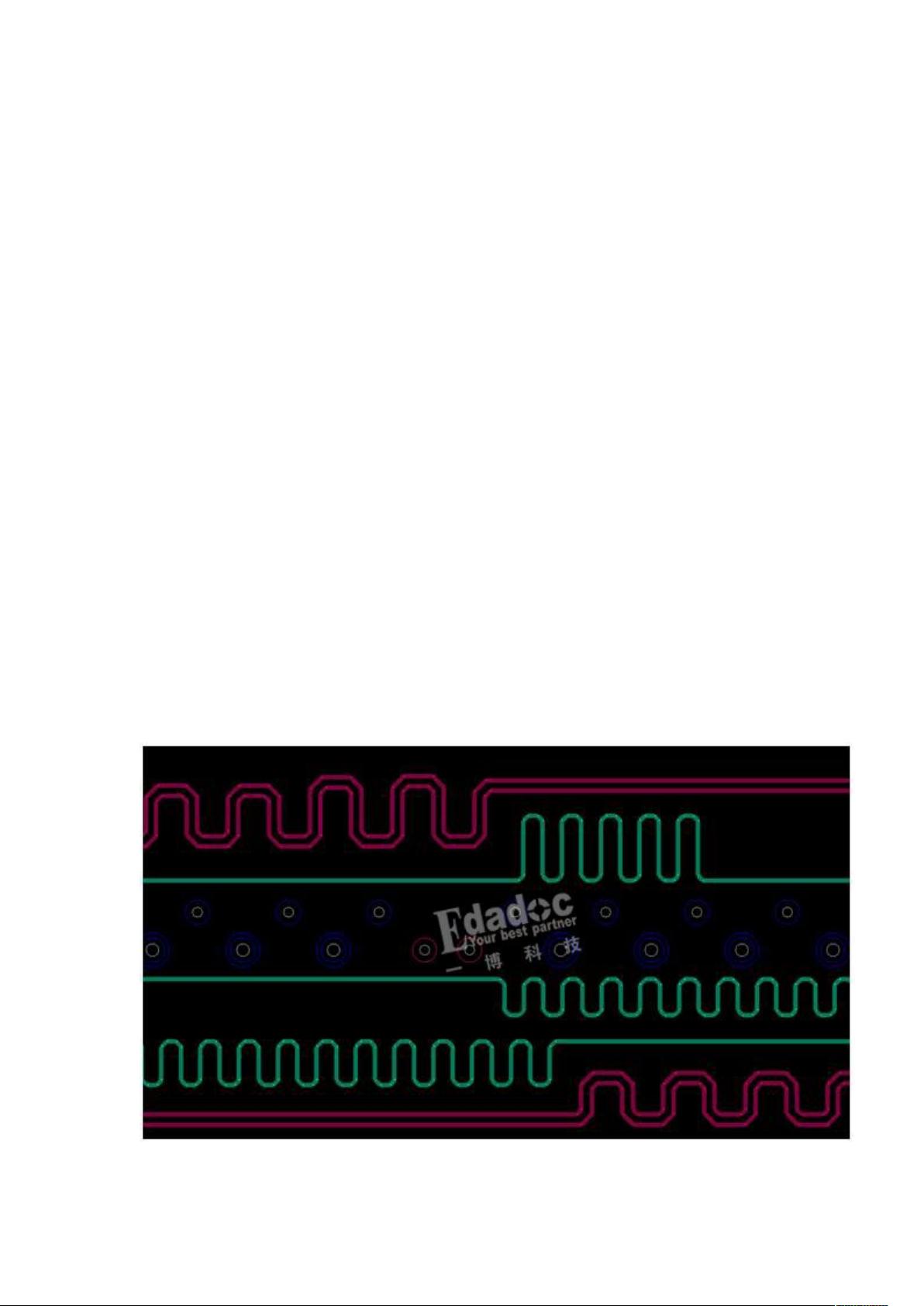

"FPGA与ARM系统中,DDR3内存的布线是关键设计环节,涉及到严格的数据等长和时序匹配。对于DDR3,数据线(DQ, DQS, DQM)需要组内等长,误差小于20MIL,而地址、控制和时钟信号需以时钟为基准,误差控制在100MIL以内。布线时应注意芯片的Pin-delay,保持同组信号在同一层,并考虑不同层的传播延迟。此外,还需要注意Z轴延时和蛇形绕线规则,以保持等时性。电源管理同样重要,包括VDD(1.5V)、VTT(0.75V)和VREF(0.75V)的电源平面设计和去耦电容的使用,以确保电源完整性和满足DDR3的电压容差要求。" DDR3内存的布线设计是FPGA和ARM系统中的核心技术,主要目的是保证数据传输的准确性和系统的稳定性。DDR3内存的严格等长要求确保了数据在传输过程中的同步性,对于64位的DDR3,数据线、时钟线以及控制线都有特定的等长要求。数据线(DQ, DQS, DQM)要求组内等长,以减少数据传输的时序误差,而地址、命令和控制信号则需要与时钟信号保持精确的时间关系,通常地址和控制线会与时钟线归为一组进行布线。 布线过程中有几点需要注意:首先,要确认芯片的Pin-delay特性,确保在布线时开启该功能,以避免因延迟不一致导致的问题。其次,同组信号应尽量在同一层布线,以减少因层间切换产生的延迟差异,同时,层间的等长也要保持一致。此外,还要考虑不同层的传播速度差异,表层走线通常较短,以减少这种差异的影响。Z轴延时也需要考虑,特别是在采用多层PCB设计时,需要正确设置层叠以确保Z轴延时的准确性。 蛇形绕线是常见的等长手段,单线按照3倍线宽(W)进行弯曲,差分对则按照5倍线宽进行,同时保持信号组内的间距和不同组间的最小间距,以减少干扰。DQS和CLK信号与其他信号的距离应大于5倍到主参考平面的间距(H),以增强信号的隔离。 电源管理方面,DDR3有三个关键电源:VDD(1.5V)是核心电源,负责为DDR3提供工作电压,需要在整个电源平面上均匀分布并配合去耦电容保证电源完整性;VTT(0.75V)用于终端电阻,确保信号质量;VREF(0.75V)是参考电压,对于VREFCA和VREFDQ,它们分别服务于地址和数据线。每个电源都有相应的容差要求,需要通过合理的电源平面设计和去耦电容布局来满足这些要求。 DDR3的布线设计是一门精细的艺术,需要综合考虑等时性、信号完整性和电源完整性,确保系统运行的高效和可靠。

下载后可阅读完整内容,剩余4页未读,立即下载

- 粉丝: 0

- 资源: 3

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

最新资源

- 李兴华Java基础教程:从入门到精通

- U盘与硬盘启动安装教程:从菜鸟到专家

- C++面试宝典:动态内存管理与继承解析

- C++ STL源码深度解析:专家级剖析与关键技术

- C/C++调用DOS命令实战指南

- 神经网络补偿的多传感器航迹融合技术

- GIS中的大地坐标系与椭球体解析

- 海思Hi3515 H.264编解码处理器用户手册

- Oracle基础练习题与解答

- 谷歌地球3D建筑筛选新流程详解

- CFO与CIO携手:数据管理与企业增值的战略

- Eclipse IDE基础教程:从入门到精通

- Shell脚本专家宝典:全面学习与资源指南

- Tomcat安装指南:附带JDK配置步骤

- NA3003A电子水准仪数据格式解析与转换研究

- 自动化专业英语词汇精华:必备术语集锦

信息提交成功

信息提交成功