同步与异步复位:亚稳态解析与设计考量

需积分: 50 180 浏览量

更新于2024-09-16

1

收藏 196KB PDF 举报

"本文主要探讨同步复位、异步复位以及它们引发的亚稳态问题,关注如何提升数字设计的可靠性。"

在数字电路设计中,复位机制是确保系统正确初始状态的关键部分。同步复位和异步复位是两种常见的复位方式,它们各有优缺点。

同步复位是指复位信号与系统时钟同步,通常在时钟的上升沿或下降沿生效。这种方式的优点在于它能确保系统在时钟周期的特定时刻进行复位,降低了设计的复杂性和不确定性。然而,同步复位也存在局限性,例如,如果复位信号不在预定义的时钟边沿到来,可能会导致数据竞争,影响系统的稳定性。

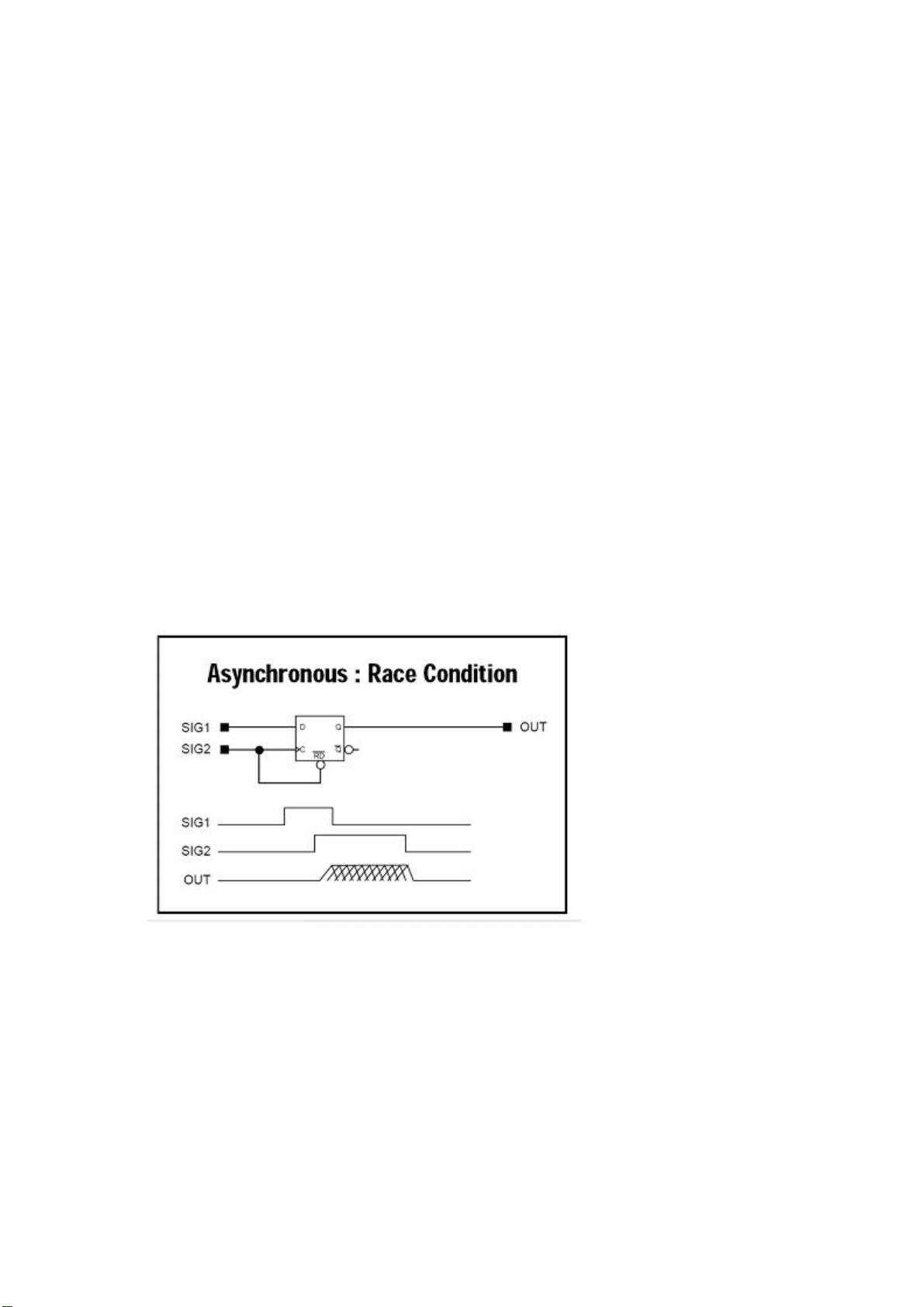

相比之下,异步复位不依赖于时钟,可以随时对系统进行复位。这提供了更大的灵活性,但也引入了潜在的问题。由于异步复位信号可能在任何时间到达,如果信号中存在毛刺或者延迟不确定性,可能导致触发器的非预期翻转,进一步引发时序问题。如图1所示的例子,当复位信号SIG2在时钟信号的上升沿前后到达,可能会产生竞争条件,即亚稳态。

亚稳态是数字电路中的一种临时不稳定状态,发生在时序路径上信号的传递速度不能满足电路的定时要求时。当输入信号未能在足够短的时间内达到其应有的逻辑电平,电路内部的触发器可能无法及时响应,从而需要额外的时间来稳定输出。这种情况可能导致输出状态在一段时间内处于不确定,增加了设计的不可预测性和潜在错误。

为了应对亚稳态,设计师需要考虑以下几个策略:

1. 增加定时裕量:确保所有信号传输都有足够的提前量,以避免接近时序边界。

2. 使用同步复位:尽管它不能完全消除亚稳态,但可以降低其出现的概率。

3. 异步复位信号的去抖动:通过添加简单的去抖电路,可以滤除复位信号中的毛刺,减少亚稳态的可能性。

4. 采用自同步复位:将异步复位信号通过同步器(通常是一个或多个触发器)转换为与系统时钟同步的信号,从而减少不确定性。

亚稳态对集成电路(ASIC)的可靠性至关重要,因为微小的环境变化(如温度、电压或制造工艺差异)都可能使原本正常工作的设计突然出现错误。因此,理解和管理亚稳态是高速数字设计中不可或缺的一部分,它涉及到系统级的性能优化和故障预防。

理解同步复位和异步复位的工作原理以及如何处理亚稳态是提高数字系统可靠性的关键。设计师必须仔细考虑这些因素,并在设计早期阶段就采取适当的措施来防止潜在的问题。通过深入研究和应用上述策略,可以大大增强系统在各种条件下的稳定性。

2010-11-09 上传

2012-12-09 上传

点击了解资源详情

2022-02-11 上传

2007-11-16 上传

2013-05-15 上传

2020-08-18 上传

2020-08-20 上传

点击了解资源详情

apex_ch

- 粉丝: 6

- 资源: 5

最新资源

- Fisher Iris Setosa数据的主成分分析及可视化- Matlab实现

- 深入理解JavaScript类与面向对象编程

- Argspect-0.0.1版本Python包发布与使用说明

- OpenNetAdmin v09.07.15 PHP项目源码下载

- 掌握Node.js: 构建高性能Web服务器与应用程序

- Matlab矢量绘图工具:polarG函数使用详解

- 实现Vue.js中PDF文件的签名显示功能

- 开源项目PSPSolver:资源约束调度问题求解器库

- 探索vwru系统:大众的虚拟现实招聘平台

- 深入理解cJSON:案例与源文件解析

- 多边形扩展算法在MATLAB中的应用与实现

- 用React类组件创建迷你待办事项列表指南

- Python库setuptools-58.5.3助力高效开发

- fmfiles工具:在MATLAB中查找丢失文件并列出错误

- 老枪二级域名系统PHP源码简易版发布

- 探索DOSGUI开源库:C/C++图形界面开发新篇章