ModelsimSE10.0c入门教程:Quartus11.0仿真指南

需积分: 8 187 浏览量

更新于2024-09-10

1

收藏 460KB PDF 举报

"这篇教程是针对初学者的ModelsimSE10.0.c使用指南,主要讲解如何在Quartus 11.0环境下结合Modelsim进行HDL语言的仿真,特别是Verilog HDL的仿真操作。教程还涉及到Testbench的编写,并通过一个计数器程序作为实例进行演示。"

在数字电路设计中,Modelsim是一款广泛使用的仿真工具,它允许开发者在硬件描述语言(HDL)如Verilog或VHDL中进行设计验证。对于初学者来说,了解如何设置和使用Modelsim是进入 FPGA 和 ASIC 设计的重要步骤。Quartus 10 版本之后,不再内置波形仿真软件,因此需要像Modelsim这样的第三方软件来完成仿真任务。

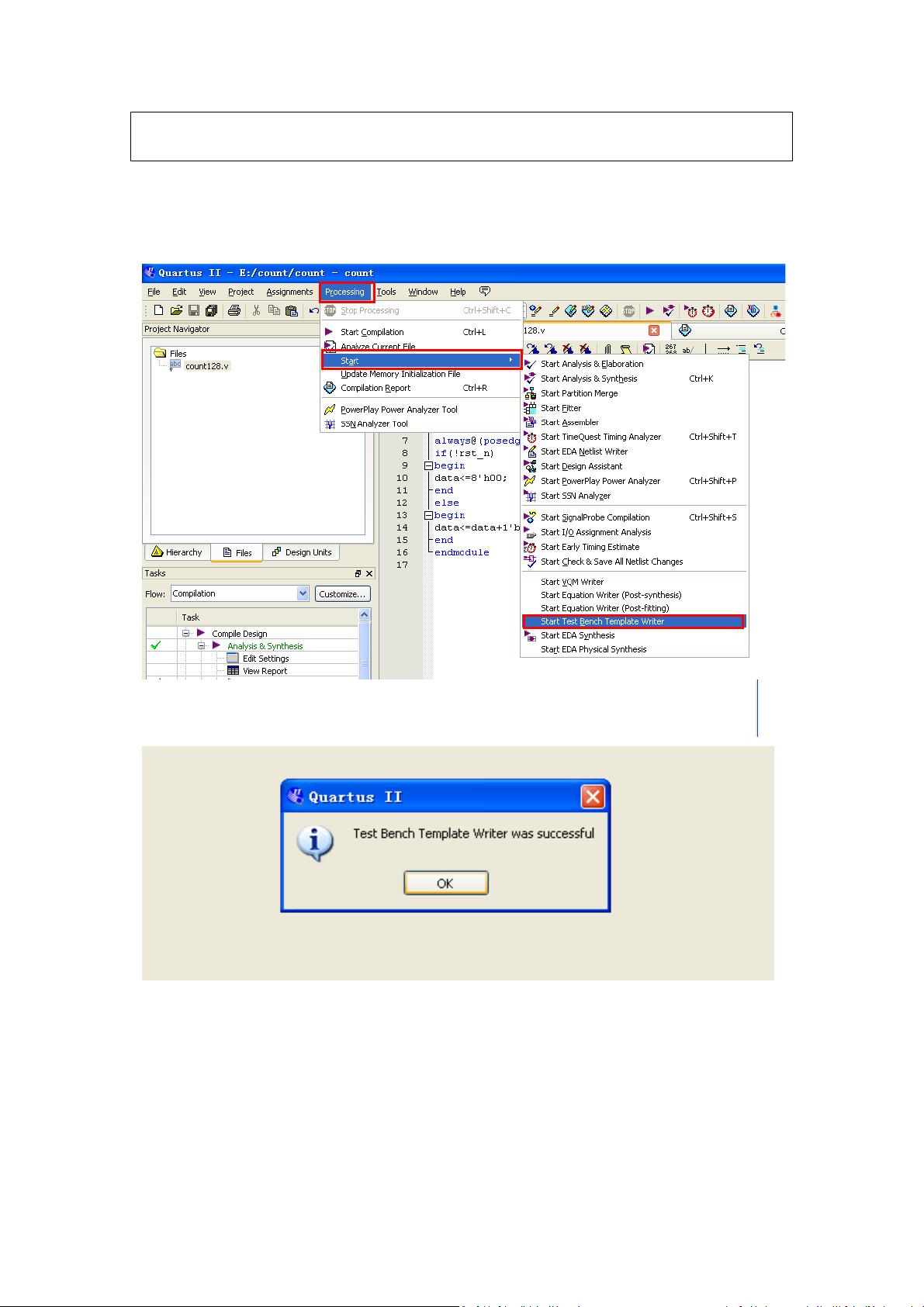

首先,我们需要安装Quartus 11.0和Modelsim 10.0c。在新建工程时,要选择相应的仿真软件和语言,这里选择了Modelsim和Verilog HDL。接下来,我们需要编写设计模块,例如这里的计数器模块`count128.v`:

```verilog

module count128 (

input clk,

input rst_n,

output divclk,

output [7:0] data

);

reg [7:0] data;

assign divclk = data[7];

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin

data <= 8'h00;

end else begin

data <= data + 1'b1;

end

end

endmodule

```

这个计数器模块实现了对输入时钟`clk`的128分频,输出`divclk`表示每128个时钟周期翻转一次,同时输出8位的计数值`data`。

然后,我们需要创建Testbench文件,这是验证设计功能的关键部分。Testbench通常会模拟真实环境中的输入信号,以及观察和分析设计的输出。对于`count128`,Testbench可能如下所示:

```verilog

`timescale 1ps/1ps

module count128_vlg_tst(); // 顶层模块名

// constants

// general purpose registers

reg eachvec;

// test vector input registers

reg clk;

reg rst_n;

// wires

wire [7:0] data;

// Instantiate the design under test

count128 dut (

.clk(clk),

.rst_n(rst_n),

.divclk(divclk),

.data(data)

);

initial begin

clk = 0;

rst_n = 1; // 仿真开始时,复位信号为高

#100 rst_n = 0; // 在100ps后拉低复位

#100 rst_n = 1; // 释放复位

forever begin

clk = ~clk;

#50; // 每隔50ps切换时钟

end

end

endmodule

```

Testbench中,我们实例化了设计模块`count128`,并给其输入信号提供合适的激励。`initial`块用于设置初始条件和时序控制,比如复位和时钟信号的生成。通过观察和分析Testbench运行的结果,可以验证设计是否按照预期工作。

这篇教程通过实例介绍了Modelsim的基本使用方法,包括如何在Quartus环境中调用Modelsim进行仿真,以及如何编写和使用Testbench。对于想要学习HDL仿真的初学者来说,这是一个很好的起点,能够帮助他们快速掌握基本的仿真流程和技巧。

181 浏览量

2015-07-05 上传

116 浏览量

125 浏览量

181 浏览量

322 浏览量

点击了解资源详情

点击了解资源详情

2010-08-28 上传

ghk12397

- 粉丝: 0

最新资源

- 实际操作:从用户接触至需求分析的完整流程

- BEA Java虚拟化技术:提升效率与灵活性

- LDAP入门:原理、应用与故障诊断

- C++标准模板库STL详解:从入门到精通

- 2008年Intel白皮书:CPU升级优于GPU的选择

- ASP.NET中Frameset使用详解

- Hibernate入门教程:Java习惯下的关系数据库持久化

- 跟随陈皓探索Makefile:从基础到高级技巧

- Oracle架构解析:数据库与集群详细图

- 使用Eclipse进行ARM跨平台开发指南

- 柯尓顿信息咨询技术公司创业蓝图:引领信息咨询业

- 单片机原理与应用详解:从基础知识到主流产品

- 探索ASP.NET Web应用开发:深入浅出(英文版)

- C++笔试:结构体与类的区别及代码解析

- C++编程题目解析:引用与函数参数

- C++构造函数中的成员初始化列表详解