"Modelsim初级教程:Verilog和VHDL混合仿真指南"

需积分: 10 73 浏览量

更新于2024-01-04

收藏 2.35MB DOCX 举报

Modelsim是Model公司开发的一款仿真工具,支持Verilog、VHDL以及它们的混合仿真。通过分步执行程序,设计者可以直接查看程序下一步要执行的语句,同时还可以在任何步骤任何时刻查看任意变量的当前值,并在Dataflow窗口查看输入输出的连续变化。相比于Quartus自带的仿真器,Modelsim功能更为强大,是目前业界最通用的仿真器之一。

针对初学者,Modelsim自带的教程是一个很好的选择,在Help->SE PDFDocumentation->Tutorial中可以找到。该教程从简单到复杂、从低级到高级地讲述了Modelsim的各项功能的使用,简单易懂。但是需要注意的是教程里所有事例的初期准备工作都已经放在example文件夹里,直接将它们添加到Modelsim就可以使用。因此,初学者可能不知道如何进行当前操作的前期准备。

以下是Modelsim初级使用的教程:

1. 安装Modelsim

首先需要进行Modelsim的安装。安装完成后,打开软件并进行初步的设置及必要的配置。

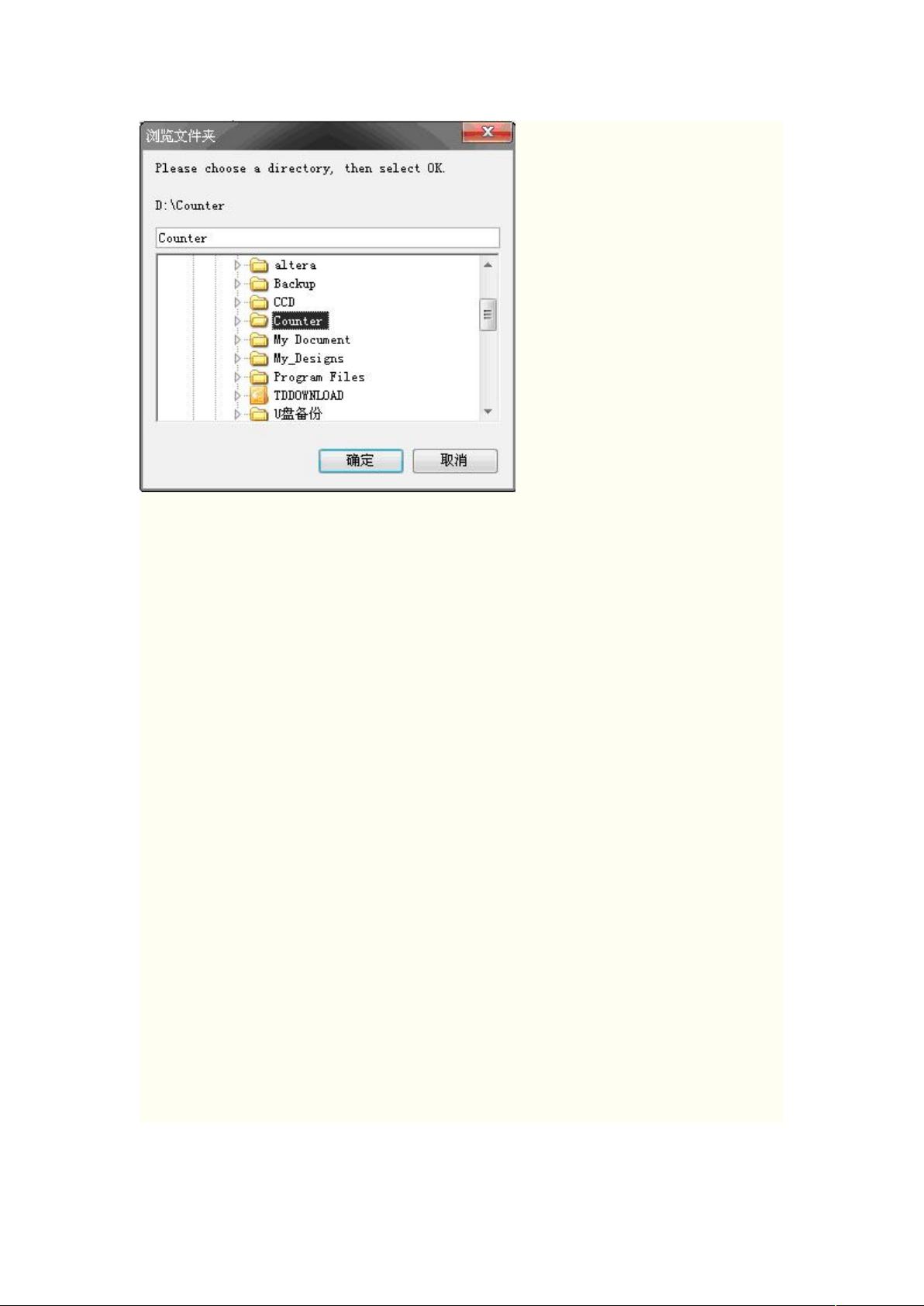

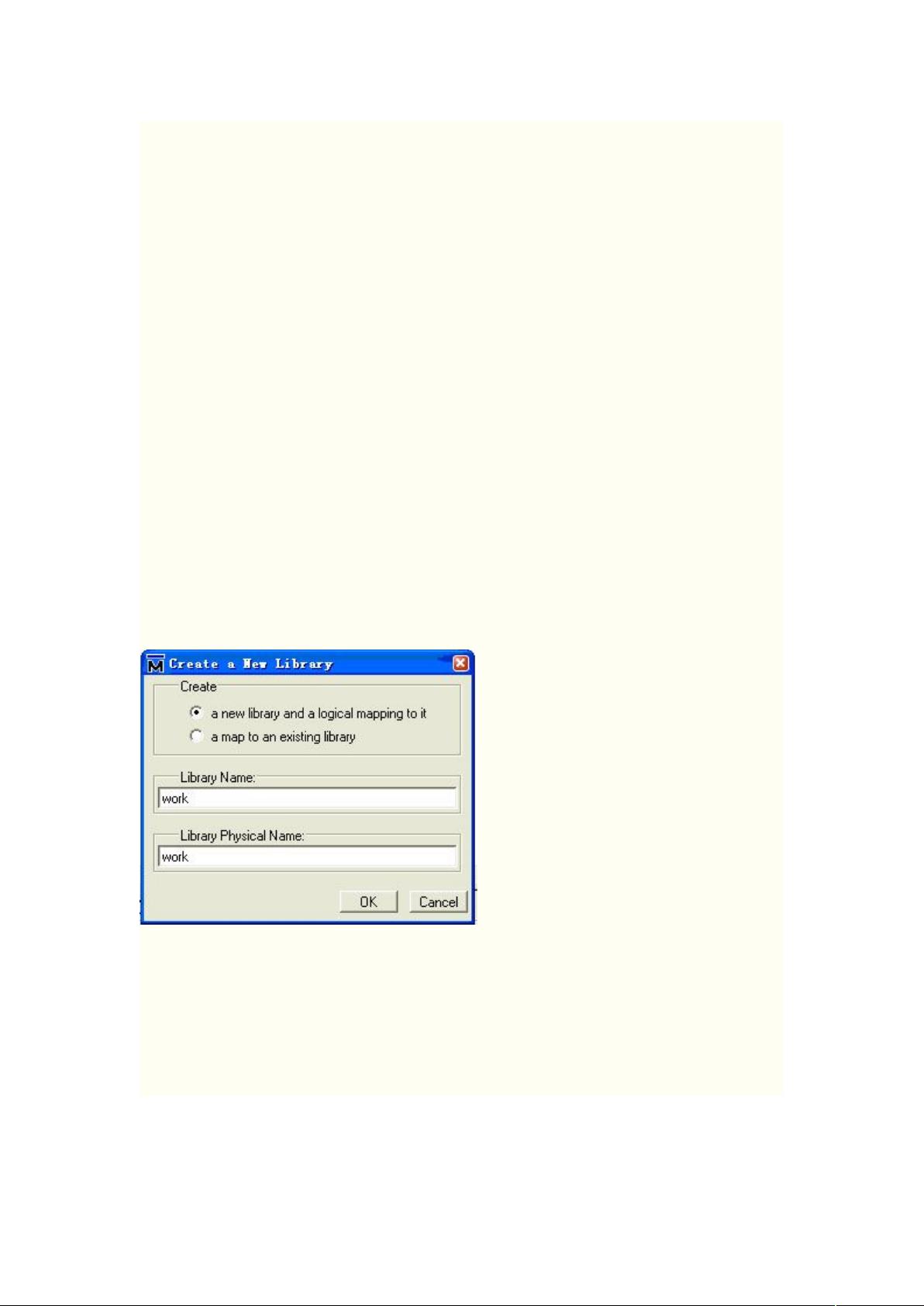

2. 创建工程

在Modelsim中,需要创建一个工程来进行仿真。在创建工程时,需要指定所用的设计文件,例如Verilog或VHDL文件。

3. 创建测试文件

在创建工程后,需要创建测试文件。测试文件可以包括测试向量或者对设计文件的输入信号进行刺激的信息。

4. 编译

进行完前期准备工作后,需要对设计文件和测试文件进行编译。编译是为了将Verilog或VHDL代码编译成仿真可执行的形式,以便进行仿真分析。

5. 运行仿真

编译完成后,可以进行仿真分析。在仿真分析中可以查看信号的变化、寄存器的值以及模块与顶层实体的交互情况。

6. 查看波形

Modelsim可以通过波形查看器来观察仿真过程中信号的变化情况。通过观察波形,可以发现设计中的问题,进行调试和优化。

7. 仿真选项

Modelsim提供了多种仿真选项,例如单步执行和断点设置等,可以更方便地进行调试和验证设计。

8. 结束仿真

仿真完成后,需要进行一系列的收尾工作,例如清理仿真数据和结果。

总结:

Modelsim是一款功能强大的仿真工具,能够支持Verilog、VHDL等设计语言的仿真,提供了丰富的仿真功能以及直观的界面,对于初学者来说,可以通过Modelsim自带的教程进行学习,并且需要注意对于前期准备工作的理解和掌握。通过学习并实践,可以熟练地使用Modelsim进行设计验证和调试工作。同时,建议初学者多参考相关的教程和资料,不断提升自己的仿真技能,更好地应用Modelsim进行设计开发。

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

lalalamiao

- 粉丝: 0

最新资源

- Access查询分析器工具包下载与使用

- 最新Spring IDE 3.1下载安装包发布

- 如何使用Java代码抓取天猫评论数据

- 嵌入式Linux源码教程与核心驱动开发分析

- HTML和CSS实现Netflix克隆项目教程

- 贝壳鼠标连点器2.0.2.6:极致点击体验

- Linux系统snmp库安装包net-snmp-libs 5.3.2.2下载

- 构建火星漫游者图像API:C#实践项目详解

- 掌握现代Web开发:ReactJS与Node.js实践指南

- 电赛FDC2214程序开发与调试指南

- SpringBoot框架下使用StS开发mybatis持久层用户逻辑

- 华华鼠标自动点击器V6.0:提高工作效率的免费神器

- CH341SER USB转串口驱动的介绍与应用

- SSD5课程附加练习3详细解析

- go-mod-graph-chart:使用GO MOD GRAPH绘制模块依赖图

- 一键清除软件残留,WiseRegistryCleanerPortable使用体验