FPGA实现子带分解自适应滤波:EDA/PLD中的优化技术

"EDA/PLD中的子带分解的自适应滤波器的FPGA实现"

自适应滤波器是一种动态调整其参数以适应输入信号变化的滤波技术,广泛应用于通信、音频处理、图像处理等多个领域。在EDP(电子设计自动化)/PLD(可编程逻辑器件)中,这种技术可以通过FPGA(现场可编程门阵列)实现,以高效地处理实时数据流。FPGA的优势在于其灵活性和并行处理能力,适合实现复杂算法,如自适应滤波。

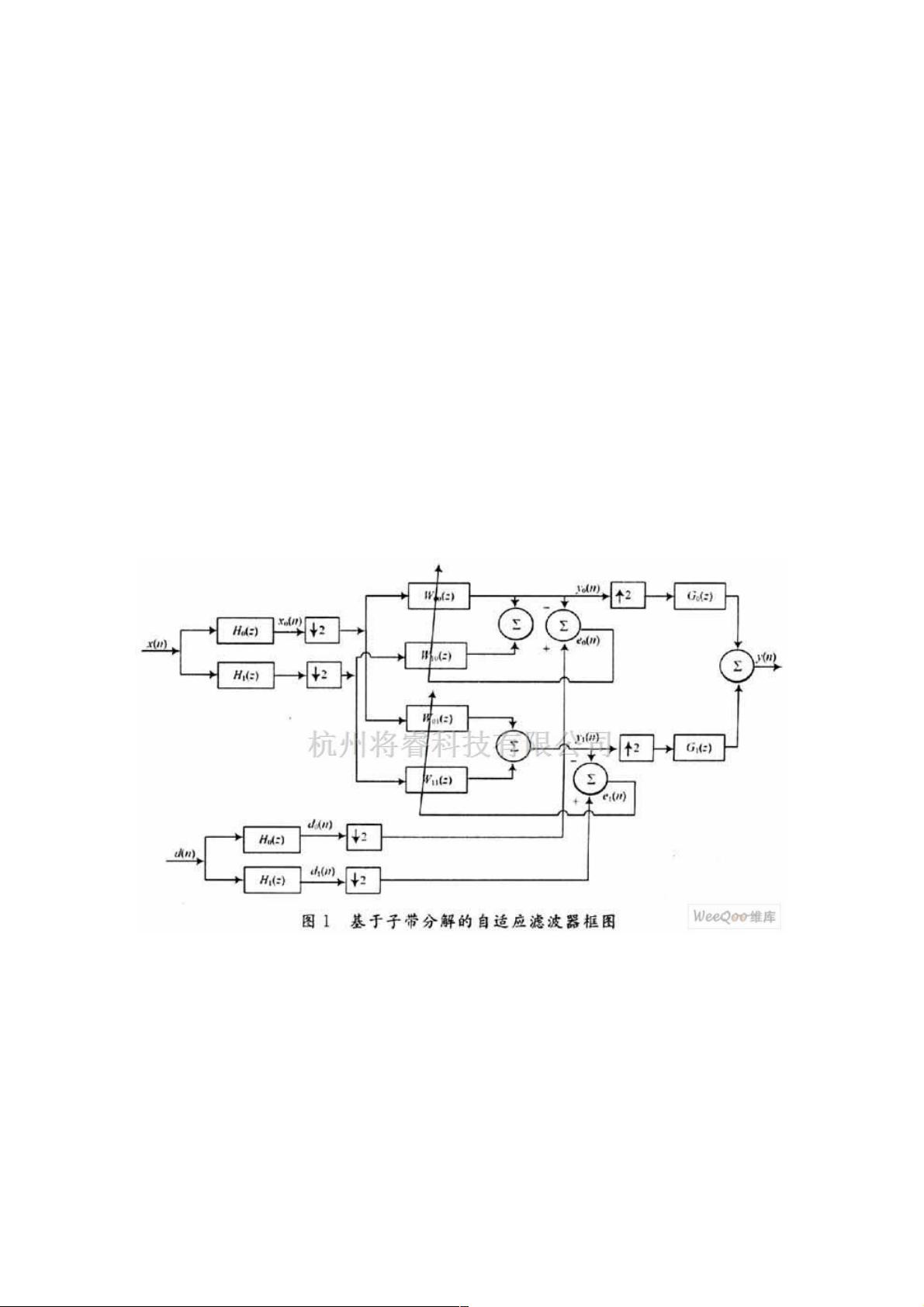

子带分解的自适应滤波策略是将输入信号和参考信号通过分解滤波器组分解成多个子带,然后在每个子带上进行自适应滤波,这有助于减少计算量,同时提升系统的收敛性能。具体流程包括以下几个步骤:

1. 子带分解:输入信号x(n)和参考信号d(n)分别通过滤波器组进行分解,形成多个频率分辨率不同的子带信号。

2. 抽取:降低子带信号的采样率,进一步减少计算需求。

3. 子带自适应滤波:在每个子带上应用自适应滤波算法,如NLMS(正常化最小均方误差)算法,以调整滤波器权重,适应输入信号的变化。

4. 内插:将子带处理后的信号恢复到原始采样率。

5. 合成滤波:通过合成滤波器组将各子带信号组合成最终的输出信号,消除子带处理引入的失真。

NLMS算法相对于传统的LMS(最小均方误差)算法,虽然计算复杂度略有增加,但由于其自适应速度更快,更适合实时处理环境。子带间的滤波器W01(n)和W10(n)用于消除由于滤波器组的非理想特性导致的混叠效应,确保信号的准确恢复。

双通道滤波器组的设计是子带分解自适应滤波的关键。分析滤波器H0(z)和综合滤波器H1(z)、G0(z)、G1(z)之间存在特定的关系,如H1(z)=H0(-z),G1(z)=-2H0(-z),G0(z)=2H1(-z)。设计时主要集中在确定H0(z),因为它决定了其他滤波器的特性。滤波器通常是FIR(有限 impulse response)类型,需要较长的滤波器长度来接近理想的频率响应特性。

在FPGA实现过程中,滤波器的系数更新、子带抽取和内插操作都需要硬件电路来完成。通过精心设计和优化,可以实现高效能和低功耗的自适应滤波器系统。FPGA的可编程性允许快速迭代设计,以适应不同应用场景的需求。

EDA/PLD中的子带分解自适应滤波器FPGA实现结合了子带处理的优势和FPGA的并行处理能力,为解决各种信号处理问题提供了高效的解决方案。这种技术在现代通信、信号处理和噪声抑制等领域的应用中具有重要价值。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2020-12-10 上传

2020-11-04 上传

2020-11-05 上传

2020-12-04 上传

2020-11-09 上传

2020-11-17 上传

weixin_38626473

- 粉丝: 3

- 资源: 927

最新资源

- JavaScript实现的高效pomodoro时钟教程

- CMake 3.25.3版本发布:程序员必备构建工具

- 直流无刷电机控制技术项目源码集合

- Ak Kamal电子安全客户端加载器-CRX插件介绍

- 揭露流氓软件:月息背后的秘密

- 京东自动抢购茅台脚本指南:如何设置eid与fp参数

- 动态格式化Matlab轴刻度标签 - ticklabelformat实用教程

- DSTUHack2021后端接口与Go语言实现解析

- CMake 3.25.2版本Linux软件包发布

- Node.js网络数据抓取技术深入解析

- QRSorteios-crx扩展:优化税务文件扫描流程

- 掌握JavaScript中的算法技巧

- Rails+React打造MF员工租房解决方案

- Utsanjan:自学成才的UI/UX设计师与技术博客作者

- CMake 3.25.2版本发布,支持Windows x86_64架构

- AR_RENTAL平台:HTML技术在增强现实领域的应用