FPGA实现的160阶FIR低通滤波器设计与仿真

需积分: 31 89 浏览量

更新于2024-09-19

收藏 349KB DOC 举报

"本文档详述了一种基于FPGA的FIR低通滤波器设计与实现过程。设计包括在MATLAB的FDATool中设定滤波器参数,然后进行硬件仿真,最终选择FPGA作为滤波器实现平台。滤波器阶数为160阶,需要160个加法器,161个乘法器。FPGA的选择基于其灵活的可编程性和适合并行处理的特点。"

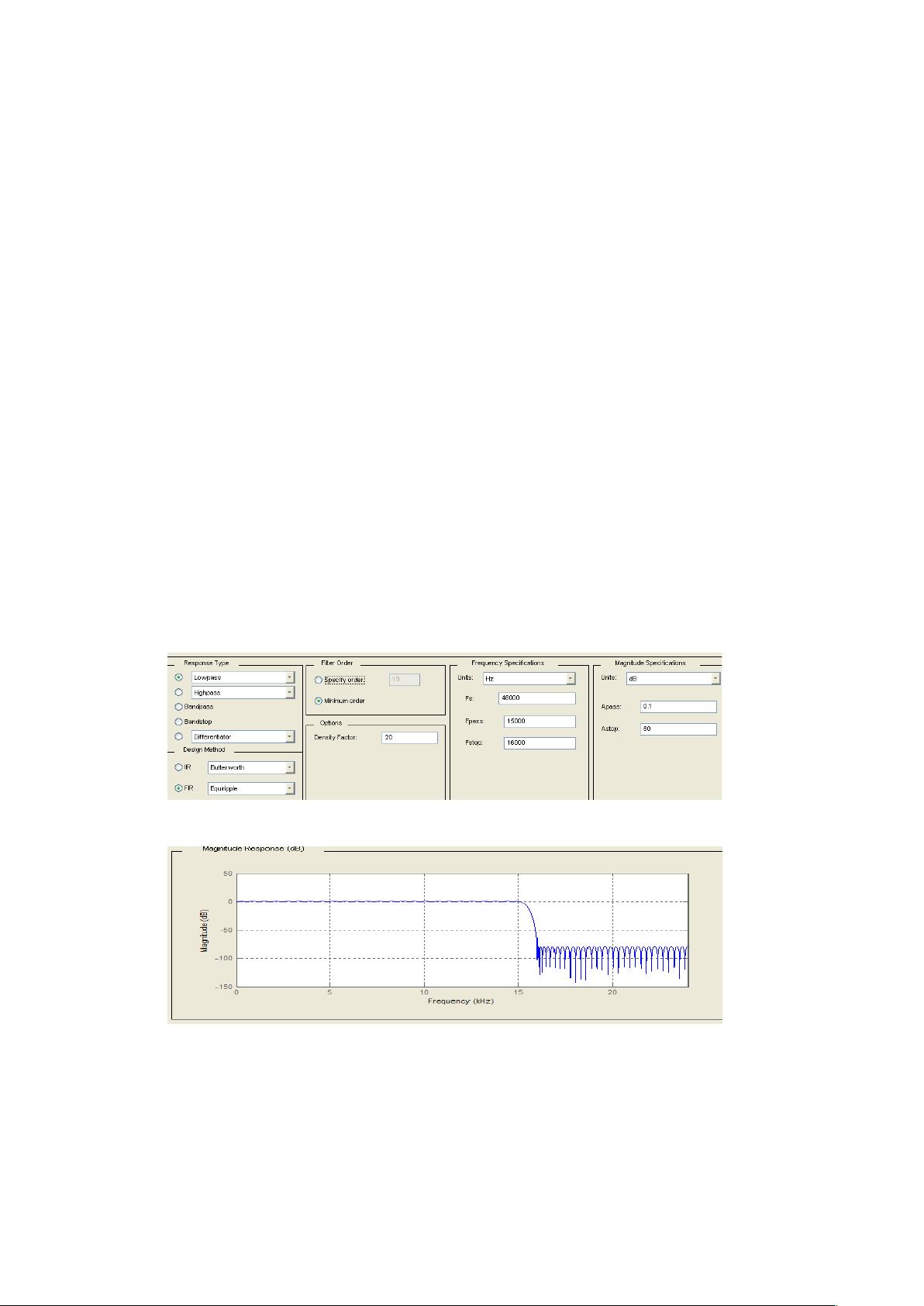

在硬件设计仿真领域,FPGA(现场可编程门阵列)常被用于实现复杂数字信号处理任务,如滤波器设计。本设计任务聚焦于创建一个FIR(有限 impulse response)低通滤波器,其技术指标包括输入信号采样率48kHz、通带频率15kHz、阻带频率16kHz、通带平坦度0.1dB、阻带衰减80dB,以及处理器字长16bits。

滤波器设计首先在MATLAB的FDATool中进行,依据技术指标定制滤波器。通过设置滤波器指标,可以得到理想的幅频响应和相频响应曲线。在设计完成后,会生成归一化的滤波器系数文件供后续硬件实现使用。

为了验证滤波器性能,使用了一个48kHz采样率的单声道音频信号作为输入源。通过对原始音频信号进行频谱分析,然后应用设计好的滤波器,观察滤波后的信号频谱变化,确认滤波效果是否满足预期。

在滤波器实现平台的选择上,考虑到FPGA的特性,如内置的触发器资源、分布式模块互联和现场可编程性,使得FPGA更适合实现并行处理的时序功能。相比于CPLD(复杂可编程逻辑器件),FPGA在处理并行处理任务时更为高效,且能适应设计需求的变化,减少了开发风险。

FPGA的基本构造由查找表、触发器和多路复用器等组成,这些模块通过适当的配置可以实现复杂的逻辑功能。在本设计中,由于滤波器阶数为160阶,所以需要160个加法器来进行信号累加,161个乘法器用于系数乘法。这种硬件实现方式确保了滤波器的实时处理能力和高性能。

总结来说,本设计展示了如何通过MATLAB进行FIR滤波器设计,并在FPGA平台上实现,利用其并行处理能力来处理48kHz采样率的音频信号,实现特定的滤波效果。这个过程涉及了信号处理理论、硬件仿真技术和FPGA的底层结构理解,是数字信号处理领域的一个典型应用案例。

2020-04-12 上传

2021-07-13 上传

2020-08-09 上传

2023-06-05 上传

2011-07-05 上传

点击了解资源详情

点击了解资源详情

点击了解资源详情

点击了解资源详情

paozhuanyinyuge

- 粉丝: 0

- 资源: 6

最新资源

- Raspberry Pi OpenCL驱动程序安装与QEMU仿真指南

- Apache RocketMQ Go客户端:全面支持与消息处理功能

- WStage平台:无线传感器网络阶段数据交互技术

- 基于Java SpringBoot和微信小程序的ssm智能仓储系统开发

- CorrectMe项目:自动更正与建议API的开发与应用

- IdeaBiz请求处理程序JAVA:自动化API调用与令牌管理

- 墨西哥面包店研讨会:介绍关键业绩指标(KPI)与评估标准

- 2014年Android音乐播放器源码学习分享

- CleverRecyclerView扩展库:滑动效果与特性增强

- 利用Python和SURF特征识别斑点猫图像

- Wurpr开源PHP MySQL包装器:安全易用且高效

- Scratch少儿编程:Kanon妹系闹钟音效素材包

- 食品分享社交应用的开发教程与功能介绍

- Cookies by lfj.io: 浏览数据智能管理与同步工具

- 掌握SSH框架与SpringMVC Hibernate集成教程

- C语言实现FFT算法及互相关性能优化指南