设计多周期CPU与调试单元:数据通路、控制器与调试功能

需积分: 0 105 浏览量

更新于2024-08-04

收藏 333KB DOCX 举报

在《计算机组成原理实验》的第四次实验中,主题是"Lab4_多周期CPU1",主要目标是让学生深入理解计算机硬件的基本构成,包括数据通路和控制器的工作原理,以及数字系统的设计和调试方法。实验的核心内容围绕一个多周期CPU的设计展开。

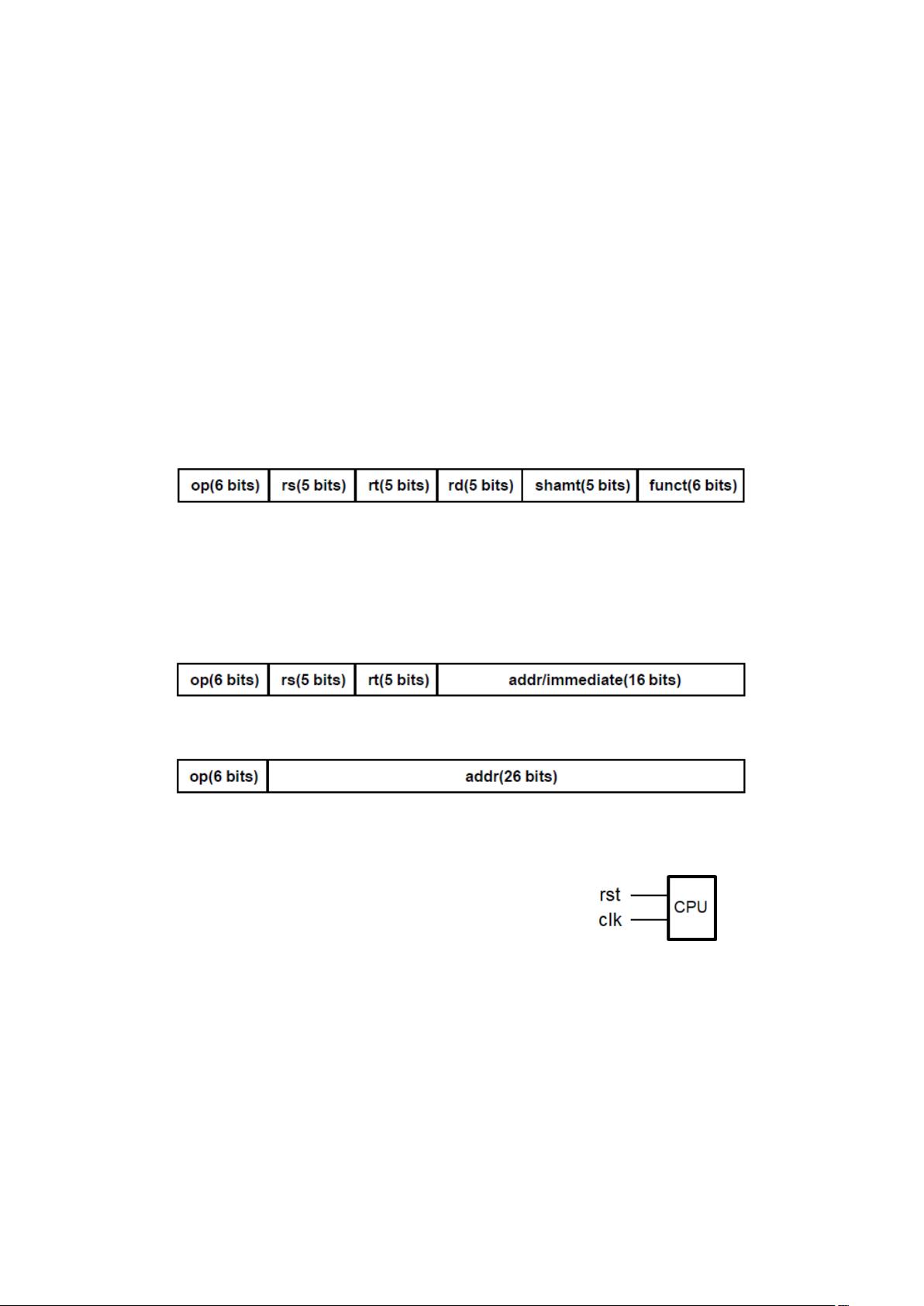

首先,实验中的多周期CPU是一种能执行6条指令(如加法、立即数加法、加载/存储操作、条件跳转和无条件跳转)的处理器。CPU的逻辑符号被模块化表示,如图-1所示,接受时钟信号clk和异步复位rst作为输入。数据通路和控制器的设计至关重要,它们负责指令的解析、控制运算和数据流动,这部分内容在图-2中详细描绘,包括ALU(算术逻辑单元)和寄存器堆的利用,以及共享的RAM存储器,通过IP例化技术实现。

图-3展示了控制器的状态机,它管理着CPU内部的不同状态,确保指令的正确执行顺序。设计者要求实现一个多周期机制,这意味着指令可能需要多个时钟周期来完成,从而提高处理性能。

实验还涉及了调试单元(DBU),这是一个重要的辅助工具,其功能类似于实验三,目的是便于程序下载和调试。DBU与CPU和FPGA开发板的外设(如拨动/按钮开关、LED指示灯和7-段数码管)相连,允许用户控制CPU的运行模式,查看运行过程中的寄存器值和数据存储状态。为了实时监控这些信息,无需中断CPU,额外增加了调试读取端口。

控制CPU运行的方式有两种:当`succ`为1时,clkd输出周期性脉冲,持续驱动CPU执行;而`succ`为0时,通过步进操作,每个step按键触发一个脉冲,使得CPU在单步执行模式下工作。这种设计不仅增强了实验的可调试性,也培养了学生对CPU控制逻辑的理解。

Lab4_多周期CPU1实验着重于让学生亲手构建一个具有多周期执行能力的CPU,并通过调试单元进行深入的硬件调试,这对于理解和掌握计算机硬件设计的基本原理和技术具有重要意义。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2022-08-08 上传

2022-08-03 上传

2022-09-21 上传

2022-08-08 上传

2022-08-04 上传

2021-10-03 上传

马李灵珊

- 粉丝: 41

- 资源: 297

最新资源

- 数字单片机数字单片机

- D语言编程参考手册1.0

- JAVA程序员面试题解惑

- cognos8.12学习资料

- Intel双核与超线程的区别与联系

- 如何编写LINUX 驱动

- Apache与多个Tomcat服务器集成时的负载平衡.txt

- GCC中文手册,详细介绍GCC

- GCC中文手册,详细介绍GCC

- Cross-words Reference Template for DTW-based Speech Recognition Systems

- 一份不太简短的LaTex介绍

- Linux 常用指令大全

- 计算机毕业论文(试题库管理系统)

- 综合电子仿真与设计项目

- XX公司网络设计方案doc

- Oracle Biee Catalog合并

已收录资源合集

已收录资源合集