Vivado设计套件约束使用指南

"VivadoDesignSuite用户指南:使用约束UG903(v2018.3),是一本关于Xilinx FPGA开发中使用Vivado工具进行约束设定的手册,包含了从2018.1到2018.3版本的更新历史。"

在Vivado设计套件中,约束是实现FPGA设计的关键部分,它们定义了设计的时序、布局和布线等关键属性。以下是对Vivado约束手册中几个重要知识点的详细解释:

1. **关于XDC约束**:

XDC(Xilinx Design Constraints)是用于定义FPGA设计约束的文件,它允许设计者指定时钟、I/O、电源、时序异常等特性。手册新增了一个关于`read_xdc`和`source`命令的重要注释,这两个命令用于在设计流程中导入和应用约束。

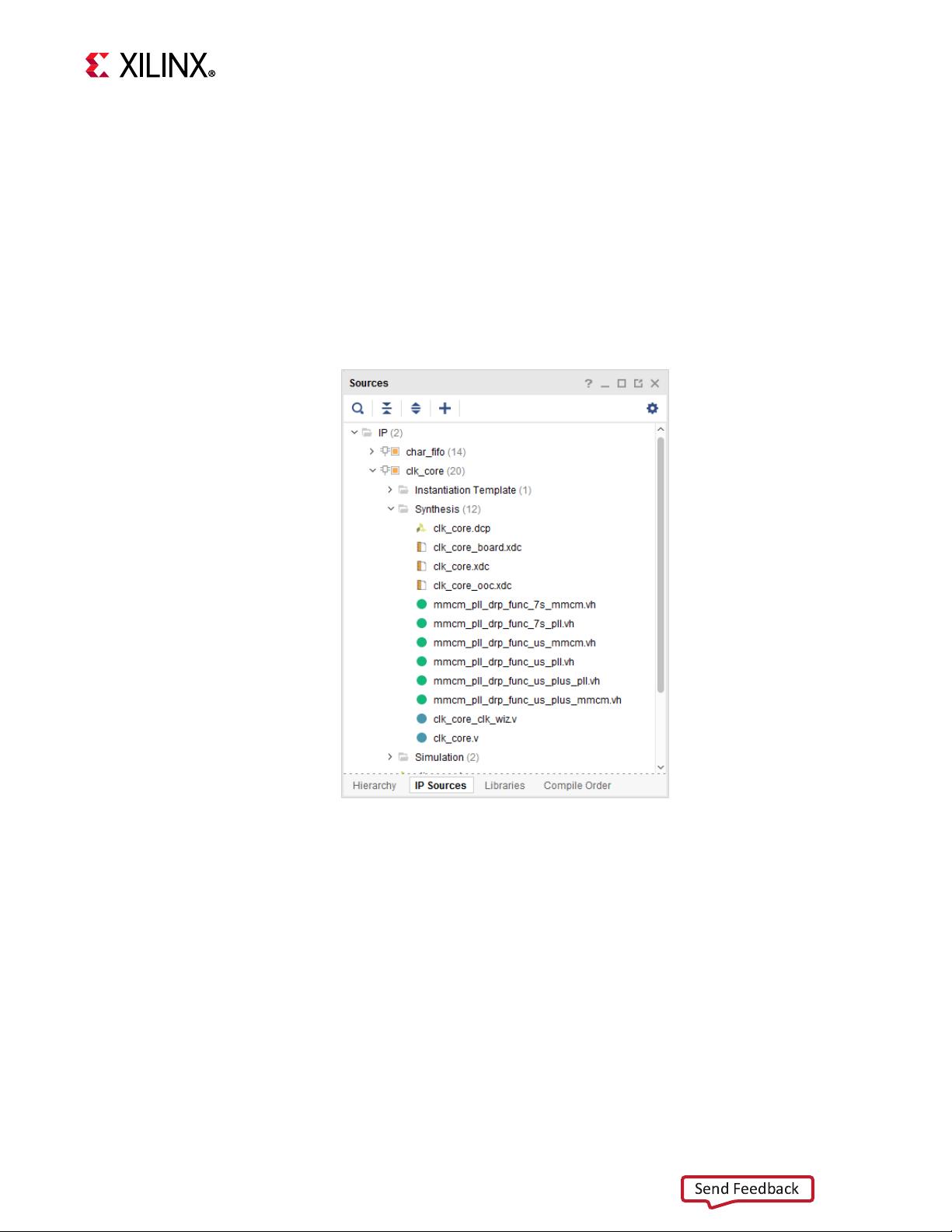

2. **出界上下文约束**:

出界上下文约束是处理大型设计模块时的一个特性,允许在不完全加载整个设计的情况下对部分设计进行约束。2018.3版中新增了一个相关章节,详细介绍了如何在这样的环境下设置约束。

3. **调整针对综合逻辑复制的约束**:

综合过程中可能会出现逻辑复制,以优化设计性能。手册更新了关于`-include_replicated_objects`和`-filter`命令行选项的信息,这些选项可以帮助用户在复制逻辑后正确地处理约束。

4. **替换所有寄存器查询**:

`all_registers`命令用于查询设计中的所有寄存器,手册新增了一个重要注释,指导用户在使用该命令时应考虑的事项。

5. **主时钟**:

主时钟是FPGA设计中的核心时序参考,手册提醒用户在定义主时钟时需要注意的要点,确保时序分析的准确性。

6. **关于时序异常**:

时序异常是设计中可能遇到的时序路径不符合目标性能的情况。手册更新了关于时序异常的表格,提供了更全面的理解和处理方法。

7. **将RPM转换为XDC宏**:

RPM(Routing Parameter Modules)是Xilinx早期的一种约束格式,手册新增了一个章节,指导用户如何将RPM转换为更现代的XDC宏,以兼容Vivado的最新功能。

8. **约束处理顺序和无效约束**:

约束的处理顺序对设计结果有直接影响,手册中讨论了如何组织约束以及当遇到无效约束时应如何处理。

了解并正确应用这些知识点,对于高效且准确地完成Vivado中的FPGA设计至关重要。通过持续学习和更新,开发者可以充分利用Vivado工具的特性,提升设计质量和效率。

点击了解资源详情

点击了解资源详情

点击了解资源详情

127 浏览量

2019-09-10 上传

2023-07-30 上传

2015-11-23 上传

橙色半瓶水

- 粉丝: 134

- 资源: 14

最新资源

- Dreamweaver 快捷键

- Hibernate 开发指南

- The Shellcoders Handbook

- sphinx中文手册

- as3学习资料gdfsd

- QUARTUS警告信息大解析

- imagessegment

- 我自己写的自定义Web的上传控件

- The C++ Standard Library

- 汽车加油问题 对于给定的n和k个加油站位置,编程计算最少加油次数。

- 程序存储问题 对于给定的n个程序存放在磁带上的长度,编程计算磁带上最多可以存储的程序数。

- Principles of Data Mining

- From C++ to Objective-C

- QR码图像处理及识别算法的研究

- 关于软件工程的软件规格说明书

- DirectDraw编程方法与技巧