Vivado约束详解:FPGA设计中的关键路径与时钟管理

需积分: 50 178 浏览量

更新于2024-07-19

8

收藏 1.52MB PDF 举报

Vivado约束指导手册是Xilinx官方提供的全面指南,旨在帮助FPGA设计者解决在设计过程中遇到的各种约束问题。它深入探讨了时序分析在FPGA设计中的重要性,特别是针对时序路径的定义和优化。

时序路径在FPGA设计中至关重要,它由设计中的实例(如逻辑门、触发器等)之间的连接决定。这些路径分为四种类型:输入端口到内部时序单元、内部时序单元间的路径、内部到外部端口的路径以及直接从输入到输出的In-to-out路径。每种路径都有其特定的传输过程和约束要求:

1. 输入端口到内部时序单元路径:数据首先通过器件的时钟引脚,经历输入延时后,通过内部逻辑并最终被目标时钟锁定的时序单元处理。

2. 从时序单元到时序单元的内部路径:数据由源时钟驱动的时序单元发送至器件内部,可能经过一系列内部逻辑,然后被目标时钟驱动的时序单元接收。

3. 内部时序单元到外部端口路径:数据同样由源时钟驱动,经过内部逻辑后,在达到端口之前可能经历输出延时,并由端口时钟捕获。

4. 输入端口到输出端口路径:对于In-to-out路径,数据无需在器件内部存储,直接从输入到输出,这减少了延迟和复杂性。

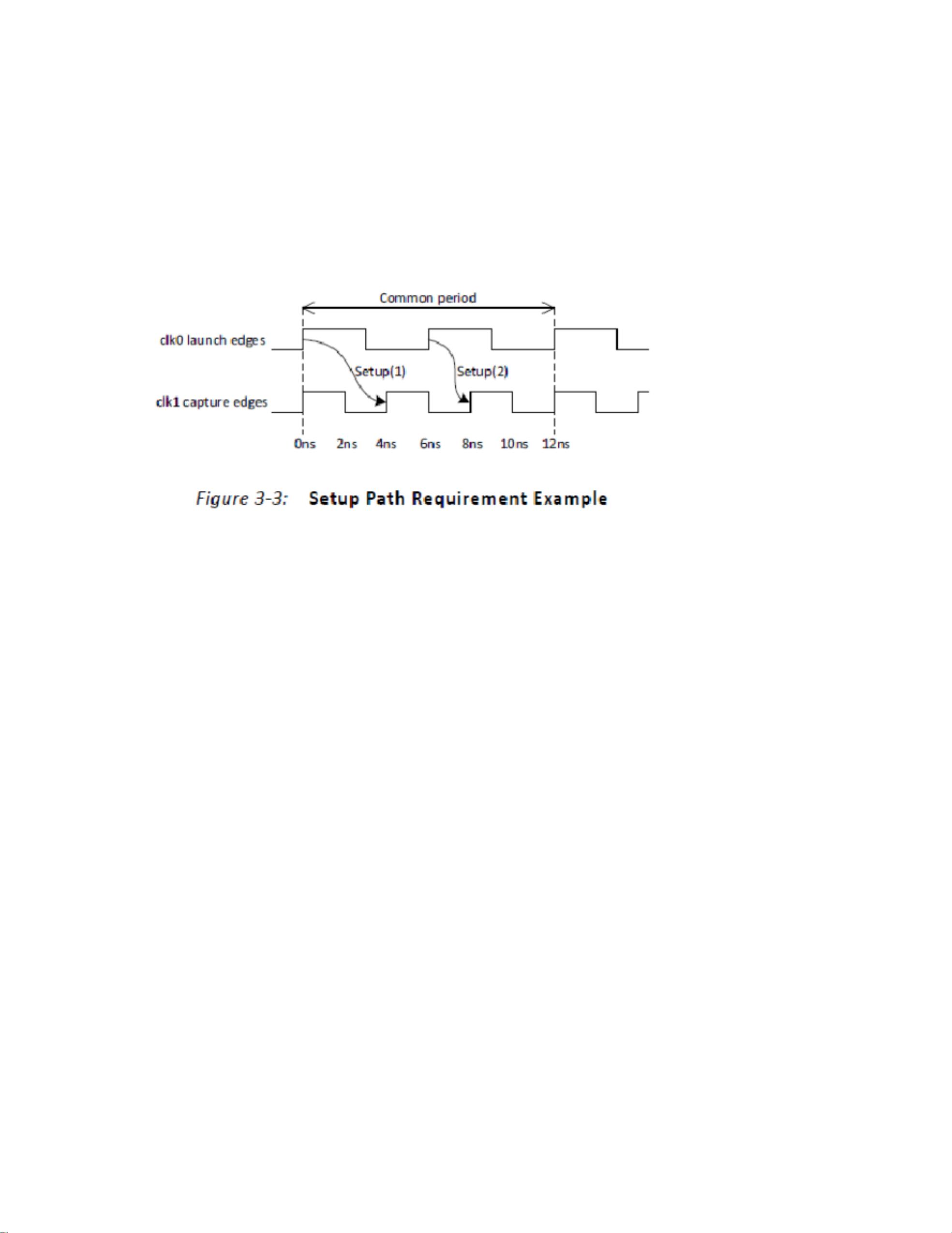

时序路径的分析涉及确定每个路径的延迟,包括源时钟、数据传输和目标时钟的时间特性。Vivado提供了Source Data Clock (SDC)定义来精确地设置这些延迟,确保设计满足系统时序要求。例如,图3-1展示了这些路径的示例,其中设计时钟CLK0可以作为端口时钟,用于约束输入(DIN)和输出(DOUT)的延时。

此外,Vivado约束指导手册还详细解释了时钟路径的构成,包括源时钟路径(从时钟源到发送时序单元的路径)、数据路径(发送和捕捉时序单元之间的连接)以及目标时钟路径(数据到达的目标时钟接收点)。这些元素的精确管理对于维持FPGA设计的性能和稳定性至关重要。

Vivado约束指导手册是设计师在进行FPGA设计时不可或缺的工具,它不仅涵盖了基础的时序路径概念,还提供了实用的指导,帮助用户优化时序约束,确保设计能够高效且稳定地运行。

点击了解资源详情

点击了解资源详情

点击了解资源详情

2023-07-30 上传

2019-09-10 上传

2018-01-23 上传

127 浏览量

2016-05-17 上传