FPGA与AD1836实现的I2S音频接口设计

PDF格式 | 162KB |

更新于2024-08-31

| 99 浏览量 | 举报

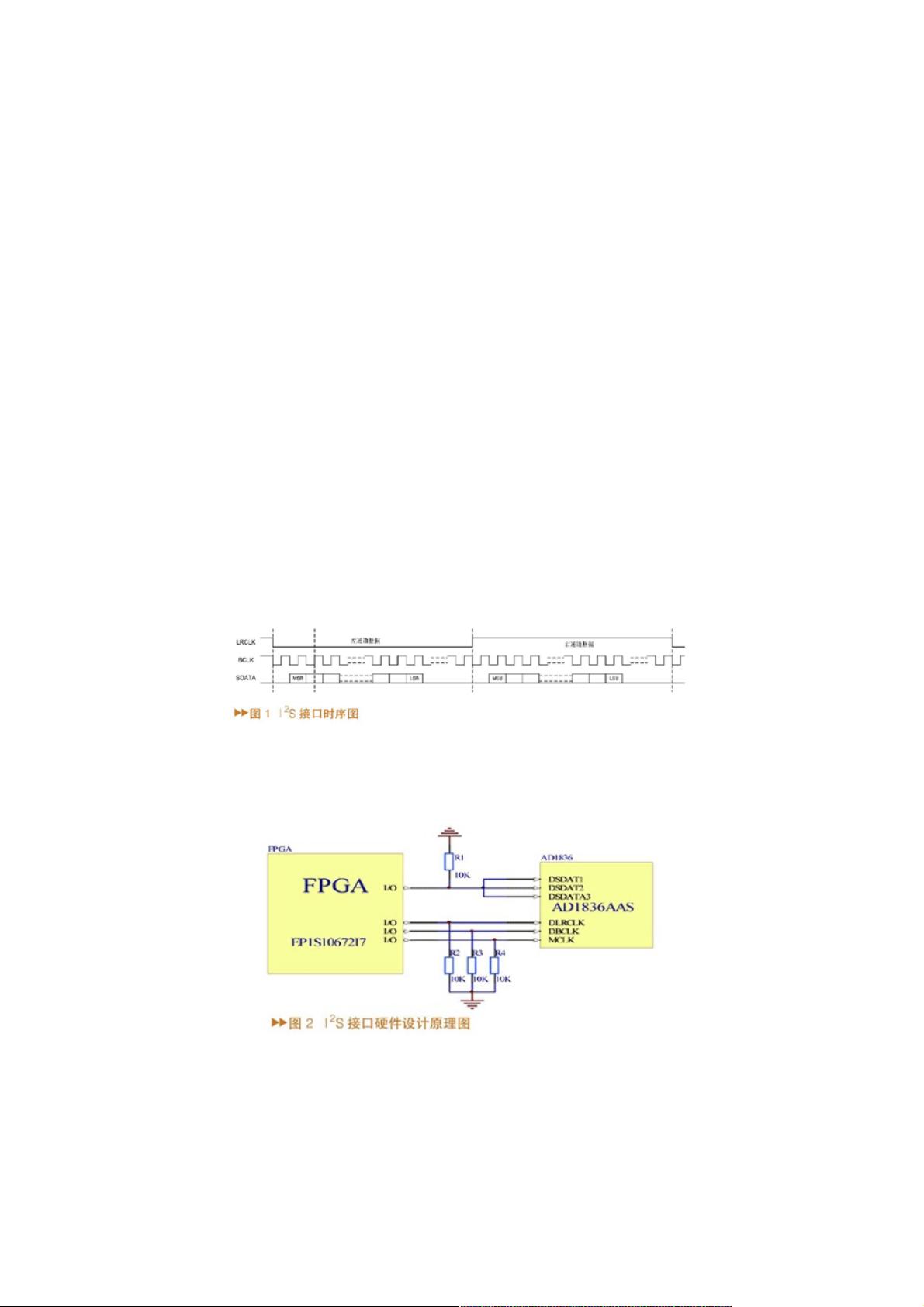

"基于FPGA和AD1836的I2S接口设计,通过FPGA与AD1836的LVTTL电平连接,实现数字音频系统的高精度信号转换。AD1836集成3路D/A和2路A/D,支持I2S接口模式,模拟信号输入输出采用差分形式,降低干扰。本文主要讨论D/A部分的I2S接口设计,涉及I2S总线协议的BCLK、LRCLK和SDATA信号以及数据传输规则。硬件设计中使用Altera的EP1S10672I7 FPGA实现I2S接口。"

在数字音频系统中,FPGA(Field-Programmable Gate Array)常被用来实现复杂的数字信号处理任务,包括与各种外设的接口设计。本文关注的是FPGA与AD1836的交互,AD1836是一款由ADI公司制造的高性能声码器,适合于数字音频应用。这款设备工作在5V电源下,其数字接口与FPGA的LVTTL电平兼容,简化了连接方案。

AD1836的特点包括集成的3个立体声D/A转换器和2个立体声A/D转换器,其参考电压为2.25V。为了减少信号噪声,模拟信号路径采用了差分信号,最大峰峰值为5.6V。其中,AD1836的数字接口支持I2S模式,便于与其它I2S设备通信。

I2S总线协议是一种常见的数字音频数据传输标准,由飞利浦公司定义。协议规定了三个核心信号:BCLK(位时钟)、LRCLK(帧时钟)和SDATA(串行数据)。BCLK确定了数据传输的速率,等于2倍采样率乘以采样位数;LRCLK用于左右声道切换,频率等于采样频率;SDATA则是实际的音频数据流,采用二进制补码表示。MCLK(主时钟)虽然不是必需的,但常用于提高系统同步性,通常为采样频率的256倍或384倍。

在I2S接口的设计中,BCLK的下降沿改变数据,上升沿进行数据采样。接收端和发送端的数据位宽可以不一致,多余或不足的部分会根据情况填充0或被忽略。这种灵活性使得I2S接口能适应多种不同的音频设备。

在硬件实现上,本设计选择Altera的Stratix系列FPGA,具体型号为EP1S10672I7,其1.5V内核电压和3.3V I/O电压与AD1836的要求匹配。设计中D/A部分的I2S接口原理图展示了如何连接并控制这些信号,以实现与AD1836的正确通信。具体到采样时钟设置,通常需要根据实际应用的需求来设定,确保与AD1836的工作模式匹配。

基于FPGA和AD1836的I2S接口设计涉及到了数字音频系统的多个关键方面,包括接口协议的理解、FPGA的逻辑设计以及信号处理的细节,这些都需要精确的计算和精心的布局来确保音频数据的高质量传输。通过这样的设计,可以构建出高效、低噪的数字音频系统,满足各种应用场景的需求。

相关推荐

216 浏览量

weixin_38657465

- 粉丝: 7

最新资源

- 普天身份证阅读器新版二次开发包发布

- C# 实现文件的数据库保存与导出操作

- CkEditor增强功能:轻松实现图片上传

- 掌握DLL注入技术:测试工具使用与探索

- 实现带节假日农历功能的jQuery日历选择器

- Spring循环依赖示例:深入理解与Git代码仓库实践

- ABB PLC液压阀门控制程序开发指南

- 揭秘4核旋风密版626象棋引擎的超牛实力

- HTML5实现的经典游戏:小霸王坦克大战源码分享

- 让Visual Studio兼容APM硬件信息的方法

- Kotlin入门:创建我的第一个应用

- Android语音识别技术研究报告与应用分析

- 掌握JavaScript基础:第8版教程源代码解析

- jQuery制作动态侧面浮动图片广告特效教程

- Android PinView仿支付宝密码输入框源码分析

- HTML5 Canvas制作的围住神经猫游戏源码分享