异步FIFO在EDA/PLD中的设计与实现

173 浏览量

更新于2024-08-30

收藏 258KB PDF 举报

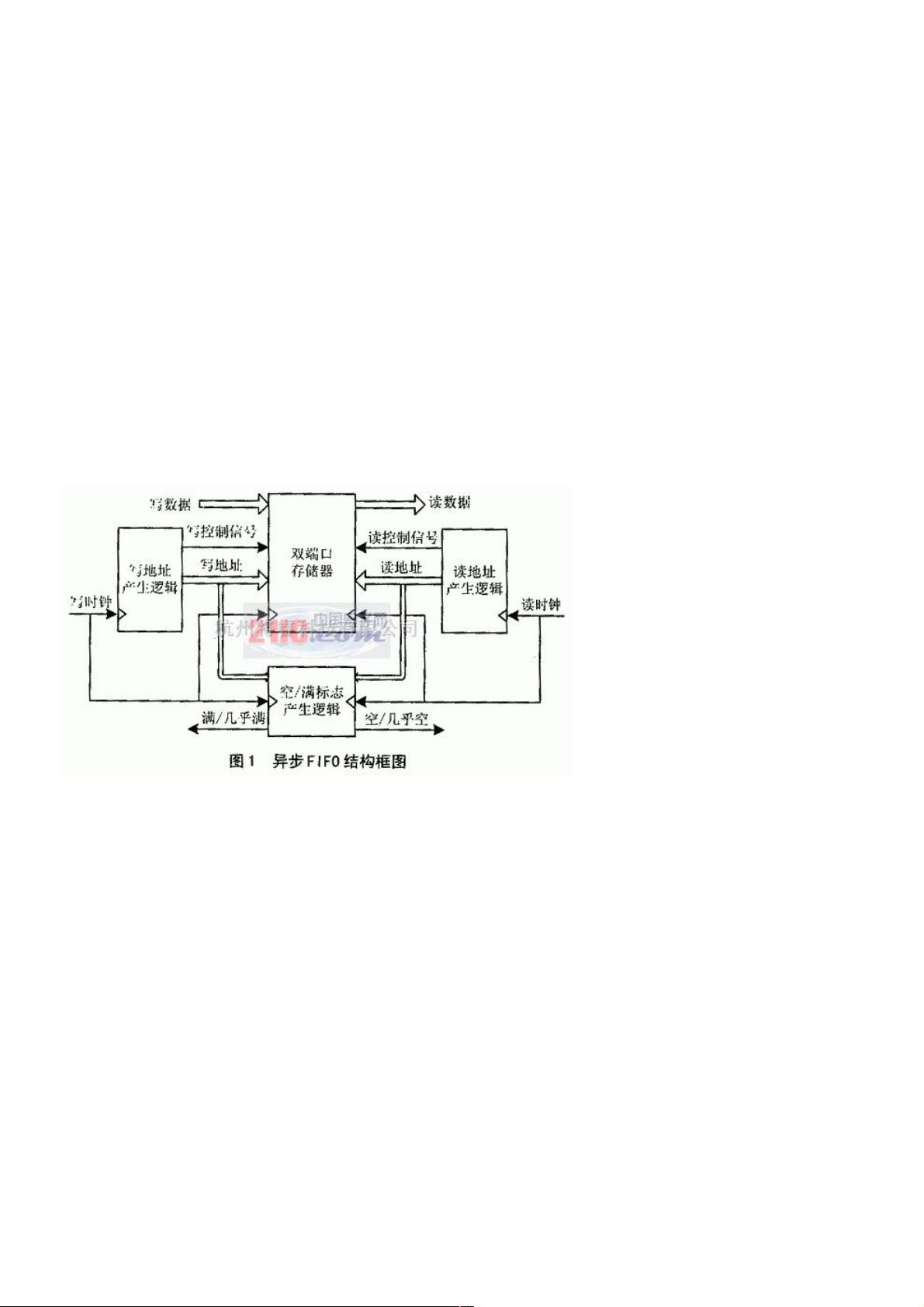

"异步FIFO在现代集成电路设计中扮演着重要的角色,特别是在处理多时钟域数据传输的问题上。这种先进先出的数据缓冲结构能够确保数据在不同时钟速率下的稳定传输,尤其在网络接口和图像处理等领域有广泛应用。本文探讨了异步FIFO的基本概念、应用,以及其在EDA/PLD(电子设计自动化/可编程逻辑器件)中的实现,重点讨论了设计挑战和解决策略。

1. 异步FIFO简介

异步FIFO的核心在于其能在两个不同时钟域之间无缝地传递数据。当系统中有多个独立的时钟源时,数据传输可能会遇到时钟域同步问题,异步FIFO通过内部存储机制解决了这个问题。它使用双端口RAM作为存储介质,允许在读时钟域和写时钟域的同时读写操作,确保数据的连续流动。

2. 设计难点

- 亚稳态的避免:在异步信号的传递中,如果不正确处理,可能导致触发器进入亚稳态,产生不可预测的行为。为解决这个问题,通常采用同步器或格雷码计数器来确保时钟边沿的稳定转换。

- 空/满状态检测:正确设计空、满以及接近满的信号控制至关重要,这需要精确比较读写地址,以防止读写操作间的冲突和数据丢失。通常需要采用比较逻辑和状态机来监测和管理这些状态。

3. 解决方案与实现

文章提出了一个新的电路结构来优化异步FIFO的设计,通过综合仿真验证了其性能,并在FPGA平台上进行了实际实现。这种新结构可能包括改进的同步机制、优化的地址比较逻辑和更高效的状态管理。

4. FPGA实现

FPGA(现场可编程门阵列)因其灵活性和高性能,常被用于实现复杂的数字逻辑,包括异步FIFO。在FPGA上实现异步FIFO需要考虑硬件资源的优化、功耗和速度的平衡,以及适应不同应用场景的可配置性。

5. 结论

通过对异步FIFO的深入理解和创新设计,可以克服多时钟域通信中的挑战,实现高效、可靠的实时数据传输。这种技术对于提高系统性能和降低设计复杂性具有重要意义,特别是在大规模集成电路设计中。

关键词:异步电路、FIFO、亚稳态、格雷码、FPGA设计、双端口RAM、同步器、状态机、数据传输、时钟域同步。"

2020-12-07 上传

2020-12-07 上传

2020-11-17 上传

2020-12-08 上传

2020-12-10 上传

2020-11-27 上传

2020-11-19 上传

2020-12-07 上传

2020-12-01 上传

weixin_38539705

- 粉丝: 6

- 资源: 952

最新资源

- 探索数据转换实验平台在设备装置中的应用

- 使用git-log-to-tikz.py将Git日志转换为TIKZ图形

- 小栗子源码2.9.3版本发布

- 使用Tinder-Hack-Client实现Tinder API交互

- Android Studio新模板:个性化Material Design导航抽屉

- React API分页模块:数据获取与页面管理

- C语言实现顺序表的动态分配方法

- 光催化分解水产氢固溶体催化剂制备技术揭秘

- VS2013环境下tinyxml库的32位与64位编译指南

- 网易云歌词情感分析系统实现与架构

- React应用展示GitHub用户详细信息及项目分析

- LayUI2.1.6帮助文档API功能详解

- 全栈开发实现的chatgpt应用可打包小程序/H5/App

- C++实现顺序表的动态内存分配技术

- Java制作水果格斗游戏:策略与随机性的结合

- 基于若依框架的后台管理系统开发实例解析