Altera PCIE硬核IP设计与DMA应用解析

"本文档主要介绍了如何在Altera FPGA中使用PCI Express (PCIE) 技术,涵盖了PCIE系统的基本拓扑结构、Altera PCIE硬核的关键特性,以及基于Qsys的设计流程。同时,提到了Windriver驱动的使用以及SGDMA在实现DMA操作中的作用。"

Altera PCI Express (PCIE) 是一种高速接口技术,用于在FPGA和外部设备之间建立高效的数据传输通道。在介绍PCIE系统之前,先要理解其基本的拓扑结构。PCIE采用点对点连接,如图1-1所示,包括Root Complex(根复合体)、Switch、Endpoint(如I/O或存储设备)以及PCIE到PCI/PCI-X的桥接。这种结构允许独立的数据传输,提高了系统的带宽和性能。

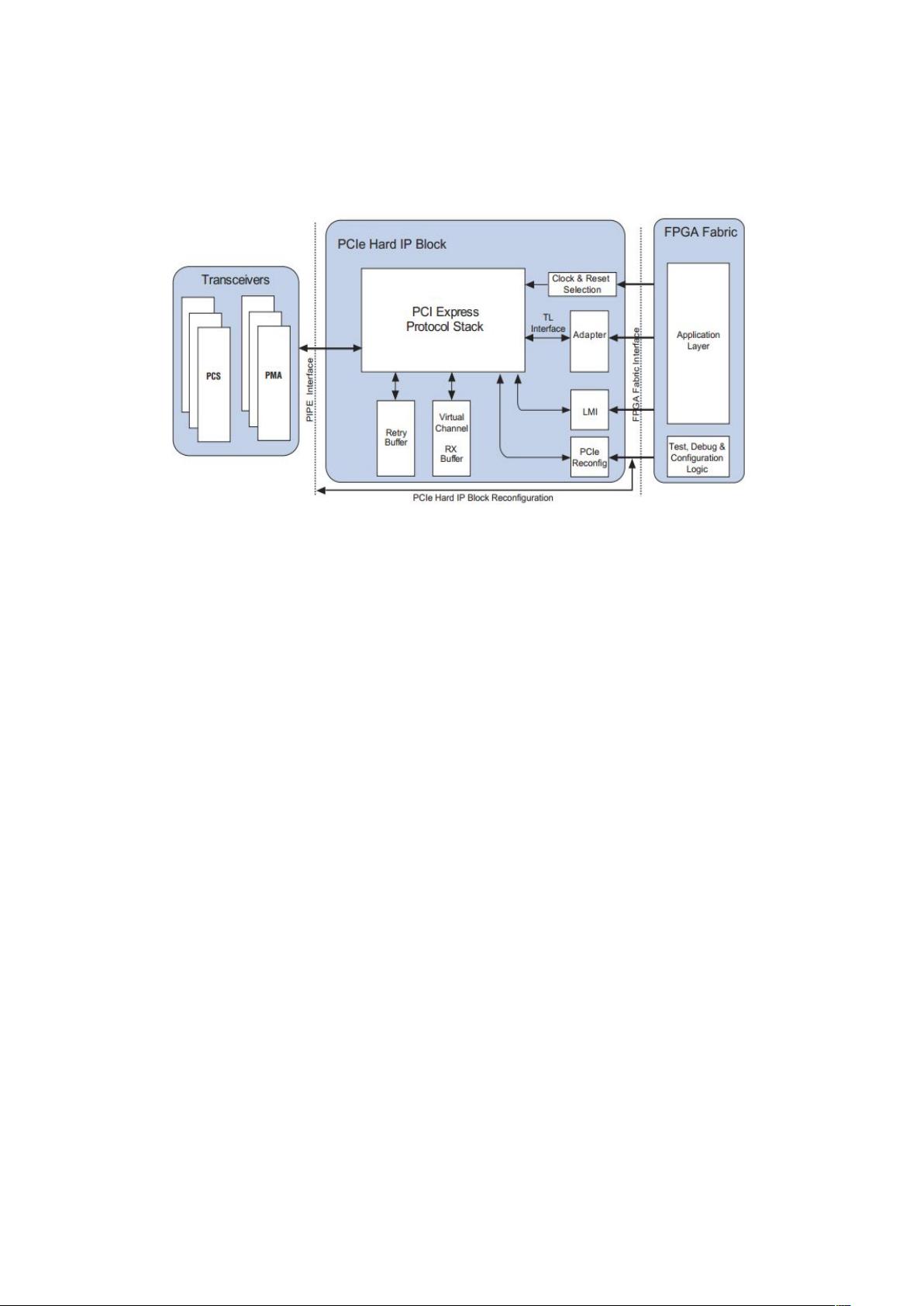

Altera的PCIE硬核IP是实现PCIE功能的核心,它可以配置为Root Port (RP) 或 Endpoint (EP) 模式。在本文档中,它被用作Endpoint模式。硬核包含了Physical、Datalink和Transaction三层协议,支持设备配置空间、收发缓冲和流控制等功能。Avalon-MM或Avalon-ST接口用于与应用层交互,LMI接口则用于访问配置空间,而PCIeReconfig接口用于硬核及其相关GX模块的重配置。

在板级系统设计部分,如图2-1所示,系统包括了FPGA中的Qsys生成的Endpoint和PC端的Windriver驱动。Windriver驱动使得PC能对FPGA进行配置读写和存储读写操作,但这种方式可能会占用大量CPU资源并降低速度。为了解决这个问题,系统引入了DMA(直接存储器访问)机制。在DMA操作中,FPGA作为主设备发起读写请求,直接与PC的物理内存进行数据交换,提高传输效率。

在实际应用中,SGDMA(System Generator for Direct Memory Access)经常用于实现DMA控制器,它可以处理从FPGA到PC或反之的大量数据传输,无需CPU干预。使用SGDMA,用户可以设计出高效的数据传输路径,从而优化系统性能。

本文档提供了关于Altera FPGA中实施PCIE的基本知识,包括设计流程、关键组件和接口,以及如何利用DMA优化数据传输。对于想要在Altera FPGA中构建PCIE系统的工程师来说,这是一个重要的参考资料。虽然没有包含详细的每步操作指南,但它概述了主要概念和技术,有助于快速理解和启动PCIE项目。

点击了解资源详情

点击了解资源详情

点击了解资源详情

138 浏览量

2022-07-14 上传

2022-09-23 上传

2022-07-15 上传

123 浏览量

2022-09-24 上传

yangshuhe33

- 粉丝: 1

- 资源: 8

最新资源

- Sane time.:合理的自动时间跟踪。-开源

- 一个简单的图库项目

- Nik_Collection_4.0.7.0_Multilingualx64.rar

- netfil:一个内核网络管理器,具有针对macOS的监视和限制功能。 #nsacyber

- SCAN_tests

- 图像浏览器

- C# MQTTNET示例

- music_edit:DOS音乐编辑器-开源

- 海岸线工具_python_

- 机器学习经典二分类数据集——马疝病数据集.zip

- redalert:不断测试所有内容-触发故障警报

- SAM:SAM是专门为维也纳大学计算机科学学院服务器设计的多功能Discord Bot

- SAP SuccessFactors Only: Display Full Name-crx插件

- POS票据打印机.zip

- Android-Bazel-Starter-Kotlin

- APx500_4.5.1_w_dot_Net 音频分析仪软件 apx515 apx525