Electrical Characteristics (Continued)

The following specifications apply for V

CC

ea

5.0V, V

REF

ea

4.6V, f

S

e

700 kHz, and f

C

e

3 MHz unless otherwise

specified. Boldface limits apply for T

A

e

T

J

e

T

MIN

to T

MAX

; all other limits T

A

e

T

J

e

25

§

C.

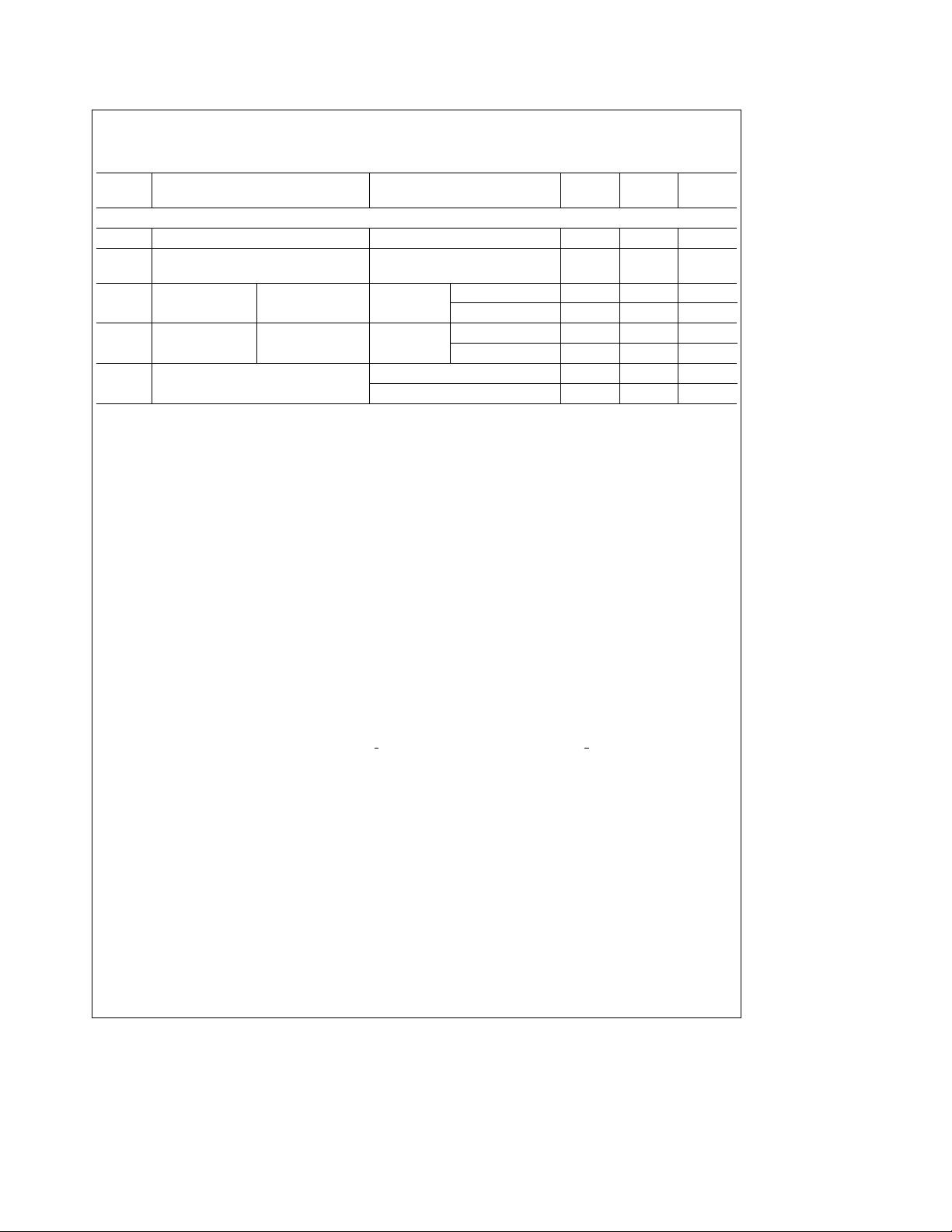

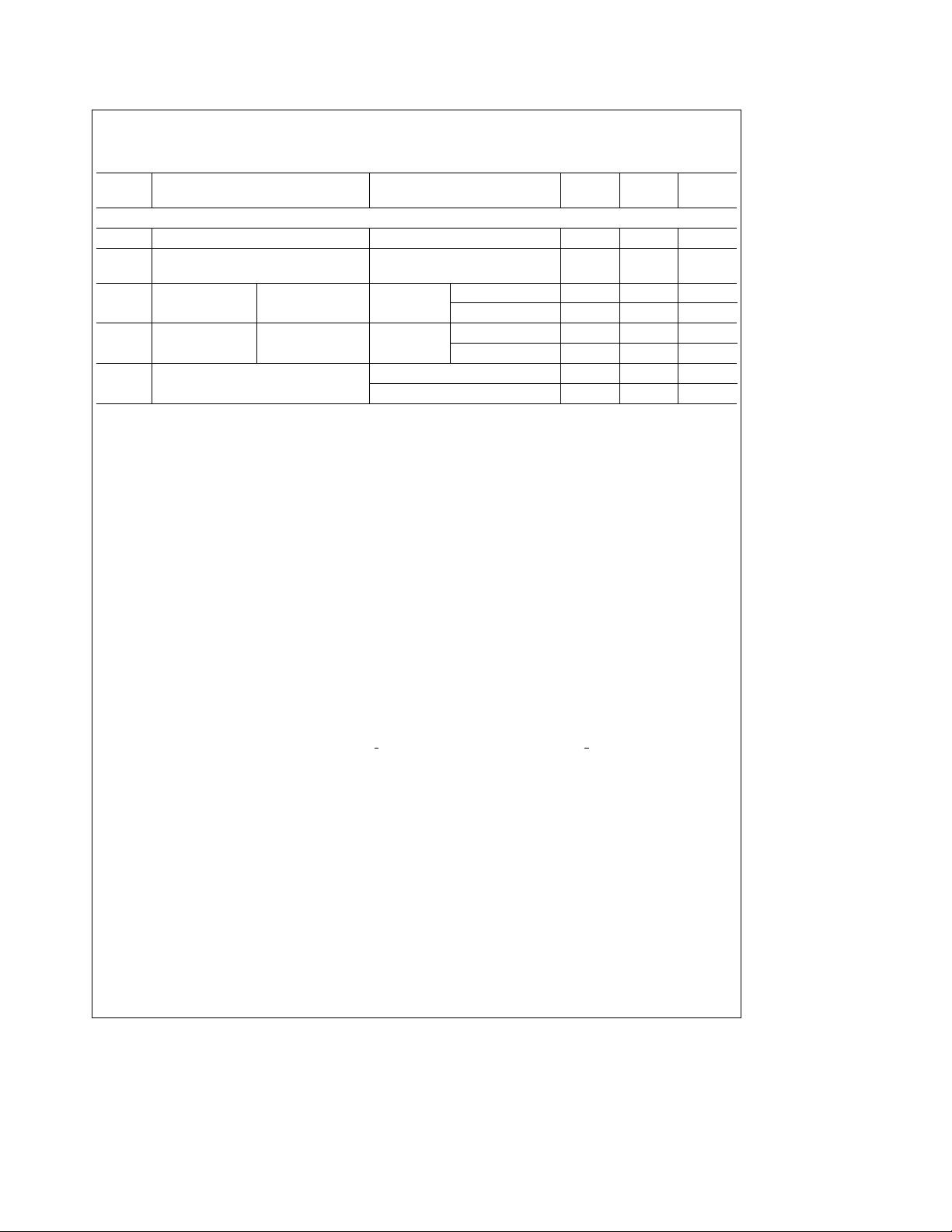

Symbol Parameter Conditions

Typical Limit Units

(Note 8) (Note 9) (Limits)

AC CHARACTERISTICS (Continued)

t

HDO

DO Hold Time from S

CLK

Falling Edge R

L

e

30 kX,C

L

e

100 pF 70 10 ns (min)

t

DDO

Delay from S

CLK

Falling R

L

e

30 kX,C

L

e

100 pF

150 250 ns (max)

Edge to DO Data Valid

t

RDO

DO Rise Time R

L

e

30 kX, TRI-STATE to High 35 75 ns (max)

C

L

e

100 pF

Low to High 75 150 ns (max)

t

FDO

DO Fall Time R

L

e

30 kX, TRI-STATE to Low 35 75 ns (max)

C

L

e

100 pF

High to Low 75 150 ns (max)

C

IN

Input Capacitance Analog Inputs (CH0– CH7) 50 pF

All Other Inputs 7.5 pF

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur.

Note 2: Operating Ratings indicate conditions for which the device is functional, but do not guarantee specific performance limits. For guaranteed specifications

and test conditions, see the Electrical Characteristics. The guaranteed specifications apply only for the test conditions listed. Some performance characteristics

may degrade when the device is not operated under the listed test conditions.

Note 3: All voltages are measured with respect to AGND and DGND, unless otherwise specified.

Note 4: When the input voltage (V

IN

) at any pin exceeds the power supplies (V

IN

k

DGND, or V

IN

l

V

CC

) the current at that pin should be limited to 5 mA. The

20 mA maximum package input current rating limits the number of pins that can safely exceed the power supplies with an input current of 5 mA to four pins.

Note 5: The maximum power dissipation must be derated at elevated temperatures and is dictated by T

Jmax

, i

JA

and the ambient temperature, T

A

. The maximum

allowable power dissipation at any temperature is P

D

e

(T

Jmax

b

T

A

)/i

JA

or the number given in the Absolute Maximum Ratings, whichever is lower. For this

device, T

Jmax

e

125

§

C. The typical thermal resistance (i

JA

) of these parts when board mounted follow: ADC1031 with CIN suffixes 71

§

C/W, ADC1034 with CMJ

suffixes 52

§

C/W, ADC1034 with CIN suffixes 54

§

C/W, ADC1034 with CIWM suffixes 70

§

C/W, ADC1038 with CMJ suffixes 53

§

C/W, ADC1038 with CIN suffixes

46

§

C/W, ADC1038 with CIWM suffixes 64

§

C/W.

Note 6: Human body model, 100 pF capacitor discharged through a 1.5 kX resistor.

Note 7: See AN450 ‘‘Surface Mounting Methods and Their Effect on Product Reliability’’ or

Linear Databook

section ‘‘Surface Mount’’ for other methods of

soldering surface mount devices.

Note 8: Typicals are at T

J

e

25

§

C and represent most likely parametric norm.

Note 9: Limits are guaranteed to National’s AOQL (Average Outgoing Quality Level).

Note 10: Total unadjusted error includes offset, full-scale, linearity, multiplexer, and hold step errors.

Note 11: Two on-chip diodes are tied to each analog input. They will forward-conduct for analog input voltages one diode drop below ground or one diode drop

greater than V

CC

supply. Be careful during testing at low V

CC

levels (4.5V), as high level analog inputs (5V) can cause an input diode to conduct, especially at

elevated temperatures, which will cause errors for analog inputs near full-scale. The spec allows 50 mV forward bias of either diode; this means that as long as the

analog V

IN

does not exceed the supply voltage by more than 50 mV, the output code will be correct. Exceeding this range on an unselected channel will corrupt the

reading of a selected channel. To achieve an absolute 0 V

DC

to5V

DC

input voltage range will therefore require a minimum supply voltage of 4.950 V

DC

over

temperature variations, initial tolerance and loading.

Note 12: Channel leakage current is measured after the channel selection.

Note 13: In order to synchronize the serial data exchange properly, SARS needs to go low after completion of the serial I/O data exchange. If this does not occur

the output shift register will be reset and the correct output data lost. The minimum limit for S

CLK

will depend on C

CLK

frequency and whether right-justified or left-

justified, and can be determined by the following equations:

f

S

l

(8.5/41) (f

C

) with right-justification (R/L

e

‘‘1’’) and f

S

l

(2.5/41) (f

C

) with left-justification (R/L

e

‘‘0’’).

4

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

信息提交成功

信息提交成功