基于基于VLSI平台的平台的MIPS处理器仿真与设计处理器仿真与设计

摘要:传统ISA处理器由于其内部有限的逻辑资源和外部固定的引脚封装,大大地限制了它的应用范围。使用硬

件描述语言,自底向上设计处理MIPS,并且与几类通用外设互连组成系统,使用Virtex-Ⅱ Pro系列FPGA进行板级

验证。 板级验证结果表明实现了既定目标,与标准MCU 兼容,系统运行稳定。这样可以依据自己的需求,

定制系统以达到传统MCU所无法完成的要求。 0 引言 随着社会的发展,工业控制及人们日常生活越来

越追求精密控制,为了满足这种需求,微控制器得到了快速的发展。随着VLSI 发展,MCU 将原本分散的

CPU,RAM,ROM,I/O等集中于一块单晶芯片内,形成一种芯片级计

摘要:传统ISA处理器由于其内部有限的逻辑资源和外部固定的引脚封装,大大地限制了它的应用范围。使用硬件描述语

言,自底向上设计处理MIPS,并且与几类通用外设互连组成系统,使用Virtex-Ⅱ Pro系列FPGA进行板级验证。

板级验证结果表明实现了既定目标,与标准MCU 兼容,系统运行稳定。这样可以依据自己的需求,定制系统以达到传统

MCU所无法完成的要求。

0 引言

随着社会的发展,工业控制及人们日常生活越来越追求精密控制,为了满足这种需求,微控制器得到了快速的发展。随着

VLSI 发展,MCU 将原本分散的CPU,RAM,ROM,I/O等集中于一块单晶芯片内,形成一种芯片级计算系统。MCU 主要用于控

制目的,MCU 构成的系统有实时、快速的外部响应,能迅速采集到大量的数据,做出逻辑判断与推理后实现对被控制对象的

参数调整与控制。

但是随着时代的推进,对控制的要求逐步增大,所需满足功能的逐渐增多,传统MCU 也越来越显得捉襟见肘。尤其是面

对现代SoC 的挑战。为此,使用ASIC器件在片内实现与传统MCU 相兼容的,选用合适的片内总线来连接外设,构成一个兼容

传统MCU平台,这种方法必会延续传统MCU 的生命力,使其获得更大的发展。

1 Virtex-Ⅱ Pro

Virtex-Ⅱ Pro系列在Virtex-Ⅱ的基础上,增强了嵌入式处理能力,内嵌PowerPC405内核,还包括了先进的主动互联技术,

以解决高性能系统所面临的挑战。此外还增加了高速串行收发器,提供了千兆以太网的解决方案。主要特征如下:

(1)核电压为1.5 V,工作时钟可以达到420 MHz;(2)支持多达20种的I/O接口标准;(3)增加了2个高性能RISC技术,

频率高达400 MHz的PowerPC处理器;(4)增加多个3.125 Gb/s 速率的Rocket 串行收发器;(5)内嵌了多个硬核乘法器,

提高了DSP处理能力;(6)具有完全系统时钟管理功能,多达8个DCM.

2 Virtual MIPS Core 实现

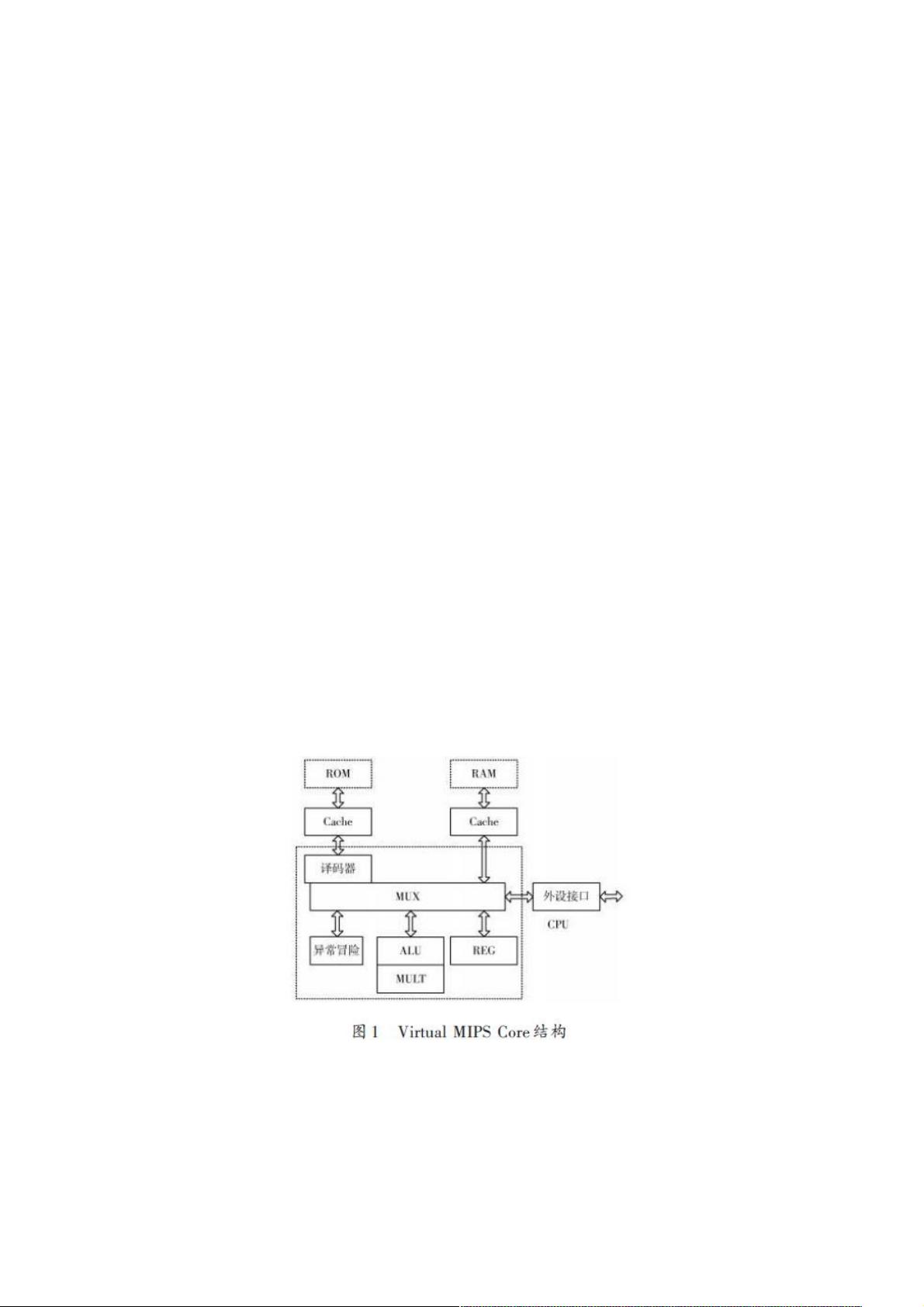

Virtual MIPS Core 依据MIPS 公司的32 位处理器R3000实现,采用3级流水线技术,其结构如图1所示。

主要分为:CPU模块、Cache模块和外设总线接口模块。

其中CPU模块实现了MIPS R3000处理器中简单的CP0功能,由总线控制机构、流水线机构、冒险处理机构、异常处理机

构、运算机构和译码机构等组成。

2.1 总线控制机构

Virtual MIPS Core采用哈佛结构,有三条分离的总线:程序总线、数据读总线和数据写总线。采用该种总线方式允许

CPU在执行操作码时对数据进行读取或写入操作。这完全避免了冯诺依曼瓶颈,大大提高了系统的速率,而且在实现也较为

简单,重要的是,允许连接高速缓存(Cache)。但是数据读总线和数据写总线共用一组地址总线,这点使得无法在同一时刻

进行数据的存储和读取操作,造成了一定的限制。