Verilog实现的单周期CPU设计详解

需积分: 50 21 浏览量

更新于2024-07-22

收藏 4.99MB PPT 举报

"这篇文档主要介绍了单周期CPU的设计原理,特别是使用Verilog HDL进行实现。文档涵盖了CPU的基本构成部分,如控制单元、ALU、数据路径和I/O接口,并详细解析了单周期CPU的执行流程,包括指令的读取、分析、执行以及中断处理。此外,还提到了MIPS指令格式的三种类型:IFormat、RFormat和JFormat。"

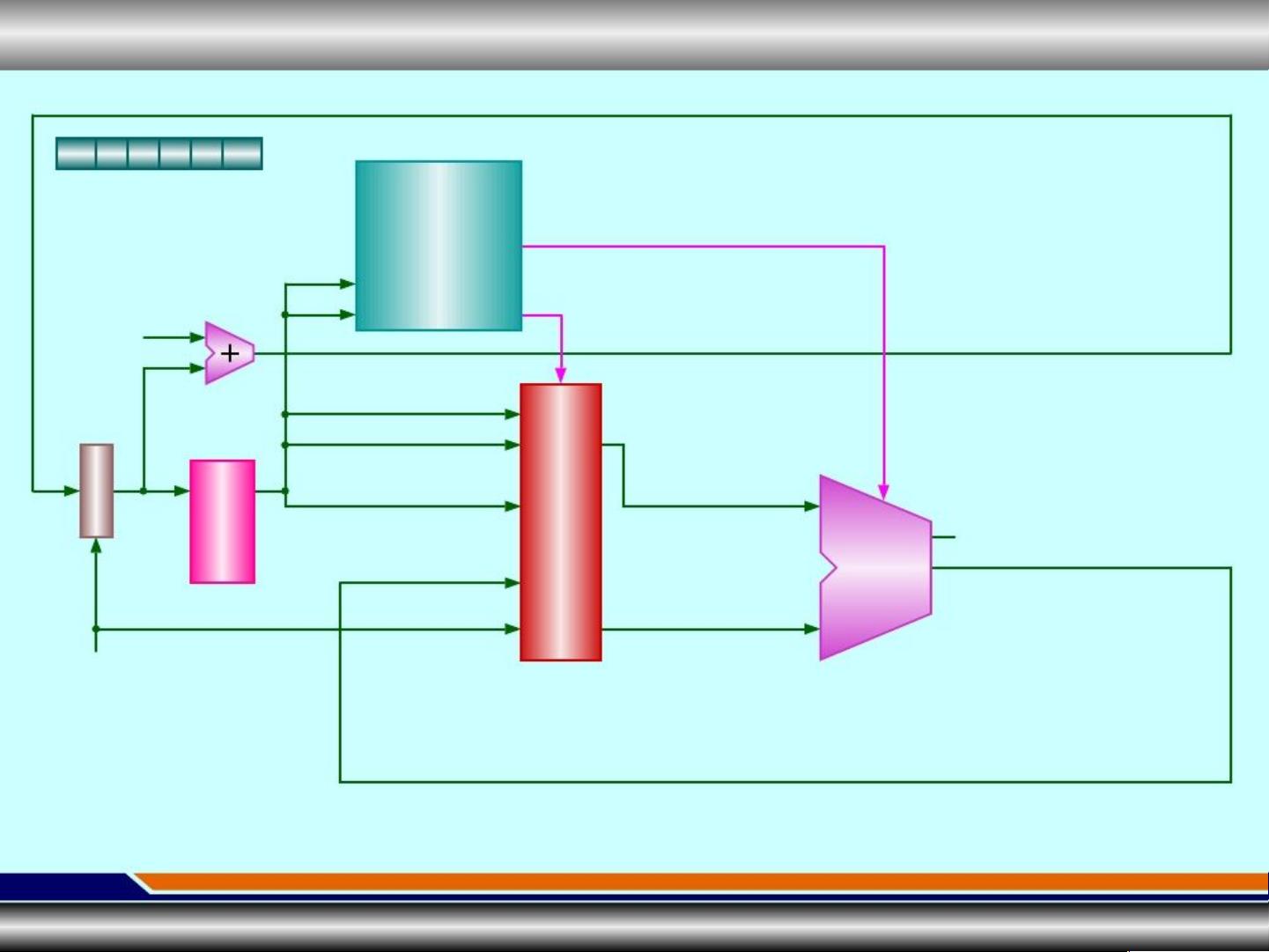

单周期CPU设计是计算机体系结构中的一个重要概念,它的核心特性是在一个时钟周期内完成一条指令的全部操作,从而提高处理速度。CPU主要由以下几个部分组成:

1. **控制单元(Control Unit)**:负责解析指令并生成必要的控制信号来协调整个系统的操作。

2. **算术逻辑单元(ALU)**:执行基本的算术和逻辑运算,如加法、减法、与、或、异或等。

3. **寄存器堆**:存储中间结果和数据,如通用寄存器、程序计数器(PC)等。

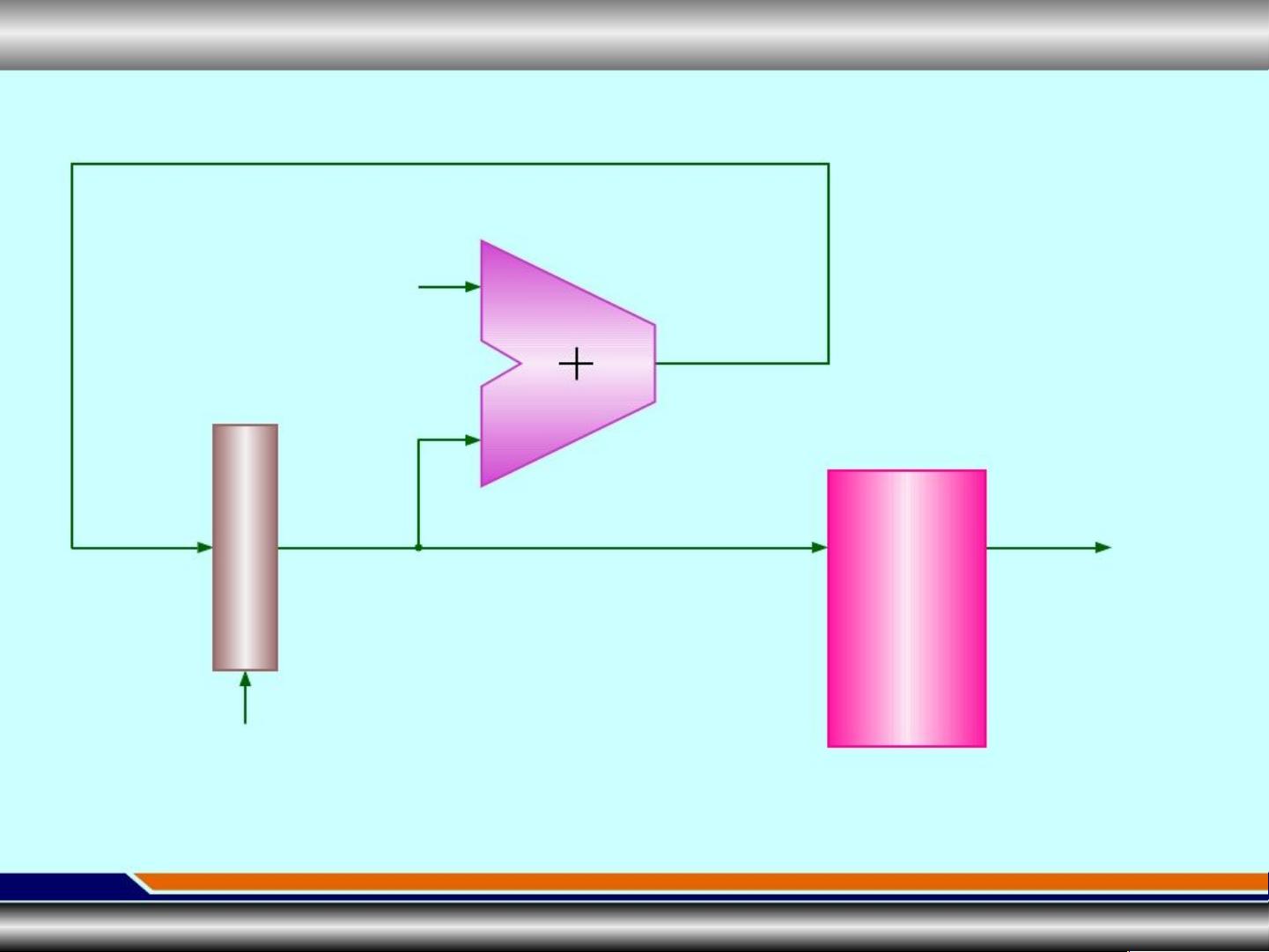

4. **多路选择器**:在数据路径中用于选择不同来源的数据。

5. **数据路径(Datapath)**:包含ALU、寄存器堆和多路选择器等,形成数据在CPU内部的流动路径。

6. **I/O接口**:连接CPU与外部设备,进行数据交换。

单周期CPU的执行过程包括以下步骤:

1. **取指令**:在时钟上升沿,通过程序计数器(PC)获取内存中的指令地址,并读取指令。

2. **指令解码**:分析指令,确定操作类型和涉及的寄存器。

3. **执行指令**:使用ALU执行指令指定的操作,如加法、逻辑运算等。

4. **检查中断**:如果无中断请求,更新PC以执行下一条指令;如果有中断,中断处理程序将接管执行流程。

5. **形成下一条指令地址**:通常情况下,PC会自动增加4(对于32位指令系统),以指向下一个指令。

MIPS指令格式是单周期CPU可能采用的一种指令集架构,它包括:

- **IFormat**:用于立即数操作,包含操作码(op)、源寄存器(rs)、目的寄存器(rt)和16位立即数(imm)。

- **RFormat**:用于寄存器操作,包含操作码(op)、源寄存器(rs)、源寄存器(rt)、目的寄存器(rd)和功能码(funct)。

- **JFormat**:用于跳转操作,包含操作码(op)和26位目标地址(addr)。

例如,MIPS指令`add R1, R2, R3`表示将R2和R3中的数据相加,结果存储在R1中;而`lwr R4, 100(R5)`则表示从内存地址R5+100处读取数据并存储到R4中。

单周期CPU设计旨在简化指令执行流程,提高处理器效率,而Verilog HDL是一种常用的硬件描述语言,用于实现这种复杂逻辑的硬件电路。理解这些基础知识对进行微处理器设计和计算机系统架构的学习至关重要。

2018-08-08 上传

112 浏览量

2024-05-19 上传

2023-12-07 上传

2023-05-02 上传

2024-05-21 上传

2023-05-01 上传

2023-02-15 上传

2023-06-13 上传

qq_21097923

- 粉丝: 0

- 资源: 2

最新资源

- C++多态实现机制详解:虚函数与早期绑定

- Java多线程与异常处理详解

- 校园导游系统:无向图实现最短路径探索

- SQL2005彻底删除指南:避免重装失败

- GTD时间管理法:提升效率与组织生活的关键

- Python进制转换全攻略:从10进制到16进制

- 商丘物流业区位优势探究:发展战略与机遇

- C语言实训:简单计算器程序设计

- Oracle SQL命令大全:用户管理、权限操作与查询

- Struts2配置详解与示例

- C#编程规范与最佳实践

- C语言面试常见问题解析

- 超声波测距技术详解:电路与程序设计

- 反激开关电源设计:UC3844与TL431优化稳压

- Cisco路由器配置全攻略

- SQLServer 2005 CTE递归教程:创建员工层级结构