Vivado下AXI DMA的FPGA设计与实现

AXI DMA LOOP Vivado建立BD详细过程

AXI DMA 传输测试是指使用 Vivado 工具建立基于 ZYNQ IP 的 DMA 传输测试系统。该系统主要包括以下几个部分:FPGA 板设计、DMA 传输测试、软件分析。

一、FPGA 板设计

FPGA 板设计是指使用 Vivado 工具建立 FPGA 板的设计。步骤如下:

1. 新建一个名为 Miz_sys 的工程。

2. 创建一个 BD 文件,并命名为 system,添加并且配置好 ZYNQ IP。

3. 读者需要根据自己的硬件类型配置好输入时钟频率、内存型号、串口,连接时钟等。

4. 勾选 FCLK_CLK0,设置为 100,即 PS 的 PLL 提供本系统的时钟 100MHZ。

5. 单击 OK。

6. 双击 DMA IP,设置如下。

- 勾选读通道;

- 勾选写通道;

- 设置 Widehofbufferlengthregister:14。(寄存器设置最大为 23,即 2 的 23 次方 8,388,607 bytes,8M 大小,这里设置 14bit 就够用了,长度越大,需要的资源也就越多)

7. DataFIFO 设置:

- 设置 TDATAWidth 为 4。

8. ConcatIP 设置:

- 实现了单个分散的信号,整合成总线信号。

- 这里,将 2 个独立的中断信号,合并在一起连接到 ZYNQ IP 的中断信号接口上。

- 设置:

- NumberofPorts:2

- In0Width:1

- In1Width:1

- DoutWidth:2

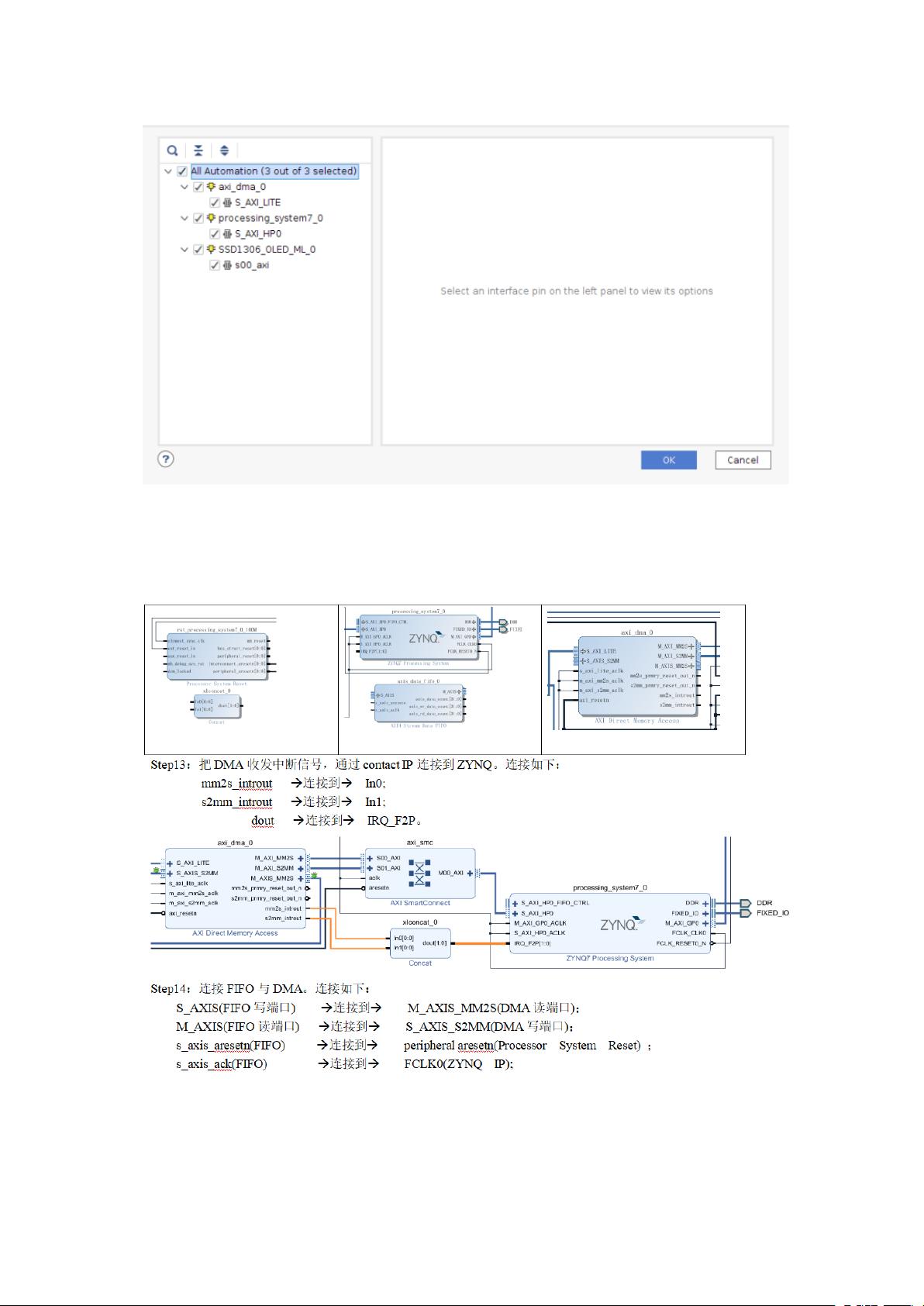

9. 点击 RunBlockAutomation,自动配置 ZYNQ IP。

10. 点击 RunConnectionAutomation 自动连线。

11. 如果还有提示需要自动连线的继续让软件自动连线,直到出下如下。

二、DMA 传输测试

DMA 传输测试是指使用 AXI DMA 传输测试函数 int axi_dma_test(),该函数的功能是实现 AXI DMA 传输测试。

DMA 传输测试的实现步骤如下:

1. 新建一个名为 AXI_DMA_Test 的空的软件工程

2. 将提供例程中 SDK 工程的源文件复制,并粘贴到新建 SDK 工程,软件会自动编译。

3. 在 main.c 源码中,函数分析 1:

- 函数名:int init_intr_sys(void);

- 功能:对中断资源的初始化,使能中断资源。

- 说明:这个函数里面调用的函数是笔者封装好的初始化函数。

三、软件分析

软件分析是指对 SDK 工程的源文件进行分析。步骤如下:

1. 新建一个名为 AXI_DMA_Test 的空的软件工程

2. 将提供例程中 SDK 工程的源文件复制,并粘贴到新建 SDK 工程,软件会自动编译。

3. 在 main.c 源码中,函数分析 1:

- 函数名:int init_intr_sys(void);

- 功能:对中断资源的初始化,使能中断资源。

- 说明:这个函数里面调用的函数是笔者封装好的初始化函数。

AXI DMA 传输测试是使用 Vivado 工具建立基于 ZYNQ IP 的 DMA 传输测试系统,包括 FPGA 板设计、DMA 传输测试、软件分析三个部分。

2012-04-15 上传

2017-05-03 上传

2022-08-08 上传

2020-11-24 上传

2022-09-20 上传

2022-07-15 上传

点击了解资源详情

2023-03-30 上传

两斤香菜

- 粉丝: 18

- 资源: 297

最新资源

- Aspose资源包:转PDF无水印学习工具

- Go语言控制台输入输出操作教程

- 红外遥控报警器原理及应用详解下载

- 控制卷筒纸侧面位置的先进装置技术解析

- 易语言加解密例程源码详解与实践

- SpringMVC客户管理系统:Hibernate与Bootstrap集成实践

- 深入理解JavaScript Set与WeakSet的使用

- 深入解析接收存储及发送装置的广播技术方法

- zyString模块1.0源码公开-易语言编程利器

- Android记分板UI设计:SimpleScoreboard的简洁与高效

- 量子网格列设置存储组件:开源解决方案

- 全面技术源码合集:CcVita Php Check v1.1

- 中军创易语言抢购软件:付款功能解析

- Python手动实现图像滤波教程

- MATLAB源代码实现基于DFT的量子传输分析

- 开源程序Hukoch.exe:简化食谱管理与导入功能