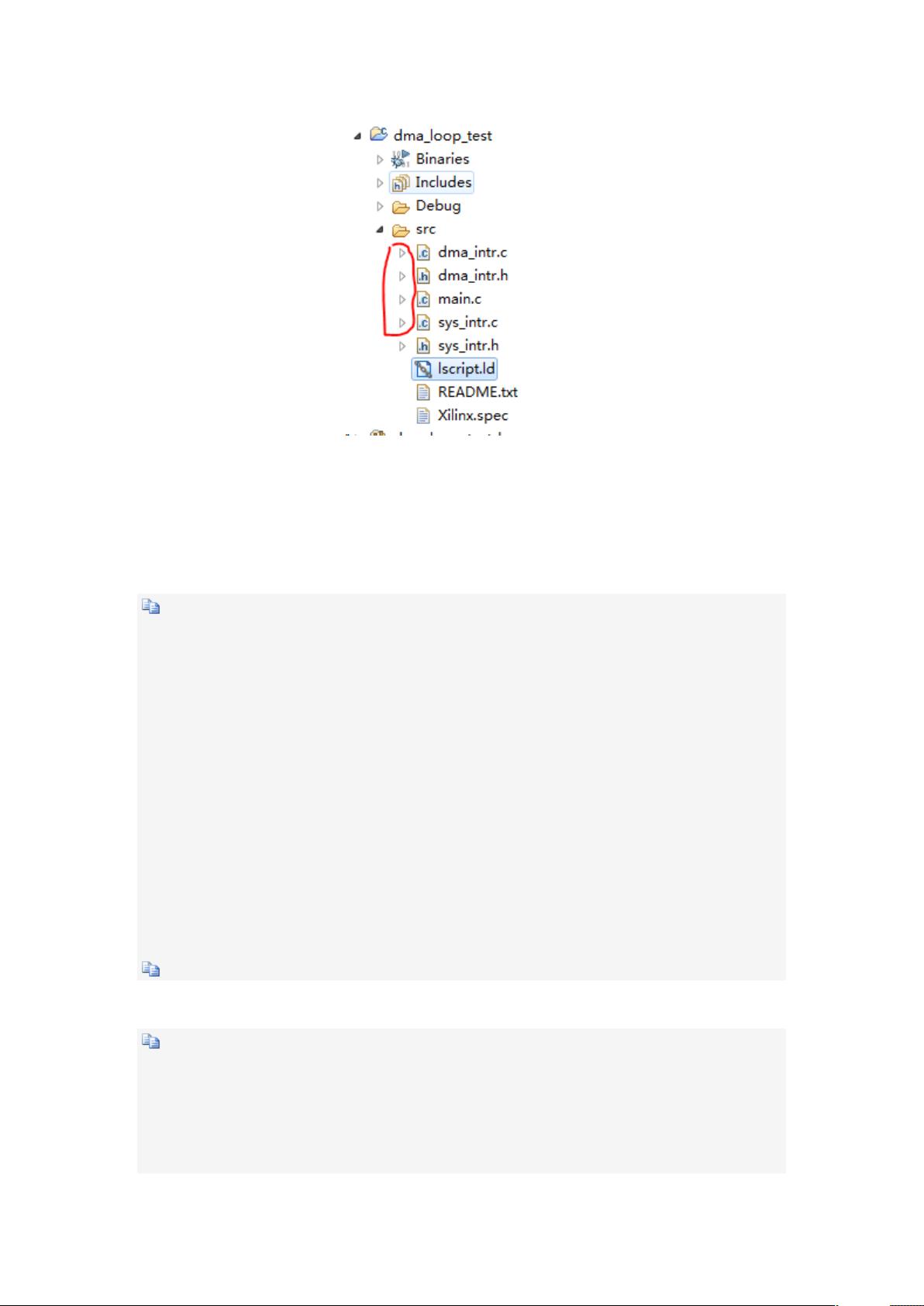

AXI DMA LOOP SDK编程详解

需积分: 0 37 浏览量

更新于2024-08-04

收藏 42KB DOCX 举报

"AXI DMA LOOP SDK代码说明1,涉及中断设备XScuGic和DMA设备XAxiDma的结构体解析"

在AXI DMA LOOP SDK中,主要涉及到两个关键的硬件抽象层(HAL)结构体,即中断控制器XScuGic和DMA引擎XAxiDma。这些结构体在软件设计中扮演着至关重要的角色,用于管理和控制硬件资源。

1. 中断设备:XScuGic

XScuGic是ARM的Scalable Interrupt Controller(GIC)的驱动实例数据。`static XScuGicIntc` 是一个静态全局变量,用于在整个程序范围内保存中断控制器的状态和配置。`XScuGic` 结构体包含以下字段:

- `XScuGic_Config* Config`:指向配置表条目的指针,包含了设备ID、CPU接口寄存器基地址和分发器寄存器基地址,以及中断处理程序的向量表。

- `u32 IsReady`:表示设备是否已经初始化并准备就绪。

- `u32 UnhandledInterrupts`:用于统计未处理的中断次数。

`XScuGic_Config` 结构体则定义了GIC的具体配置信息,包括设备ID、CPU接口和分发器的基地址,以及中断处理程序的向量表,这个向量表用于映射每个中断输入到相应的中断处理函数。

2. DMA设备:XAxiDma

`static XAxiDma AxiDma` 也是静态全局变量,用于表示使用的DMA引擎。`XAxiDma` 结构体定义如下:

- `UINTPTR RegBase`:指向DMA引擎寄存器的虚拟地址,用于访问和控制DMA引擎的各种操作。

这个结构体通常包含了DMA引擎的配置信息,如传输方向(单向或双向)、传输模式(简单模式或 Scatter-Gather 模式)等。在实际应用中,开发者会通过这些接口来设置和启动DMA传输,监控传输状态,并处理相关的中断事件。

在AXI DMA LOOP测试中,这两个结构体的实例被用于建立中断处理机制和管理DMA传输。中断设备XScuGic负责接收和分发来自硬件的中断请求,而DMA设备XAxiDma则负责在内存和外设之间高效地移动数据。通过这样的组合,SDK能够实现循环数据传输,例如在一个环形缓冲区中不断读写数据,这在实时系统和高性能计算中非常常见。在代码中,中断可能被用来触发新的DMA传输,或者在传输完成后通知处理器。

353 浏览量

366 浏览量

1381 浏览量

353 浏览量

2024-02-21 上传

2021-06-08 上传

1381 浏览量

2025-01-07 上传

2025-01-07 上传

叫我叔叔就行

- 粉丝: 33

- 资源: 323

最新资源

- 维修中心产品报价清单excel模版下载

- lsvine:`tree -L 2`具有较少的空白屏幕空间

- project_app:这是非常重要的项目

- Newton's method done right:牛顿法求解非线性方程组,包括非平方和不一致方程组-matlab开发

- 现代客厅模型效果图

- 美丽的心型:用Python表达爱意

- command-line-linter

- simpleMapExercise

- SpotifyStalker

- 日记账格式excel模版下载

- dfs:DFS 阵容优化器应用程序的 Github 存储库

- WebProjectWithDjango

- DEF-CON-Links:DEF CON 28安全模式的简易链接和指南

- r7rs-clos:适用于R7RS的微型CLOS包装器

- 小型电影院3D模型

- vscode_ros2