Xilinx UltraScale+ PCIe Integrated Block for PCI Express v1.3 设计...

下载需积分: 0 | PDF格式 | 16.16MB |

更新于2024-06-18

| 108 浏览量 | 举报

"pcie Virtex-7 FPGA Gen3 Integrated Block for PCI Express pg023"

本文档详述了Xilinx的Virtex-7 FPGA Gen3集成块在PCI Express(PCIe)应用中的具体实现和设计流程。该资源是针对UltraScale+系列器件的PCIe集成块v1.3的产品指南,适用于Vivado Design Suite。

**第1章:引言**

本章介绍了PCIe集成块的关键功能特性,包括其高速数据传输能力,以及对Vivado Design Suite的兼容性。此外,还提到了IP的相关信息,这可能包括知识产权(IP)的核心模块、许可证管理和订购详情。

**第2章:概述**

这一部分提供了功能特性的总结,强调了该IP核在不同应用场景下的适用性,例如高性能计算、数据中心和通信系统。同时,列出了不被支持的功能,以帮助设计者避免潜在问题。本章还涵盖了许可和订购信息,指导用户如何合法使用和购买相关产品。

**第3章:产品规格**

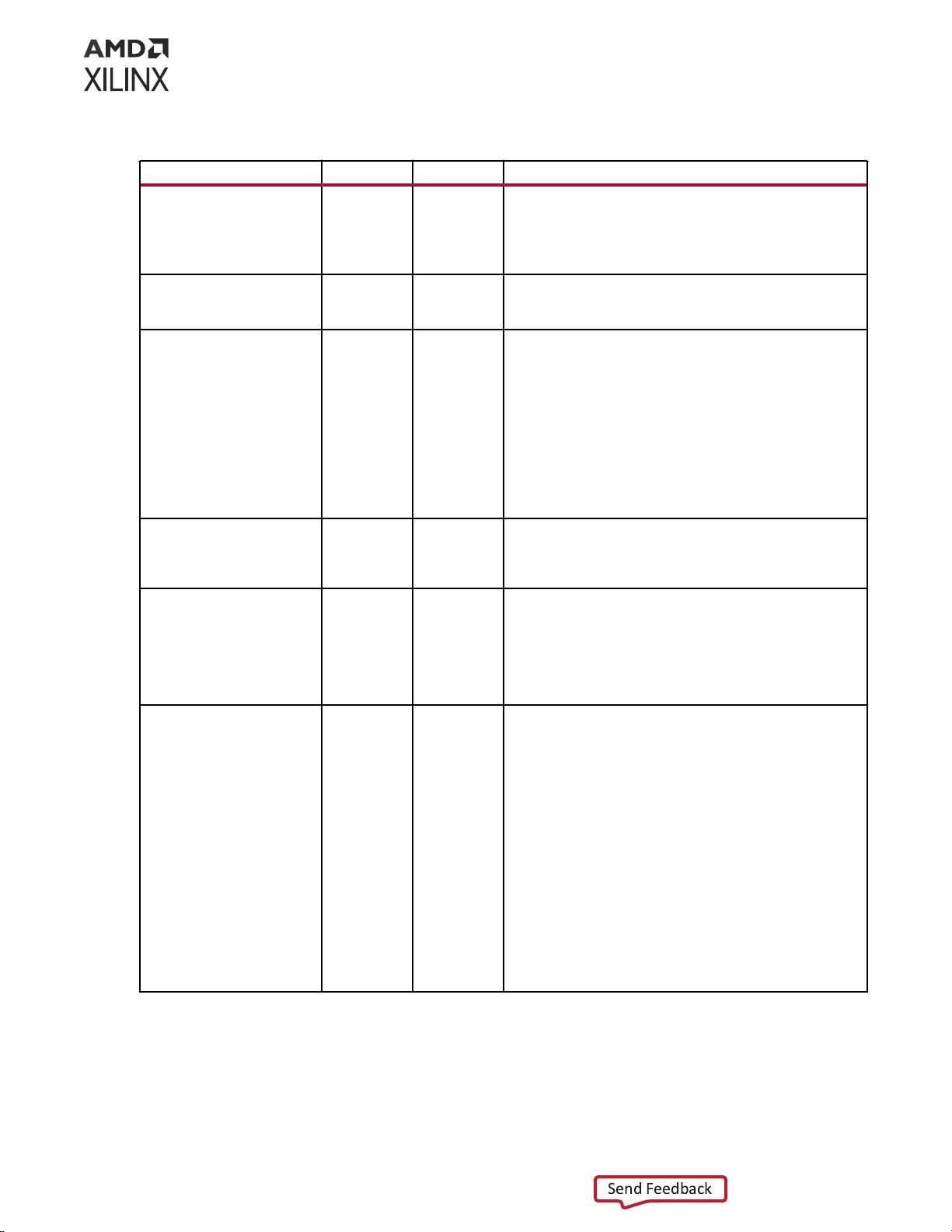

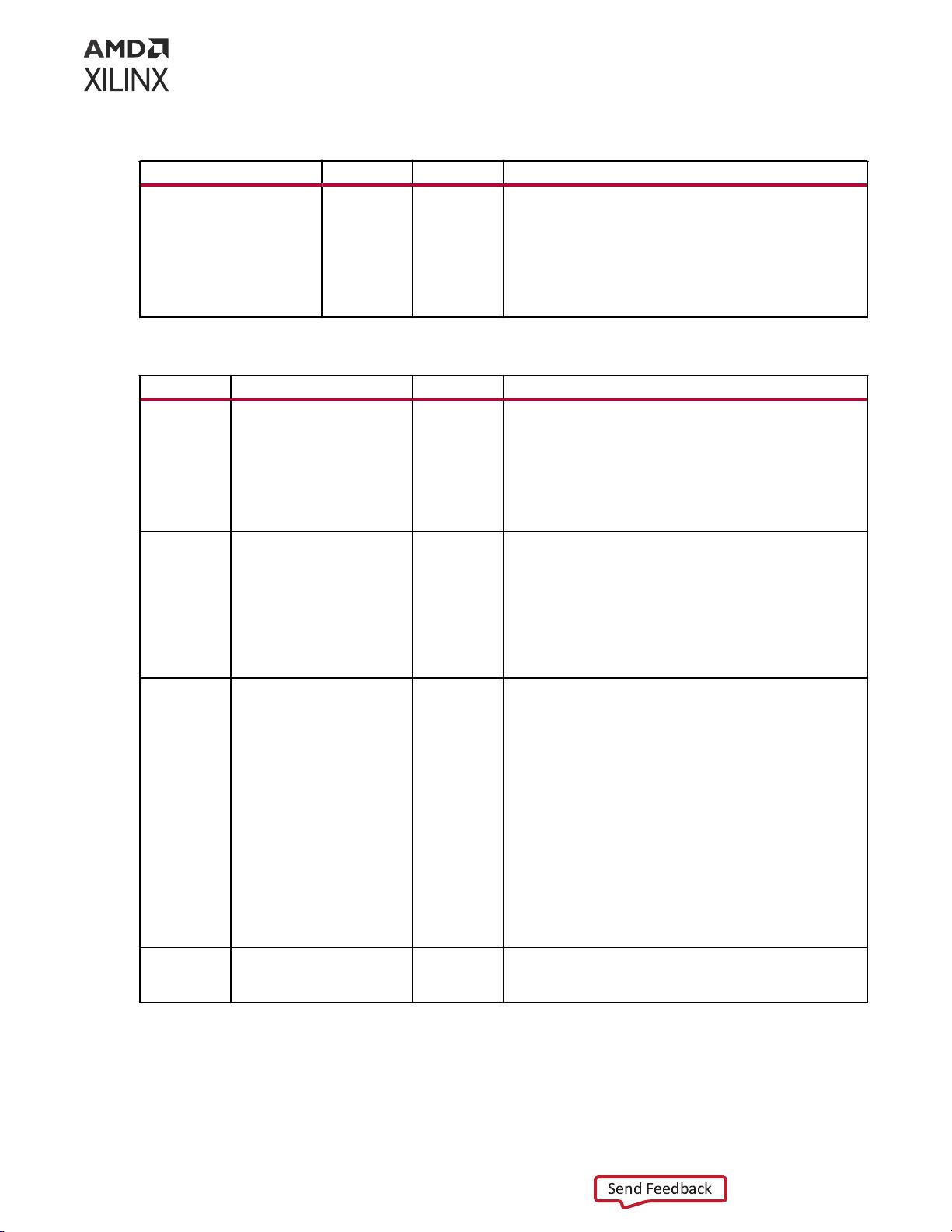

详细阐述了标准合规性,确保该PCIe集成块符合PCI-SIG的Gen3规范。讨论了资源使用情况,包括逻辑单元、I/O引脚和其他关键资源的占用。此外,明确了最小器件要求,以及可用于PCIe的不同集成块配置。GT(GigaTransceiver)位置的说明有助于布局布线,而端口描述则描述了与外部设备交互的接口细节。

**第4章:用核设计**

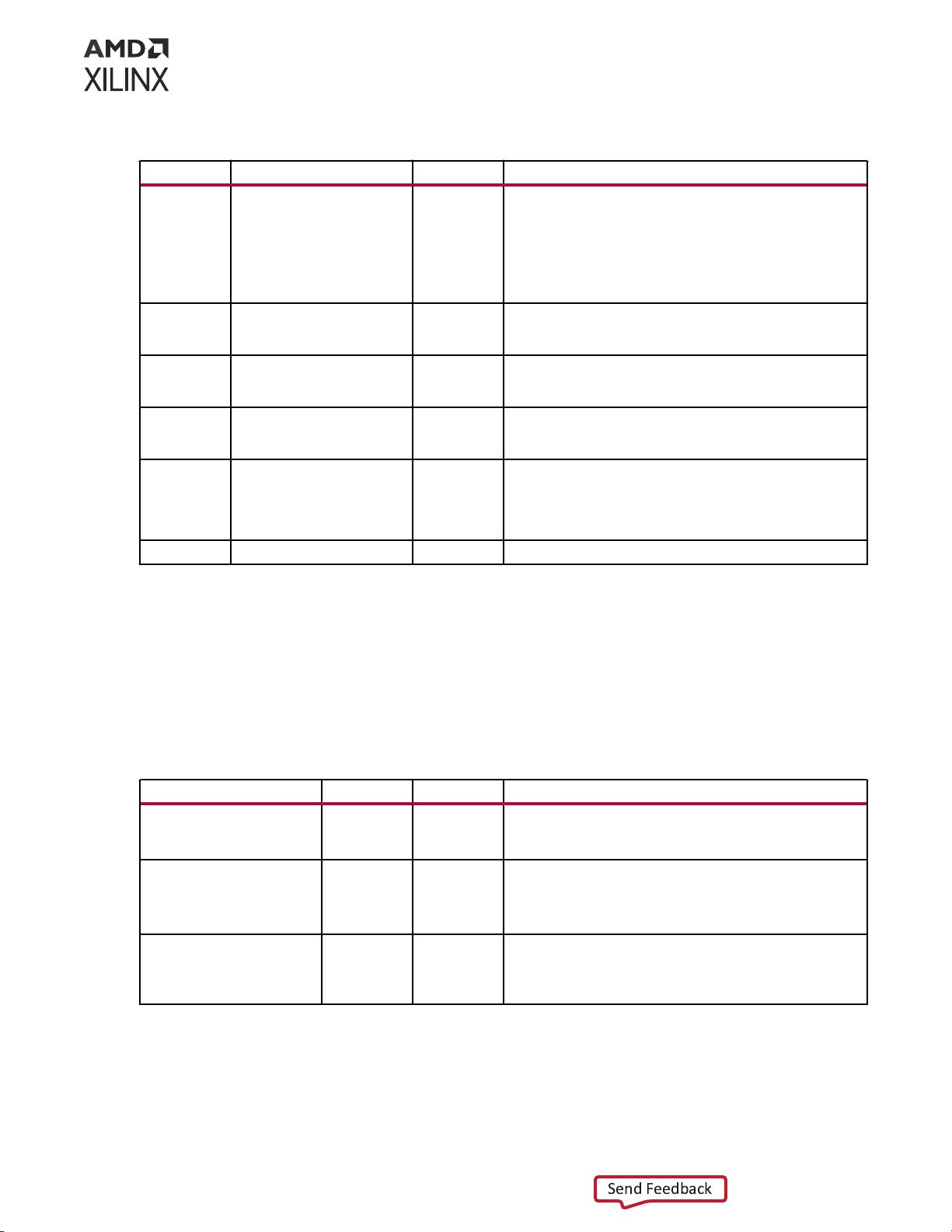

这一章深入介绍了设计过程中的各个要素,如串联配置、时钟管理、复位机制、AXI4-Stream接口的使用,以及功耗管理。它还涵盖了中断请求的生成、接收消息接口和配置管理接口的详细操作。特别是,如何在根端口上启用环回主控制器,以及链路训练过程,包括对2通道、4通道、8通道和16通道组件的支持。通道翻转功能允许用户在遇到物理连接问题时调整信号路径。

**第5章:设计流程步骤**

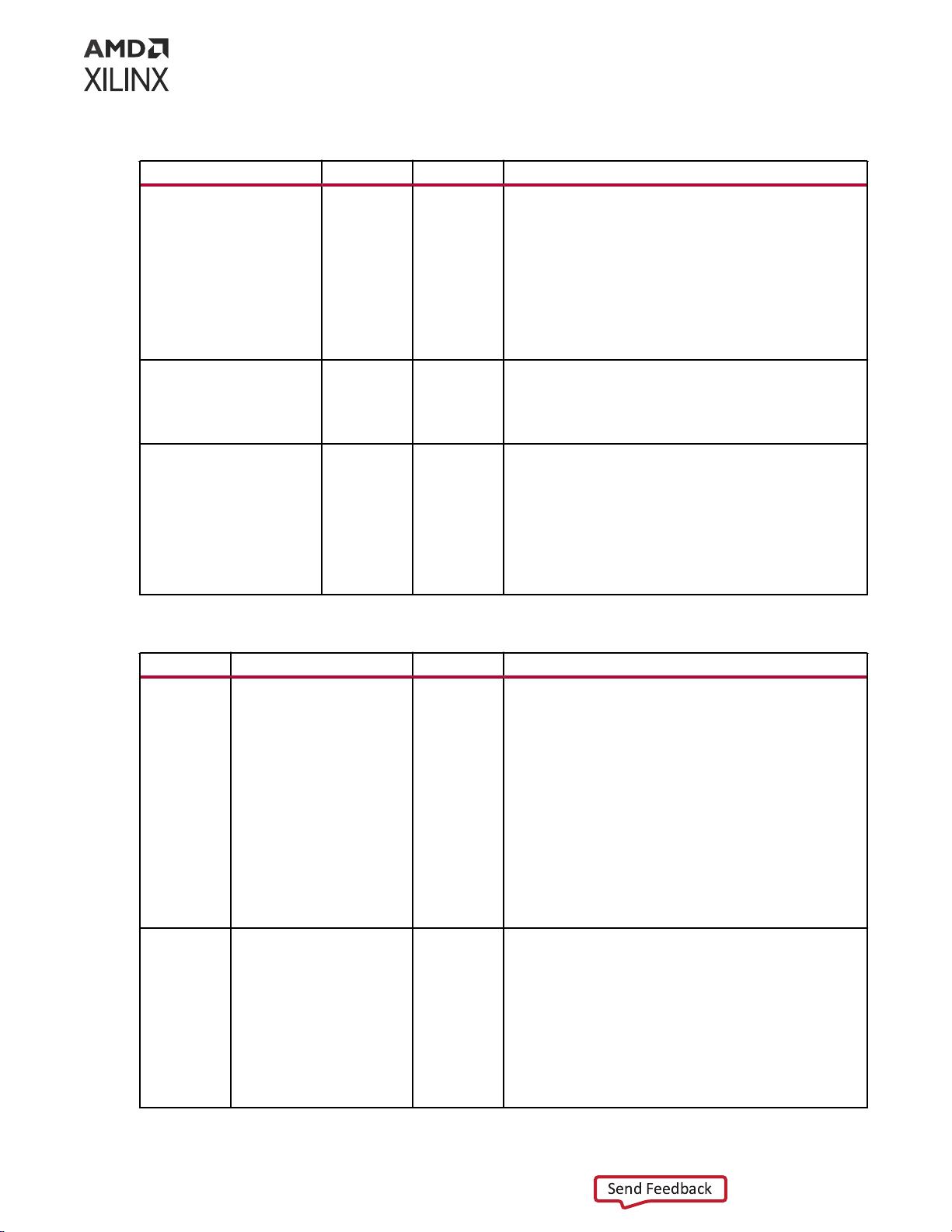

本章指导设计者如何自定义和生成PCIe集成块,包括设置约束、进行仿真、综合及实现等步骤。这些步骤是实现高效FPGA设计的关键环节。

**第6章:设计示例**

通过提供设计示例,这一章帮助用户理解如何实际操作上述设计流程。从生成核开始,直到打开设计示例、进行仿真、综合和实现,每个步骤都有详细的解释和指导。

**第7章:测试激励文件**

这部分提供了对应根端口和端点模型的测试激励文件,用于验证设计的正确性和性能。这些测试激励文件是确保设计功能完备的关键工具。

**附录A:升级**

附录中讲述了如何从UltraScale系列器件移植到UltraScale+,并给出了在Vivado Design Suite中进行这种迁移的步骤和注意事项。

Xilinx致力于创建一个包容的工作环境,并逐步从产品和文档中移除非包容性语言。尽管旧产品可能仍包含此类语言,但公司正在努力更新其内容,以符合行业发展的标准。

总结,这个资源是针对Virtex-7 FPGA Gen3 PCIe集成块的全面设计指南,包含了从设计概念到实现的全部流程,对于使用Xilinx UltraScale+ FPGA进行PCIe开发的工程师来说,是一份极其宝贵的参考资料。

相关推荐

麦克四伟

- 粉丝: 117

- 资源: 3

最新资源

- 基于卷积神经网络的4种猫咪预测模型

- 中交进出库明细表excel模版下载

- 使用Arduino监控ECG和呼吸-项目开发

- ya-school-shri-2018-1:“发现错误”-接口开发学院的入门作业

- DailyGrain

- 镍矿开采:一种用于收集镍矿开采场所相关数据的模型。 工作正在进行中

- 女士闺房3D模型设计

- 工程管理人员个人总结

- HTML-CSS-[removed]实行多元化的保护措施

- 128x64 LCD上的模拟,数字时钟和温度计-项目开发

- Smolyak各向异性网格:解决高维问题-matlab开发

- terraform-workshop

- 日记账管理系统excel模版下载

- 酒店走廊3D模型

- Arduino 101-英特尔居里图案匹配连衣裙-项目开发

- Ecom