DC中文教程:入门指南

需积分: 10 124 浏览量

更新于2024-07-24

收藏 1.15MB PDF 举报

"DC中文教程是一份针对初级学者的Synopsys Design Compiler(DC)的入门教程,旨在帮助初学者了解和掌握如何设置系统环境、执行默认综合、设定设计规范、设定操作环境以及设计约束。教程中详细讲解了时序电路和组合电路的约束设置,并介绍了综合后电路的仿真方法。此外,还提到了Synopsys Design Analyzer的使用和在线文档的获取。用户需要根据提供的示例设置环境变量,并学习如何自定义cell library和使用转换工具将Verilog模型转化为.db文件。.synopsys_dc.setup文件是关键,用于定义启动Design Compiler的配置和使用的cell Library。"

在DC中文教程中,以下几个关键知识点是重点:

1. **系统环境设置**:为了使用Synopsys工具,用户需要按照教程指示设置环境变量,如通过添加`/usr/synopsys/cicSynop/synopsys.cshrc`的内容到用户的`.cshrc`文件中,然后执行`source .cshrc`来更新环境。

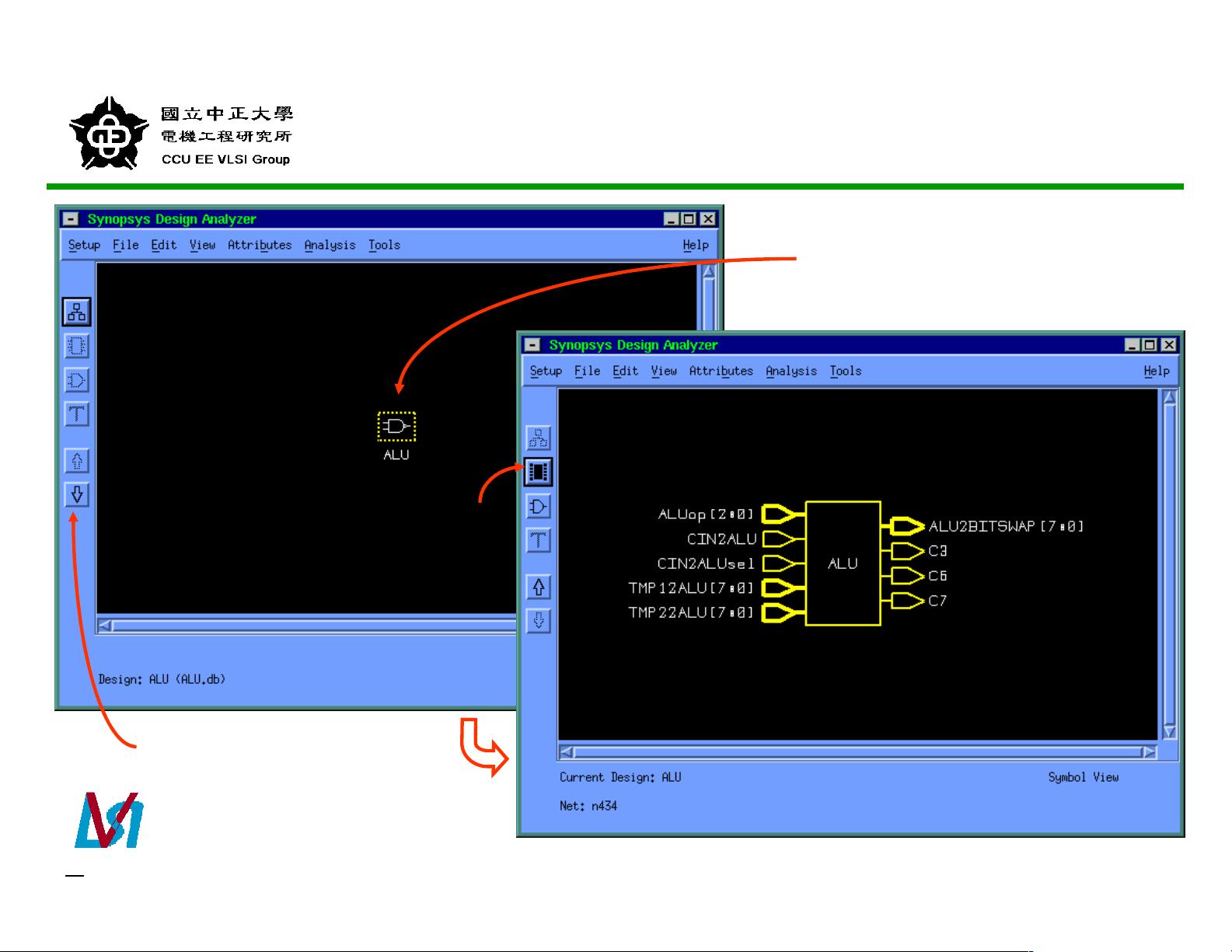

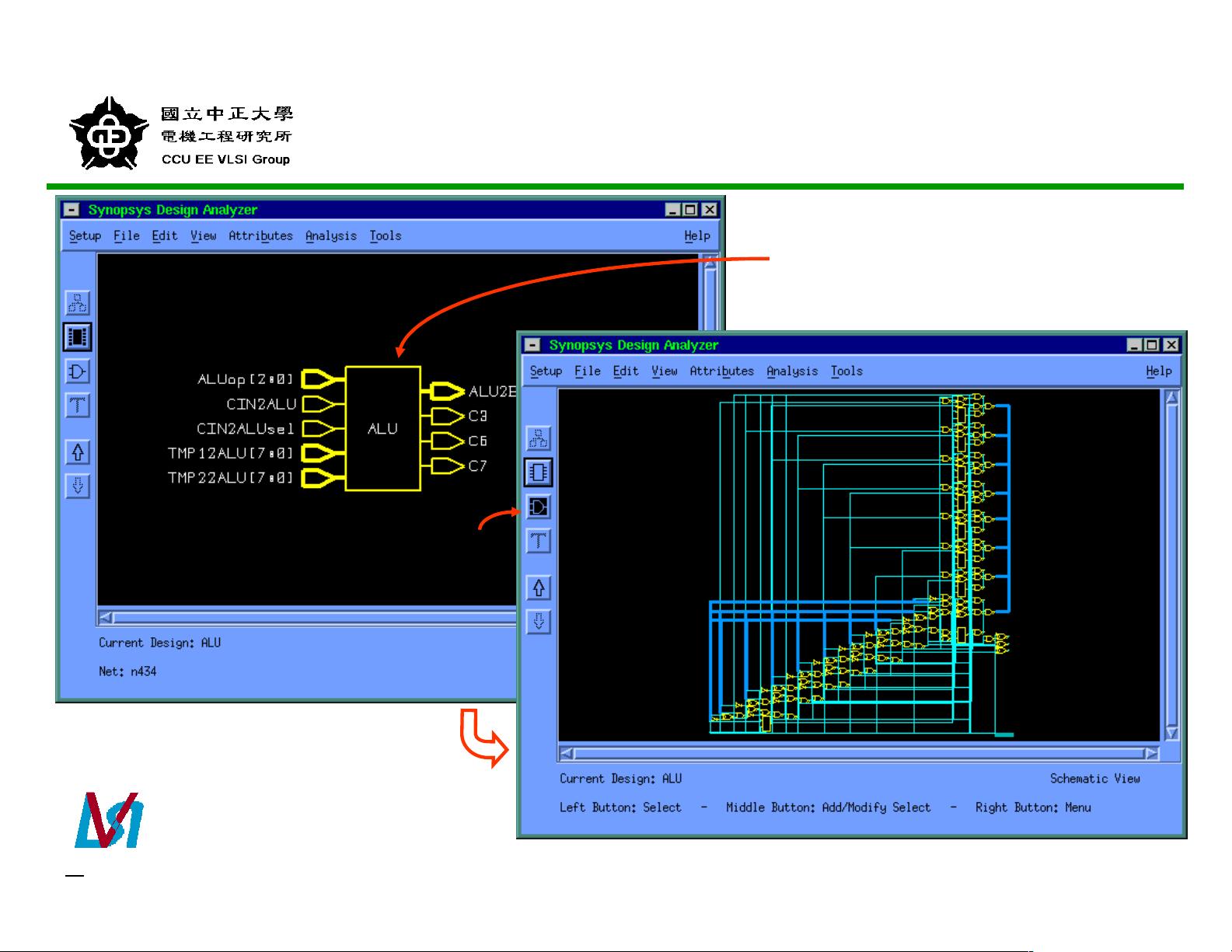

2. **默认综合**:DC提供了默认的综合流程,适合初学者快速上手。用户需要了解如何启动Synopsys Design Analyzer进行设计综合。

3. **设计规范设定**(Design SPEC):在进行综合前,需明确设计规范,包括逻辑功能、功耗、面积等目标。

4. **操作环境设定**:设置设计约束是确保综合结果满足性能要求的关键步骤,这包括时序约束、电源电压和温度等。

5. **时序电路和组合电路的约束**:对于组合电路,主要设置的是时序约束;对于顺序电路,需要指定时钟、输入延迟和输出延迟。

6. **模拟综合后的电路**:综合完成后,通过仿真工具(如Iview)验证电路的正确性。

7. **自定义cell library**:用户可以创建自己的Verilog模型库,并使用Synopsys的转换工具将其转换为二进制的.db文件,以便于设计使用。

8. **.synopsys_dc.setup文件**:这个文件定义了Design Compiler的启动参数和使用的cell库路径,用户可以根据需求对其进行定制。

9. **在线文档**:教程中提到可以获取Synopsys的在线文档,这对于深入学习和解决问题非常有帮助。

通过学习这个DC中文教程,初学者能够逐步掌握Synopsys Design Compiler的基本操作和设计流程,为进一步的数字集成电路设计打下坚实的基础。

2007-08-28 上传

2012-11-04 上传

108 浏览量

2011-09-05 上传

lzhzhup

- 粉丝: 1

- 资源: 3