北大资源:Verilog HDL从入门到高级:全面设计与仿真教程

需积分: 10 48 浏览量

更新于2024-07-20

收藏 2.53MB PDF 举报

本资源是北京大学信息学院的精品课程讲义,深入讲解了Verilog HDL(Hardware Description Language)的基础知识与进阶内容,涵盖了从入门到高级设计实践的过程。课程由数字集成电路设计专家于敦山教授主讲,旨在帮助学生掌握Verilog语言的核心概念、结构级和行为级描述、仿真技术以及实际设计流程。

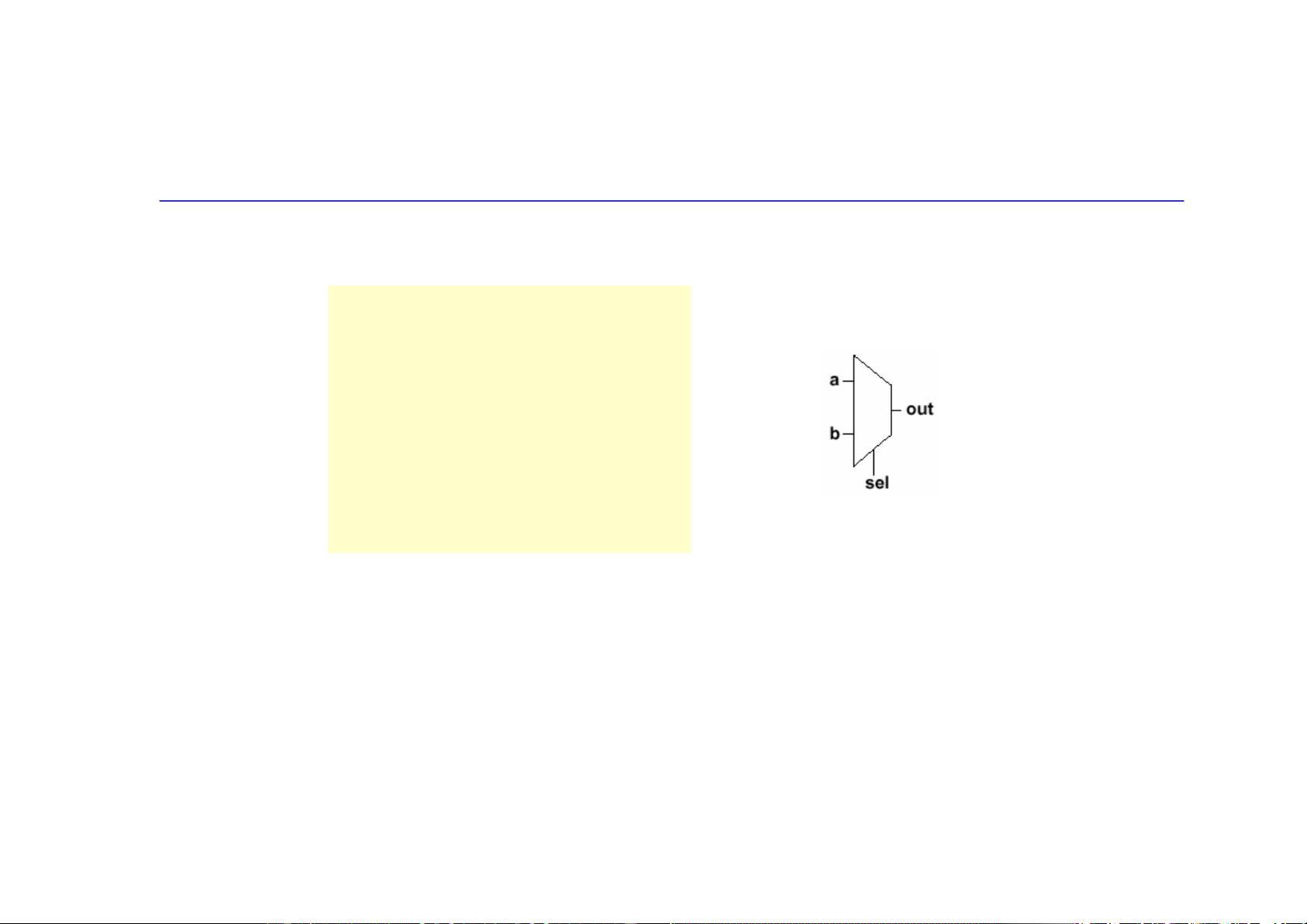

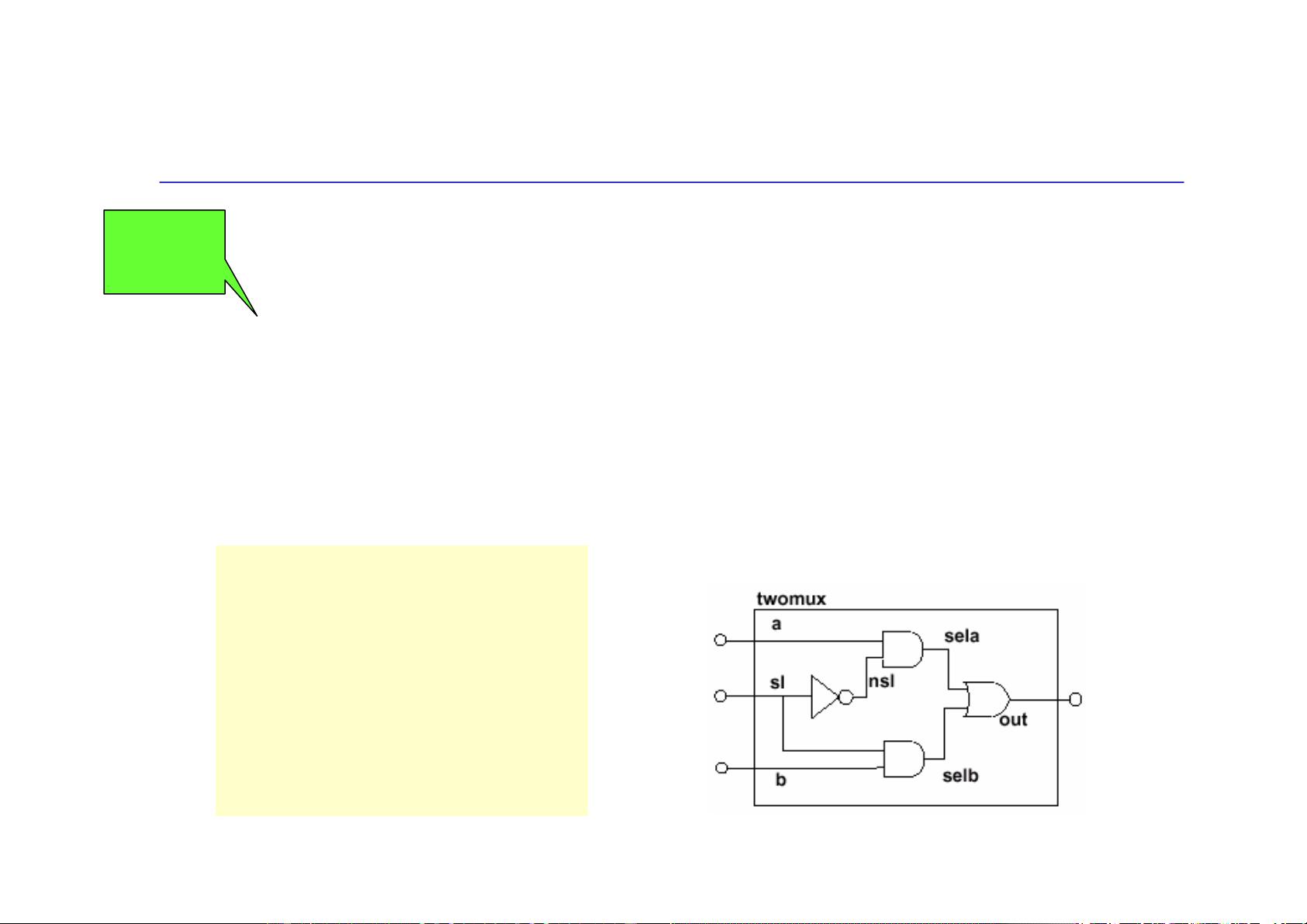

第一部分,"数字集成电路设计入门",介绍了Verilog语言的基础,包括其应用领域,构成元素如任务(task)、函数(function)和用户定义的基本单元(primitive),以及可综合的描述风格。学习者将学会如何编写结构化和行为化的代码,并通过Verilog testbench进行模型的激励和验证。

第二部分深入讲解Cadence Verilog仿真器的使用,涉及设计编译、仿真过程、源库管理、调试方法,包括图形用户界面GUI调试和延时处理。学生将掌握如何利用NCVerilog进行周期仿真,理解延时计算和反标注的重要性。

第三部分聚焦于逻辑综合,包括静态时序分析(STA)、Design Analyzer环境和可综合的HDL编码规范。通过实例,学生将学习如何编写能够被综合工具处理的Verilog代码,如Designware库的使用和综合划分策略。

课程还设置了两个实验环节,分别涉及设计约束的设置、设计优化(如FSM的优化)、设计报告的分析和自动布局布线工具Silicon Ensemble的简介。实验部分不仅锻炼了学生的动手能力,也加深了对理论知识的理解。

推荐的学习资料包括Cadence官方教材、《硬件描述语言Verilog》(清华大学出版社),以及专门针对Verilog模拟和综合的其他书籍,如Verilog-XL Simulation with Synthesis和Envisia Ambit Synthesis。

整个课程共54学时,分为理论教学和实践操作两大部分,强调理论与实践相结合,确保学生能全面掌握Verilog HDL的设计、仿真和集成开发流程。这对于希望在数字电路设计领域深造的学生来说是一份宝贵的教育资源。

2010-09-26 上传

2023-06-14 上传

2023-05-25 上传

2023-05-25 上传

2023-06-09 上传

2023-05-30 上传

2023-05-24 上传

毅雨云成

- 粉丝: 1

- 资源: 2

最新资源

- Google Test 1.8.x版本压缩包快速下载指南

- Java实现二叉搜索树的插入与查找功能

- Python库丰富性与数据可视化工具Matplotlib

- MATLAB通信仿真设计源代码与应用解析

- 响应式环保设备网站模板源码下载

- 微信小程序答疑平台完整设计源码案例

- 全元素DFT计算所需赝势UPF文件集合

- Object-C实现的Flutter组件开发详解

- 响应式环境设备网站模板下载 - 恒温恒湿机营销平台

- MATLAB绘图示例与知识点深入探讨

- DzzOffice平台新插件:excalidraw白板功能介绍与使用指南

- Java基础实训教程:电子商城项目开发与实践

- 物业集团管理系统数据库设计项目完整复刻包

- 三五族半导体能带参数计算器:精准模拟与应用

- 毕业论文:基于SSM框架的毕业生跟踪调查反馈系统设计与实现

- 国产化数据库适配:人大金仓与达梦实践教程