DDRPHY技术解析:LPDDR4与LPDDR5的电源与信号完整性

"这篇文章主要探讨了LPDDR4和LPDDR5在供电和电源分析方面的关键技术和挑战。内容涉及DDRPHY的复杂性、电源完整性、信号完整性和训练设计的重要性。"

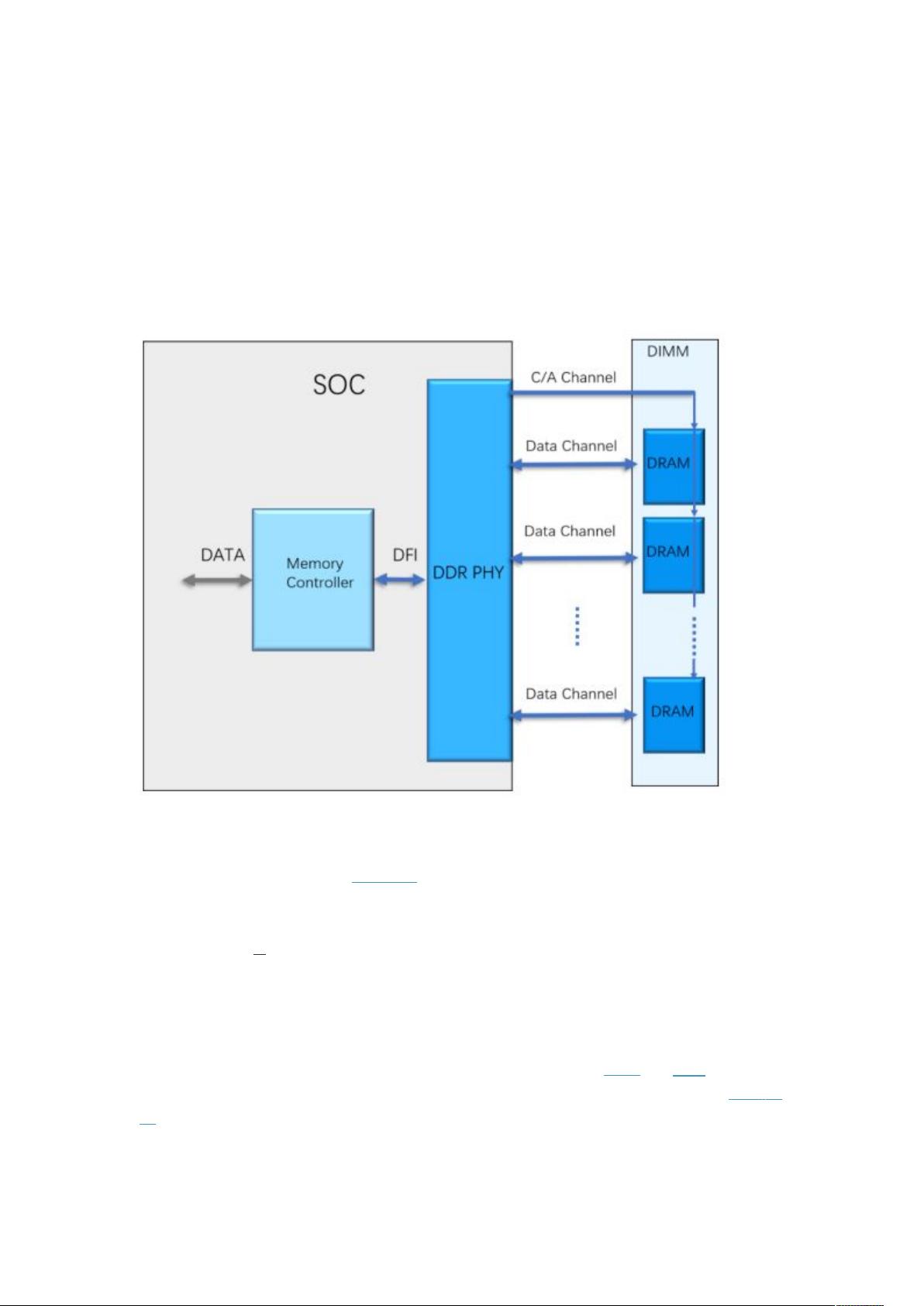

在移动设备和高性能计算中,LPDDR4和LPDDR5内存标准被广泛采用,以提供高效能与低功耗的数据传输。这两种内存类型都依赖于精密的DDRPHY(DDR PHYsical Layer),它是连接控制器和DRAM的关键组件。DDRPHY的设计不仅是一项芯片技术,更是一种系统工程,因为它需要处理高速并行传输和单端突发模式数据流带来的电源和信号完整性问题。

DDRPHY的设计难点在于它需要确保电源完整性(PI)和信号完整性(SI)。电源完整性涉及到电源网络的设计,以防止电压波动影响数据传输的准确性;而信号完整性则关注信号在传输过程中的失真,如时钟抖动和信号衰减。由于DDR数据以多位并行、单端突发模式传输,这就对封装和PCB布线提出极高要求,需要严格控制线长匹配和降低串扰,以保证数据的准确传输。

此外,DDR系统对训练有极高的需求,包括初始化的CALibration(CATraining)、WriteLeveling、ReadLeveling以及WriteEyeTraining等,确保内存能正确工作。对于LPDDR4及以上协议,还有二维VREF训练来校准参考电压。传统的硬件训练方法可能无法应对复杂的情况,例如单一的训练范式不足以反映实际通道中的码间串扰(ISI),这需要更智能的软件辅助训练策略。

芯耀辉等公司通过在早期阶段进行系统级的SI和PI分析,帮助客户优化DDRPHY的性能,确保在大规模生产时能满足严格的性能标准。这一过程通常涉及预先规划芯片的PAD布局和封装设计,以最大程度地减少潜在的问题。

LPDDR4和LPDDR5的供电和电源分析是芯片设计中的核心环节,需要综合考虑物理层设计、训练算法、封装与PCB布线优化等多个方面,确保内存系统的稳定和高效运行。随着内存速度的不断提升,这些挑战也日益增大,但通过先进的设计方法和工具,开发者能够克服这些困难,实现高性能且低功耗的内存解决方案。

985 浏览量

423 浏览量

139 浏览量

2024-07-04 上传

388 浏览量

1775 浏览量

云淡风cl

- 粉丝: 7

- 资源: 2