VerilogHDL实现的智能课堂响铃系统设计

版权申诉

91 浏览量

更新于2024-07-02

收藏 493KB DOC 举报

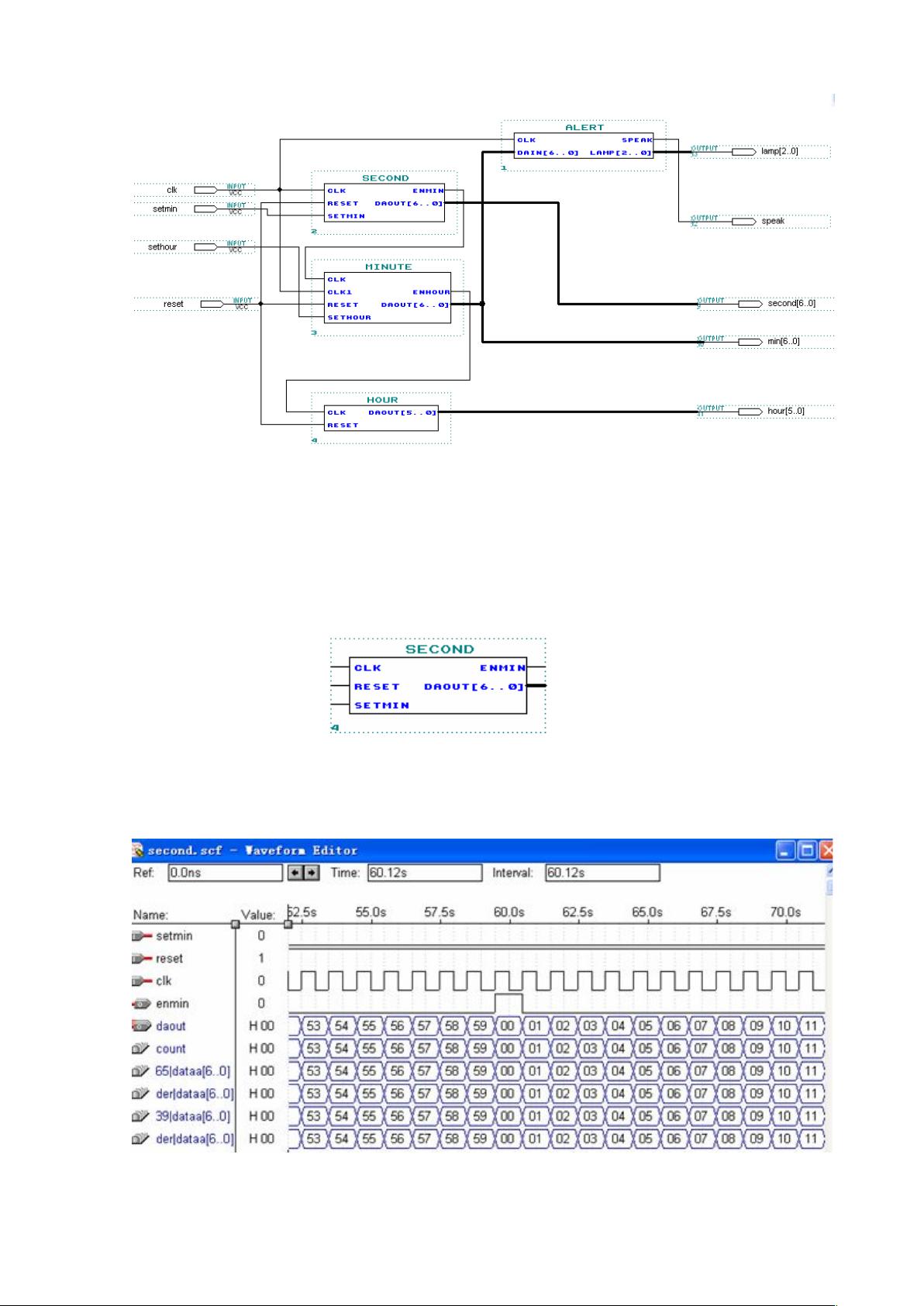

"基于Verilog HDL语言的课堂智能响铃系统设计"

本文主要讨论了使用Verilog HDL语言设计的课堂智能响铃系统,该系统具有高精度、稳定性和实用性,可应用于学校等场合,提供准确的定时响铃功能。系统采用24小时循环计时,具备LED灯的动态显示,支持时间设置、清零和整点报时功能。

1.1 课程设计目的

此课程设计的主要目标是提升通信专业学生的EDA(电子设计自动化)技能和通信电路设计能力。通过独立完成设计任务,学生能够强化对计算机硬件基础知识的理解,提高动手实践能力,并为未来更复杂项目奠定基础。

1.2 课程设计内容

设计的核心是智能打铃系统,它能准确计时并显示时、分、秒,秒和分以60进制循环,时钟以24进制循环。用户可以利用实验板上的按键调整时间,复位键用于清零,而蜂鸣器则在整点报时。LED灯在显示时间时会有特定的闪烁模式,增强视觉效果。

2.1 Verilog HDL语言概述

Verilog HDL是一种广泛使用的硬件描述语言,它允许设计者以文本形式描述数字系统的结构和行为。起源于1983年的Gateway Design Automation公司,Verilog HDL深受C语言影响,便于理解和编写,是电子设计领域的重要工具。

在设计课堂智能响铃系统时,Verilog HDL被用来描述系统中的逻辑门、触发器、计数器等基本元素,以及它们之间的交互。例如,用Verilog可以定义计数器模块,描述其计数规则(如60进制或24进制)、复位和时钟输入的逻辑,以及如何将计数值显示在LED数码管上。此外,还可以定义控制模块来处理按键输入,实现时间设置和清零功能。

在实际实现过程中,设计者会首先使用Verilog编写模块级的代码,然后通过仿真验证代码的正确性。一旦设计满足需求,代码会被综合成适配特定 FPGA(Field-Programmable Gate Array)或ASIC(Application-Specific Integrated Circuit)的网表,最后通过编程工具下载到硬件上,实现实际的课堂智能响铃系统。

这个项目不仅涵盖了Verilog HDL的基本概念和应用,还强调了数字系统设计的实践环节,包括时序逻辑、同步与异步电路、复位和时钟管理,以及人机交互设计。通过这样的课程设计,学生能够在理论与实践中得到全面的提升。

228 浏览量

132 浏览量

点击了解资源详情

137 浏览量

194 浏览量

2023-06-22 上传

智慧安全方案

- 粉丝: 3843

- 资源: 59万+