"基于VerilogHDL语言的智能课堂响铃系统设计"

版权申诉

97 浏览量

更新于2024-02-22

收藏 493KB DOC 举报

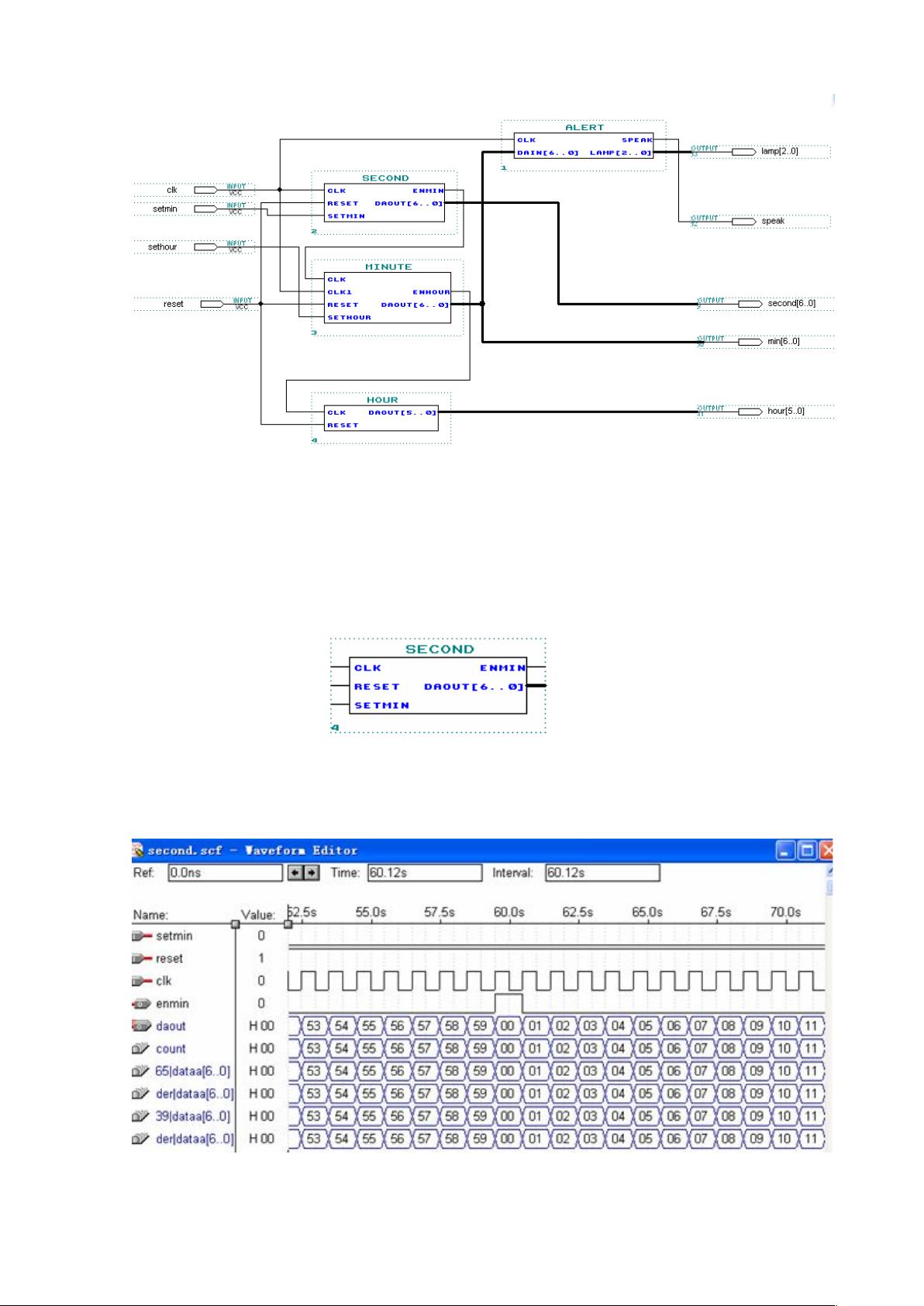

20世纪末,电子技术的飞速发展带动了现代电子产品在社会各个领域的广泛应用,推动了社会生产力的提升和社会信息化程度的提高。在这一背景下,课堂智能响铃系统作为一种新型电子产品,具有高精度、稳定性好、实用方便的特点,无需频繁调试即可有效运行。该系统具有时、分、秒计数显示功能,以24小时循环计时,LED灯花样显示时钟计数,可调节小时、分钟、清零,还具有整点报时功能。

作为通信专业的学生,通过这次基于VerilogHDL语言的课程设计,我们得以提高对EDA领域和通信电路设计领域的认识,培养通信电路和EDA设计能力。每个人都有独立的课题,这有利于锻炼我们独立分析和解决问题的能力。设计过程的复杂性和老师的严格要求有助于培养我们严谨的工作态度。本次课程设计是计算机组成原理的一部分,旨在通过设计和实现所需功能芯片来巩固以往学习的计算机硬件基础知识,同时提升动手实践能力,积累未来进行更大规模复杂开发的经验。

课程设计的内容主要是实现智能响铃系统,包括时钟计数功能:准确计时显示时、分、秒,并且显示所计的时间。通过VerilogHDL语言实现课堂智能响铃系统,我们不仅可以理解VerilogHDL语言的应用,还可以深入了解电子系统的工作原理和设计思路。设计过程中,我们需要对电路进行分析和仿真,不断调试和优化,以确保系统可靠稳定地运行。

在完成课程设计的过程中,我们通过VerilogHDL语言的学习和应用,提高了对数字电路设计和EDA工具的熟练程度,增强了解决实际问题的能力。同时,通过与同学的合作和交流,我们拓展了视野,学会了倾听他人的意见和建议,形成了良好的团队合作精神。在老师的指导下,我们逐步解决问题,不断完善设计,最终实现了功能完善的课堂智能响铃系统。

综上所述,基于VerilogHDL语言的课堂晨能响铃系统设计是一次宝贵的学习经历。通过这次课程设计,我们不仅提升了技术水平,还培养了解决问题的能力和团队合作意识。这将为我们未来的学习和工作打下坚实的基础,让我们更加自信地面对未来挑战。希望在今后的学习和工作中,我们能够不断进步,不断完善自我,为社会做出更大的贡献。

232 浏览量

点击了解资源详情

133 浏览量

133 浏览量

232 浏览量

137 浏览量

195 浏览量

智慧安全方案

- 粉丝: 3844

- 资源: 59万+