Verilog HDL驱动的课堂智能响铃系统设计与实现

需积分: 10 69 浏览量

更新于2024-07-26

4

收藏 471KB DOC 举报

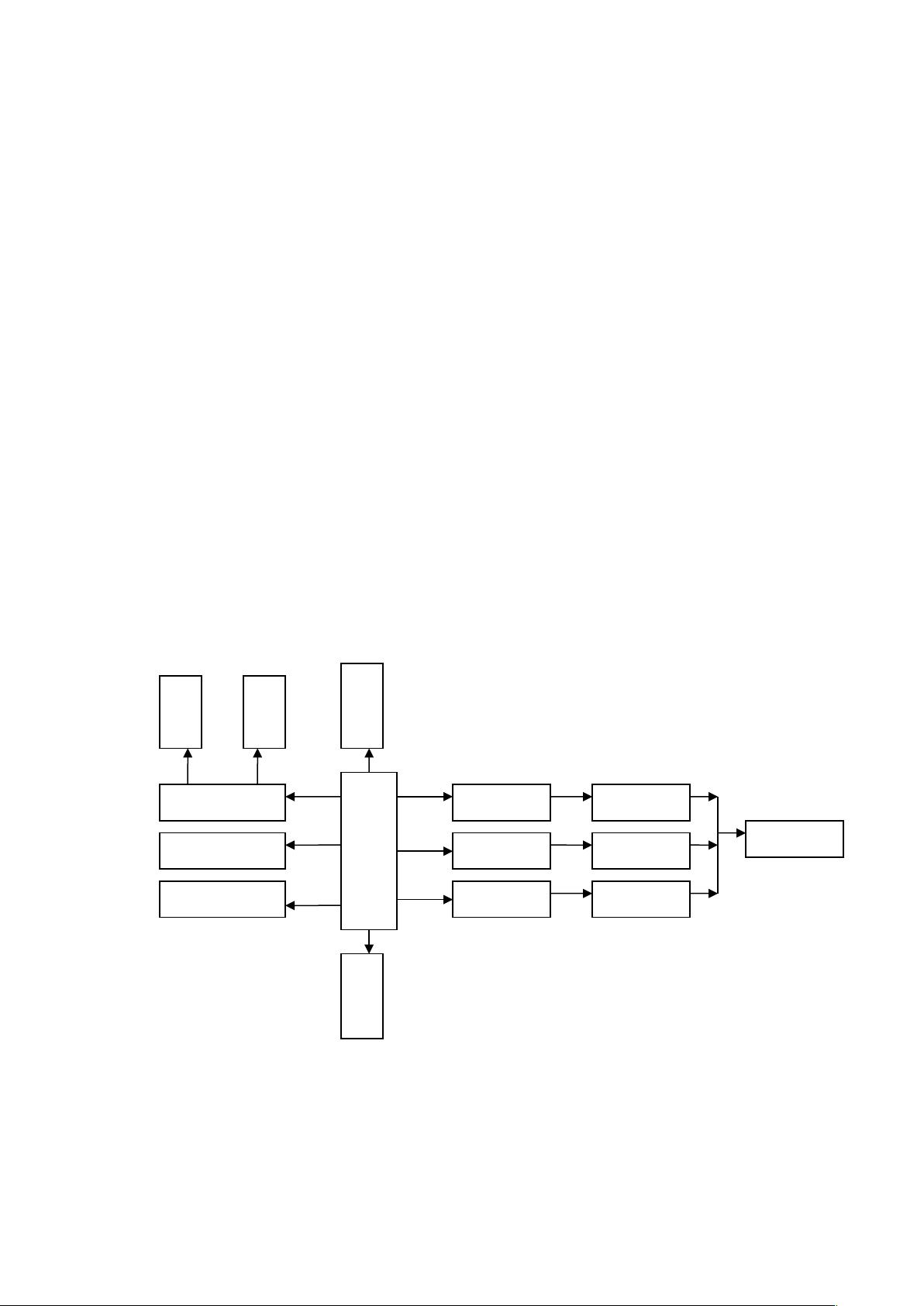

基于Verilog HDL语言的课堂智能响铃系统设计是一个创新的工程项目,它将现代电子技术与教学实践相结合,旨在提高课堂管理效率。Verilog HDL是一种专门用于描述数字系统硬件结构和行为的高级硬件描述语言,它源自C语言,由Gateway Design Automation公司在1983年推出。这个系统的核心优势在于其高精度的计时功能,包括24小时循环计时和精确到分钟的调节,同时具备清零和整点报时功能,使得时间设置变得灵活且易于操作。

设计过程中,学生利用MAX+plus II开发平台,采用Verilog HDL进行编程和仿真。MAX+plus II是一个广泛应用于电子设计自动化(EDA)的工具,它提供了设计、仿真和综合电路的功能。通过编写并调试程序,学生能够验证设计的正确性和有效性,确保每个组件如时钟计数器、数码管显示以及清零和报时逻辑都能按照预期工作。

课堂智能响铃系统的实现涉及到数字逻辑设计的基本概念,如60进制和24进制计数,以及脉冲信号的处理。此外,清零功能的实现依赖于复位键的控制,通过低电平触发清零,高电平保持正常计数,这展示了硬件设计中的条件控制逻辑。报时功能则通过在整点时触发蜂鸣器报警,通过LED灯的花样显示,增强了系统的交互性和趣味性。

通过这个课程设计,通信专业的学生不仅能够加深对EDA技术和通信电路设计的理解,还能提升独立思考和解决问题的能力,培养严谨的工作态度,同时锻炼动手实践操作和系统集成的技能。这对于未来在更复杂的电子产品研发中积累宝贵的经验至关重要。

基于Verilog HDL的课堂智能响铃系统设计不仅是技术实践,更是理论与实践相结合的教学案例,它展示了现代电子技术如何简化课堂管理,提高教学效率,并为学生提供了宝贵的学习和实践经验。

2022-03-14 上传

134 浏览量

点击了解资源详情

点击了解资源详情

点击了解资源详情

2023-06-20 上传

2025-01-06 上传

2025-01-06 上传

qinxuefen52

- 粉丝: 0

- 资源: 6

最新资源

- 图书管理备案系统.rar

- the_computer_vision_app:一款可在网络上执行常见的计算机视觉任务的应用程序

- java笔试题算法-C5:用于C#/.NET的C5泛型集合库

- comment2votes:seq2seq架构,用于预测reddit评论的投票

- andyseoDB

- 家居城促销顾客须知(转盘上摇奖的注意事项)

- 永宏PLC编成软件 适合FBE FBS B1Z等型号.rar

- file-system-access:公开用户设备上的文件系统,以便Web应用程序可以与用户的本机应用程序进行互操作

- jstl-tld.zip

- Ikasumi-crx插件

- 超可爱卡通动物图标下载

- 任务一-使用监督的机器学习预测:根据编号预测学生的百分比。 学习时间

- CSE212_DataStructures_Guide

- 初级java笔试题-awesome-php-resources:精选的很棒的php列表

- ךופה לע ךופה - הפוך על הפוך-crx插件

- 作业六