RISC处理器设计:32位单周期MIPS实现

"本资料详细介绍了32位单周期RISC处理器的设计,特别是基于MIPS指令集的实现。设计目标是构建一个支持15条指令的CPU,包括算术运算、逻辑运算、数据传递、条件分支和无条件跳转等基本功能。"

在设计32位单周期RISC处理器时,首先选择RISC体系结构是因为其适合流水线设计,简化了处理器架构,提高了执行效率。RISC(精简指令集计算机)的特点是指令数量少、指令格式固定且执行时间短,这有利于实现高速运行。

MIPS(Microprocessor without Interlocked Pipeline Stages)是一种广泛使用的RISC指令集,本设计选择了这个指令集,并遵循了五段流水线方式来实现。五段流水线通常包括取指、译码、执行、访存和写回五个阶段,每个阶段在一个时钟周期内完成,从而提高处理器的吞吐量。

目标CPU的指令集包含了15条指令,分为以下几类:

1. 算术运算:包括加法(add)和减法(sub),以及带有立即数的加法(addi)和减法(subi)。这些指令用于执行基本的数值计算。

2. 逻辑运算:包括与(and)、或(or)和非(nor)操作,以及相应的立即数操作(andi、ori和nori)。这些指令用于处理二进制逻辑操作。

3. 数据传递:通过 lw (load word) 和 sw (store word) 指令进行内存和寄存器之间的数据交换。

4. 条件分支:beq (branch if equal) 指令在两个寄存器内容相等时进行跳转;slt (set less than) 比较两个寄存器内容并设置条件标志;slt_i 是带有立即数的版本。

5. 无条件跳转:j (jump) 指令实现程序的无条件转移。

6. 空操作:nop (no operation) 指令不执行任何操作,常用于填充指令空间或作为占位符。

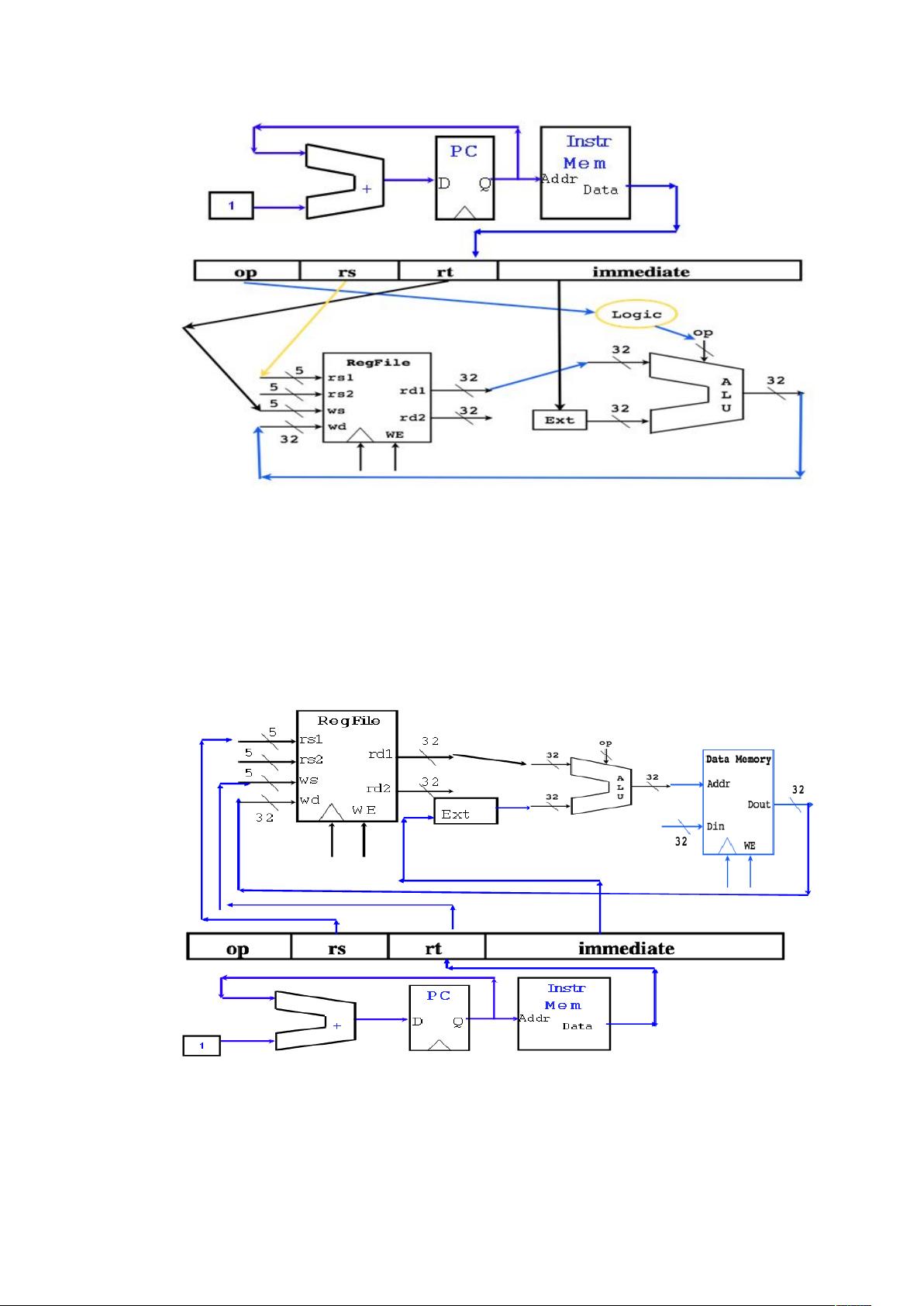

针对不同指令格式,数据通路的设计也有所不同:

- R格式指令:数据通路从指令寄存器InstrMEM获取指令,PC自动加1。rs1和rs2寄存器的内容被读出,根据指令中的操作码Opcoder在ALU中进行计算,结果写回到由rd指定的寄存器。

- I格式指令(除了 lw、sw 和分支指令):与R格式类似,但还包括从指令中提取立即数并进行符号扩展,然后与rs1的内容相加,结果写入由rt指定的寄存器。

通过这种方式,每个时钟周期可以执行一条指令,实现了单周期处理器的设计目标。在实际的处理器设计中,还需要考虑控制逻辑、异常处理、中断管理等复杂情况,以确保系统的稳定性和可靠性。此外,流水线设计还需要解决数据相关和控制相关等问题,以避免流水线的阻塞和性能损失。

2021-04-05 上传

2022-06-20 上传

2023-03-31 上传

2023-06-02 上传

2023-06-02 上传

2023-05-13 上传

2023-06-02 上传

2023-09-03 上传

绿色环保青蛙

- 粉丝: 0

- 资源: 1

最新资源

- 解决Eclipse配置与导入Java工程常见问题

- 真空发生器:工作原理与抽吸性能分析

- 爱立信RBS6201开站流程详解

- 电脑开机声音解析:故障诊断指南

- JAVA实现贪吃蛇游戏

- 模糊神经网络实现与自学习能力探索

- PID型模糊神经网络控制器设计与学习算法

- 模糊神经网络在自适应PID控制器中的应用

- C++实现的学生成绩管理系统设计

- 802.1D STP 实现与优化:二层交换机中的生成树协议

- 解决Windows无法完成SD卡格式化的九种方法

- 软件测试方法:Beta与Alpha测试详解

- 软件测试周期详解:从需求分析到维护测试

- CMMI模型详解:软件企业能力提升的关键

- 移动Web开发框架选择:jQueryMobile、jQTouch、SenchaTouch对比

- Java程序设计试题与复习指南